# Investors' Guide

2026年2月13日

東京エレクトロン株式会社

IR室

# 内容

|                              |     |

|------------------------------|-----|

| 1. 会社概要                      | 3   |

| 2. 半導体および半導体製造装置市場の見通し       | 17  |

| 3. 企業理念体系と中期経営計画             | 27  |

| 4. 事業環境と業績予想                 | 35  |

| 5. サステナビリティ                  | 45  |

| 6. 多様化する半導体技術、～技術ロードマップ～     | 57  |

| 7. 新規装置事業の取り組み               | 63  |

| 7-1 前工程 パターニング               | 67  |

| 7-2 前工程 ユニットプロセス             | 75  |

| 7-2-1 エッチング装置                | 76  |

| 7-2-2 成膜装置                   | 85  |

| 7-2-3 洗浄装置                   | 92  |

| 7-3 後工程事業戦略                  | 99  |

| 8. MAGIC市場とフィールドソリューションの取り組み | 116 |

| 9. デジタルトランスフォーメーション（DX）の取り組み | 123 |

| 10. 調達・生産戦略                  | 133 |

| Appendix : データセクション          | 143 |

# 1. 会社概要

# 会社概要

設立

1963年(昭和38年)11月11日

主要事業

半導体製造装置事業

資本金

549億6,119万円

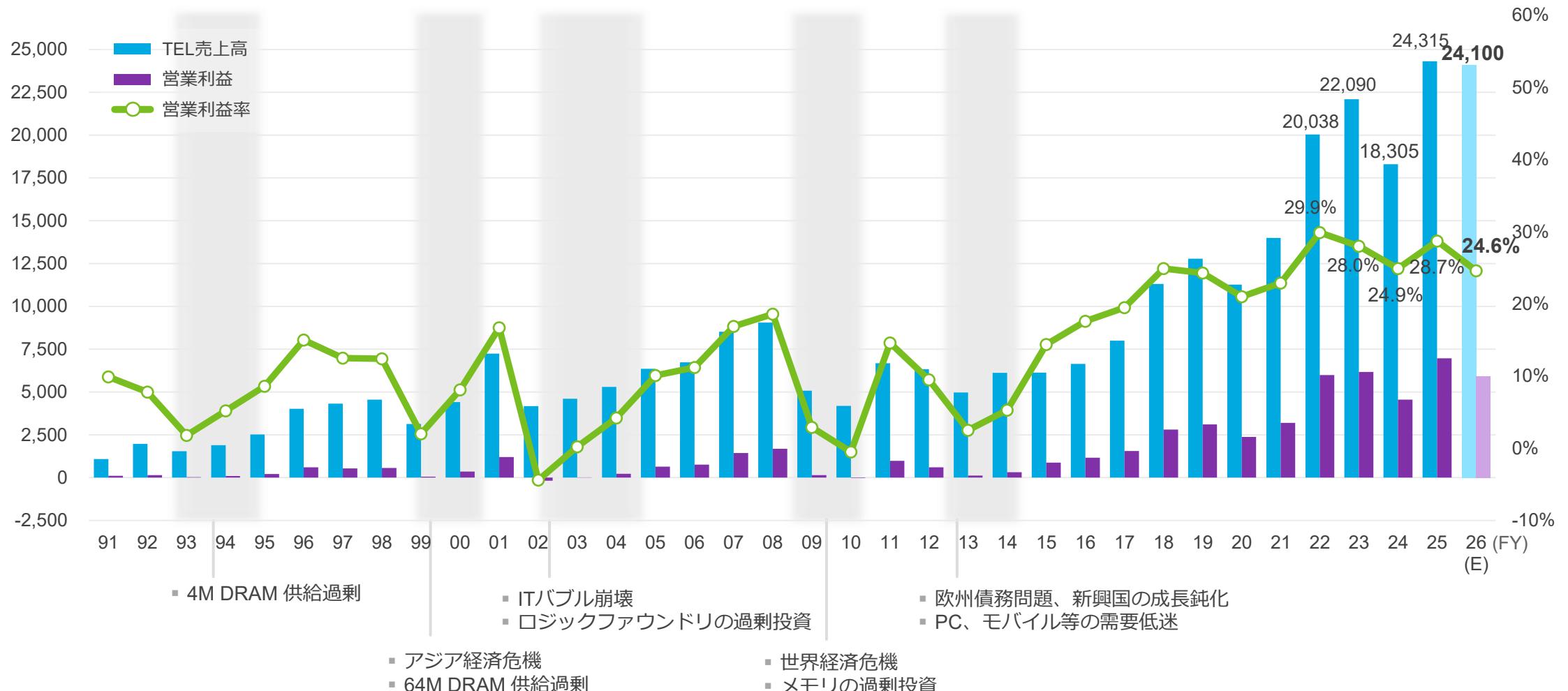

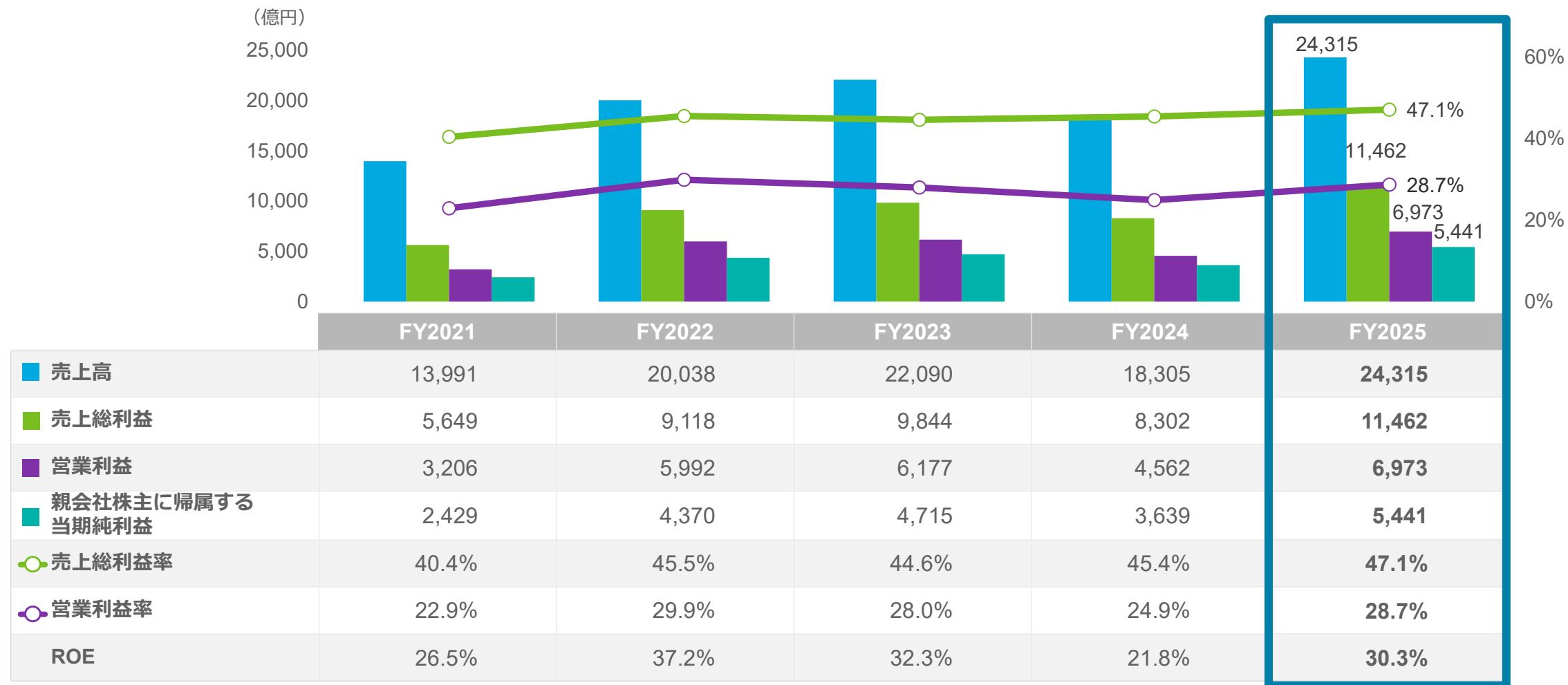

売上/利益

売上高 2兆4,315億円／営業利益 6,973億円／営業利益率 28.7% (2025年3月期)

従業員数

2,347人(単独) 20,273人(連結)

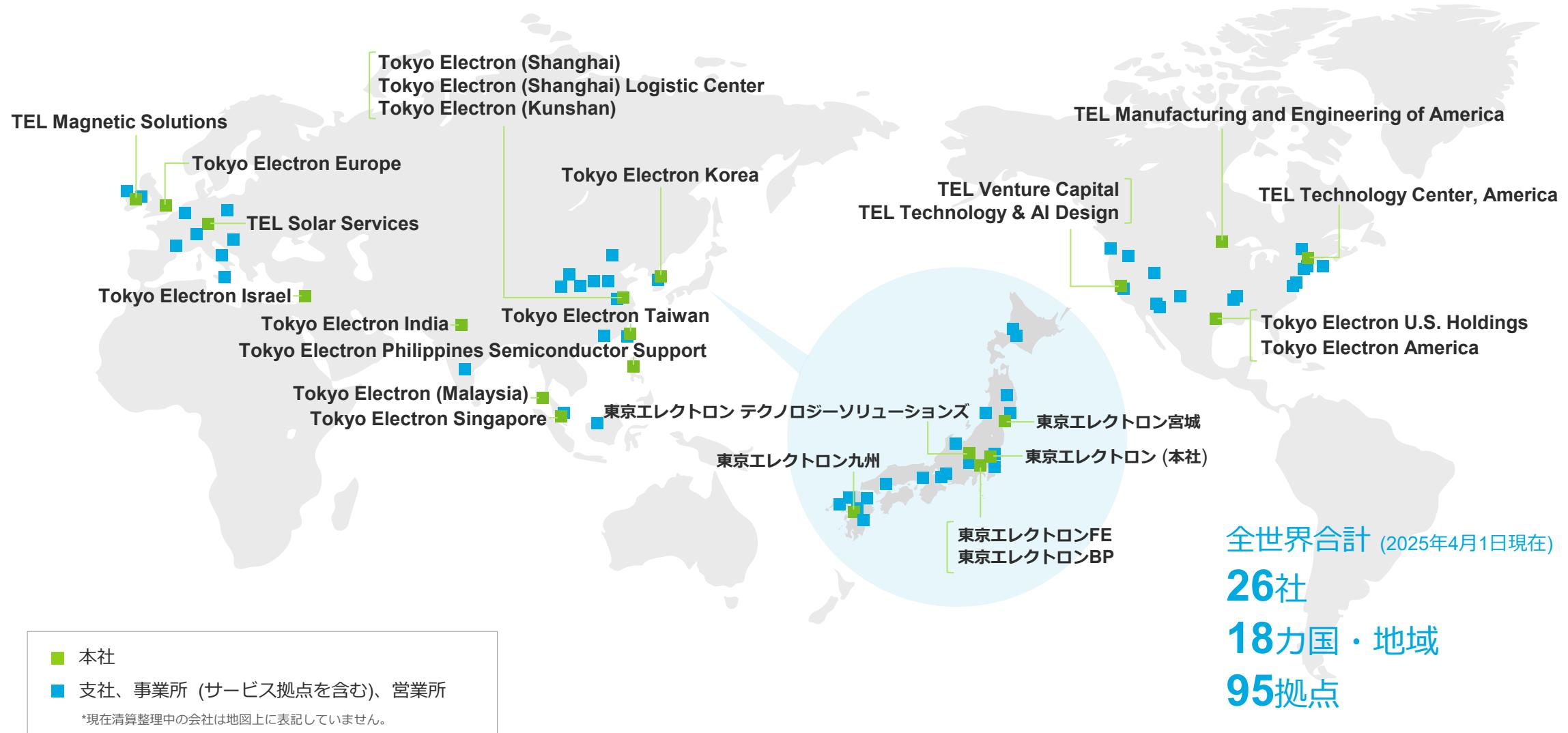

拠点数

国内 6社・30拠点

海外 20社・17の国と地域・65拠点

合計 26社・18の国と地域・95拠点(連結)

(2025年4月1日現在)

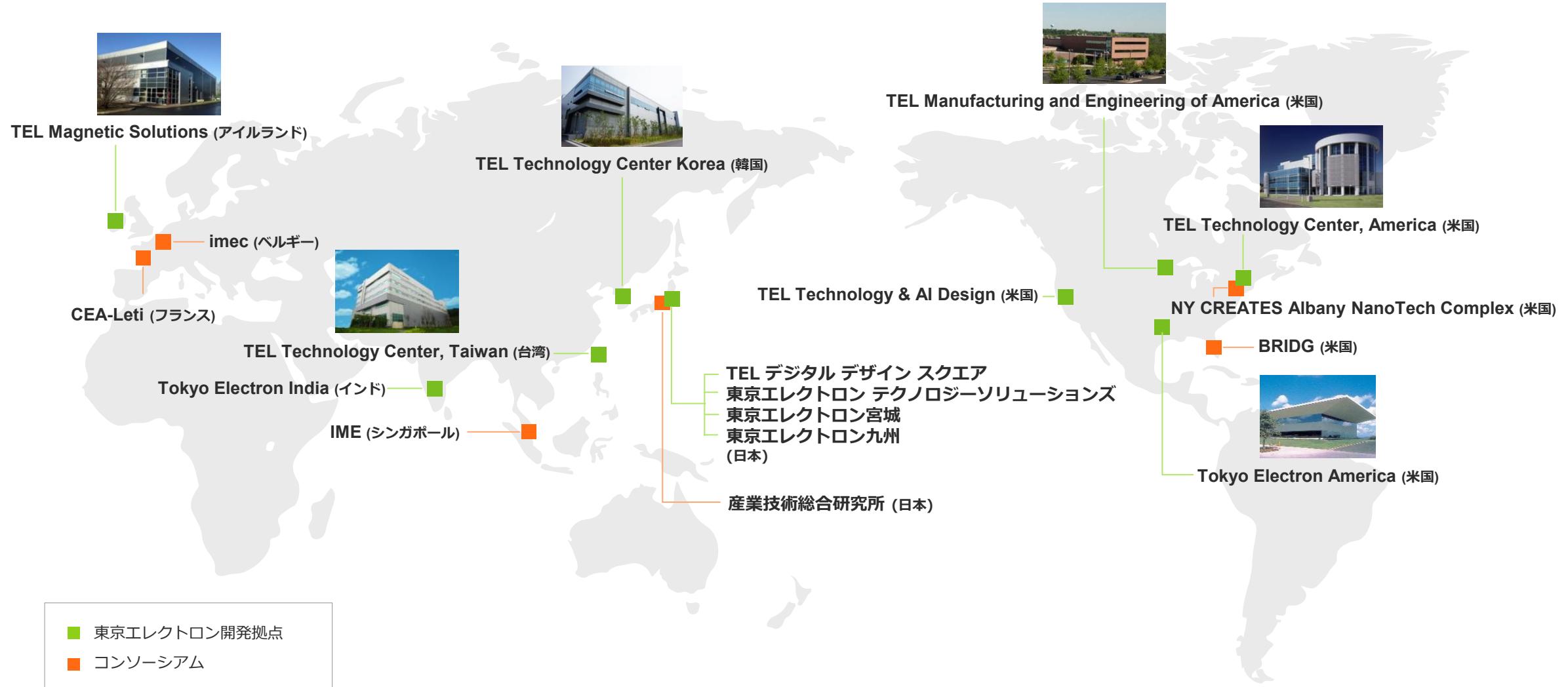

# 世界主要拠点

(2026年2月1日現在)

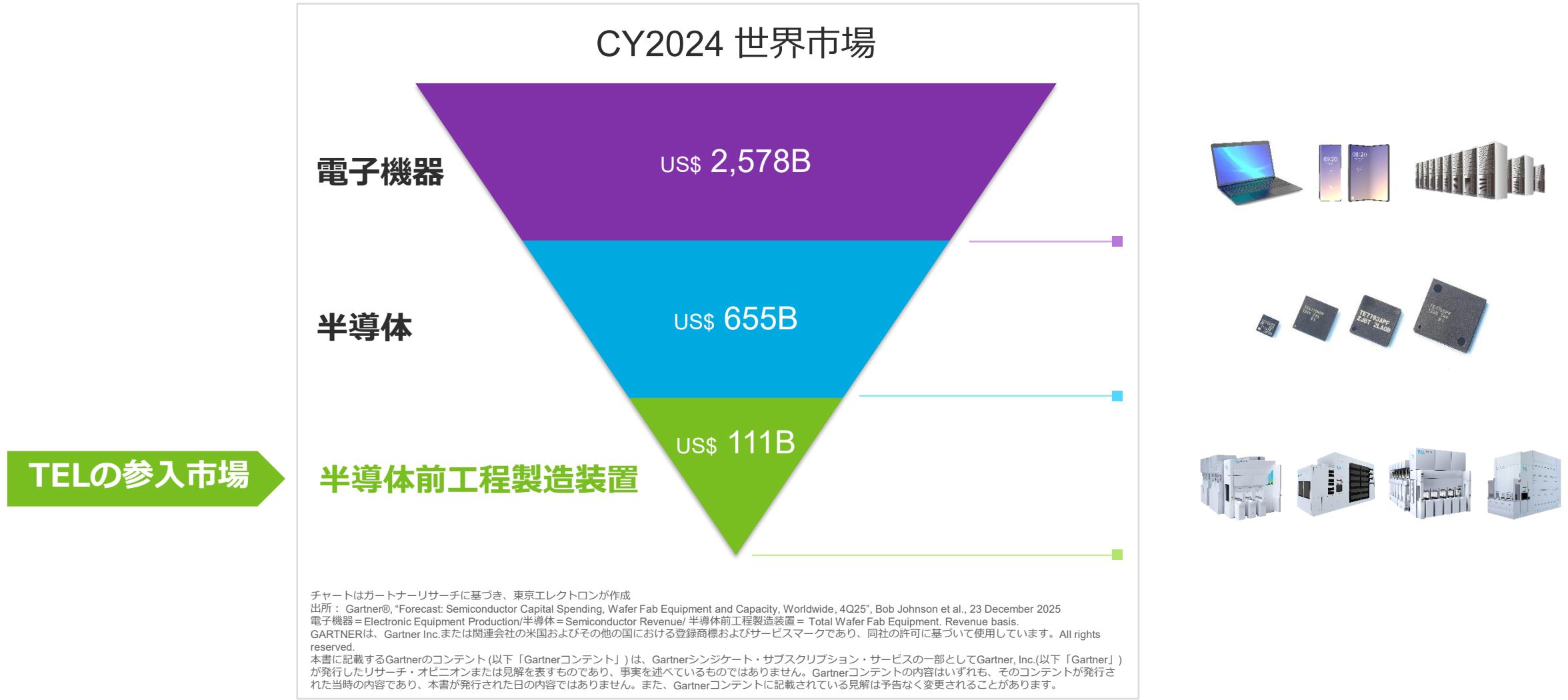

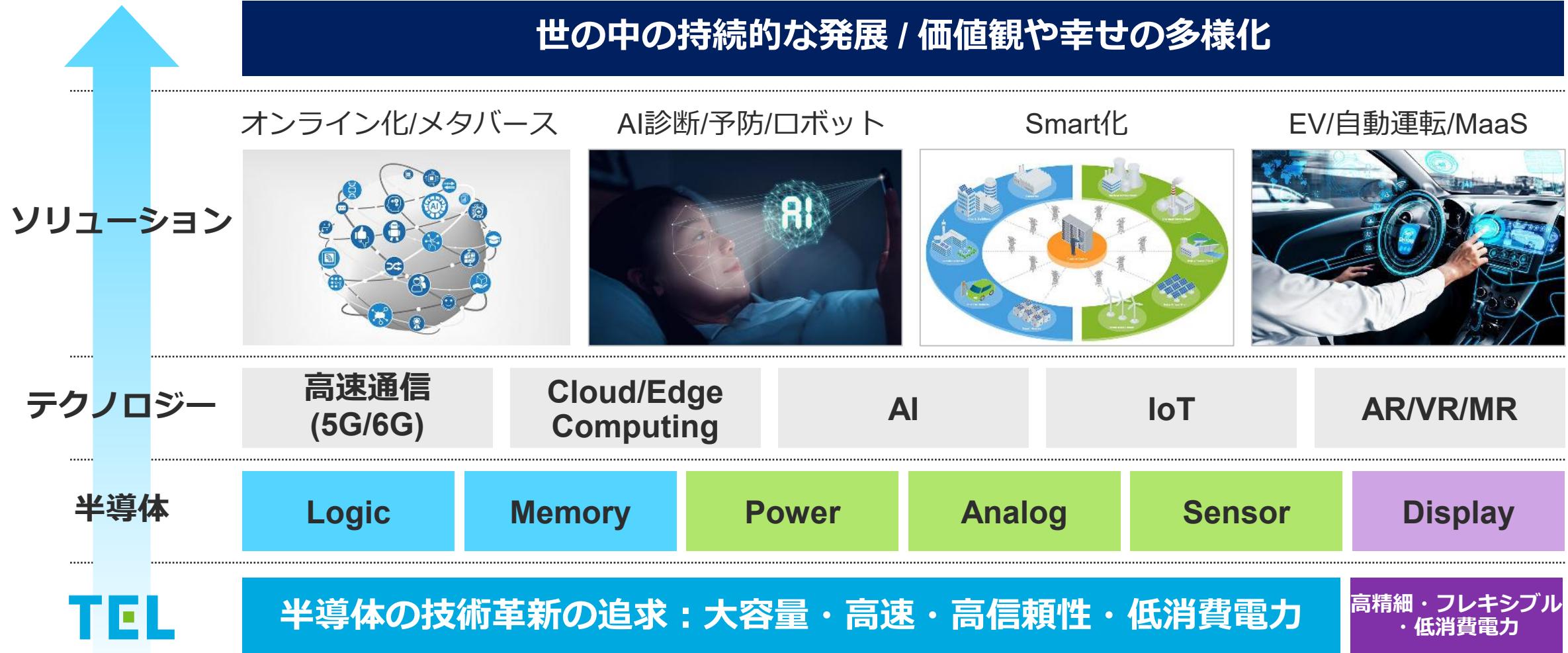

# 電子機器関連産業 市場構造

# TELの成長の軌跡

# 売上高と営業利益の推移

(億円)

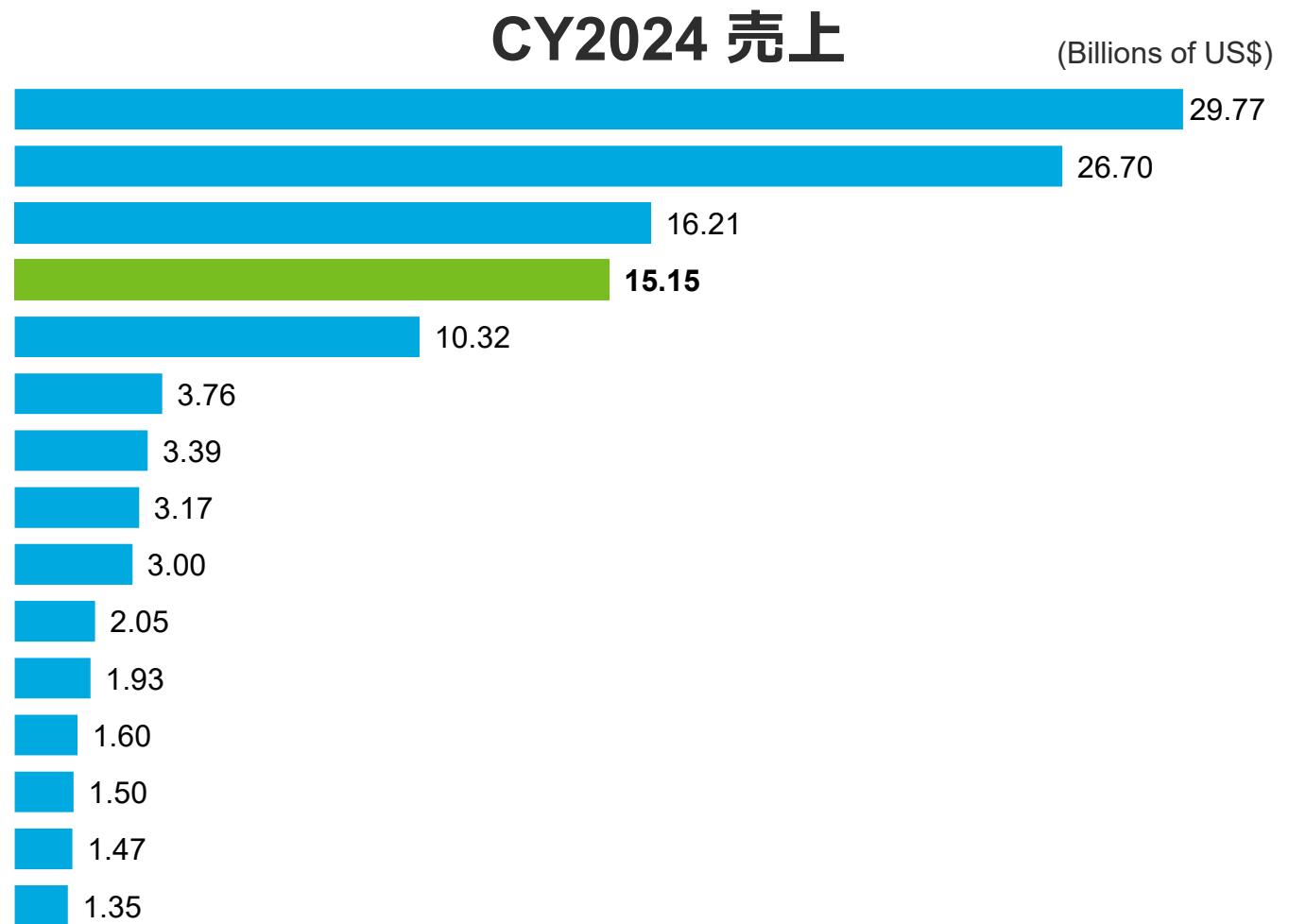

# CY2024 半導体製造装置メーカー トップ15

|  |                     |

|--|---------------------|

|  | 1 ASML              |

|  | 2 Applied Materials |

|  | 3 Lam Research      |

|  | 4 東京エレクトロン          |

|  | 5 KLA               |

|  | 6 アドバンテスト           |

|  | 7 SCREEN            |

|  | 8 ASM International |

|  | 9 NAURA             |

|  | 10 Teradyne         |

|  | 11 ディスコ             |

|  | 12 SEMES            |

|  | 13 日立ハイテク           |

|  | 14 KOKUSAI ELECTRIC |

|  | 15 レーザーテック          |

Source : TechInsights Inc., May 2025

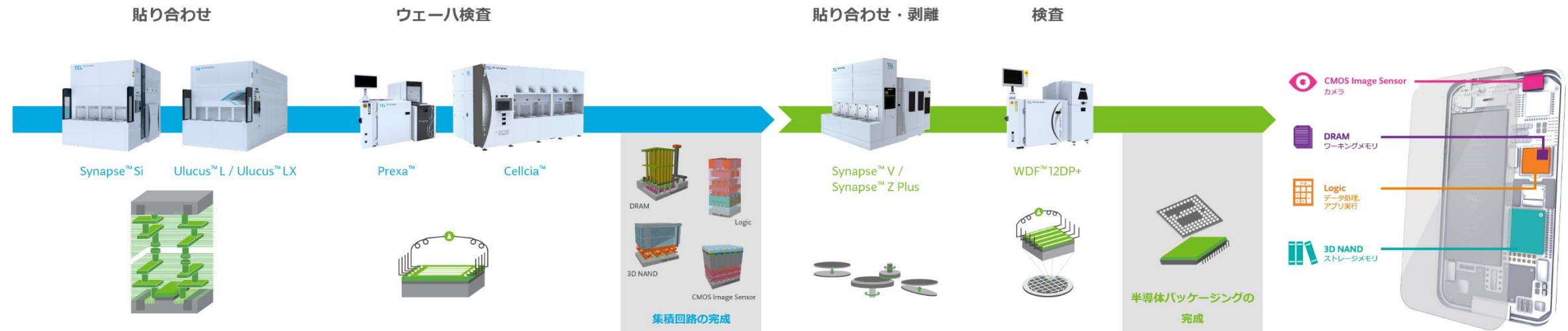

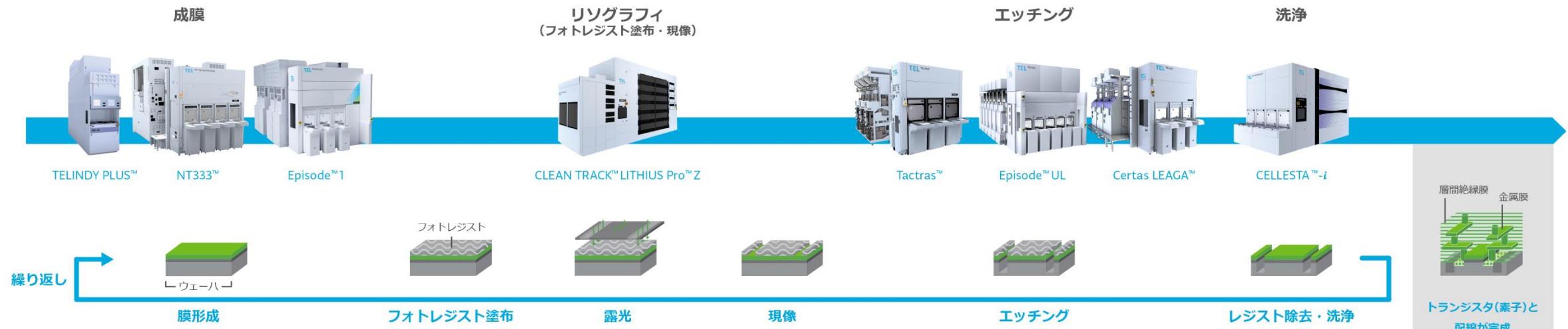

# 半導体製造プロセス

TELCC-SMP-004

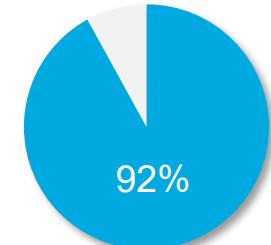

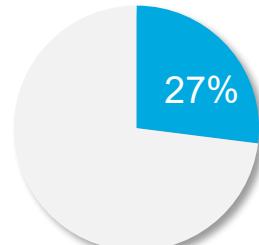

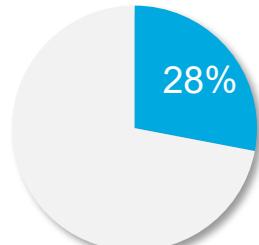

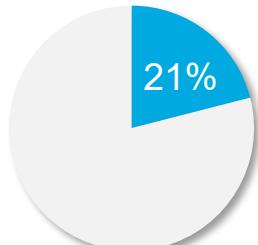

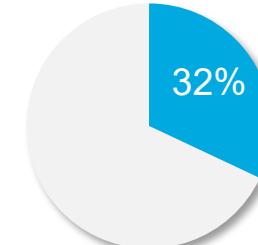

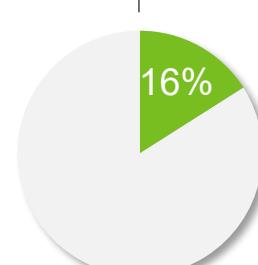

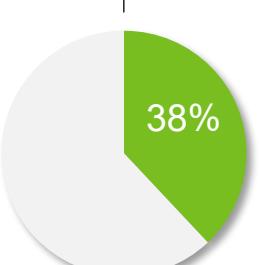

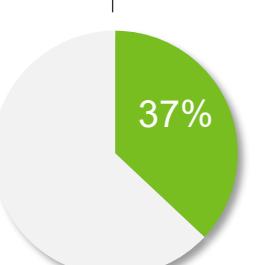

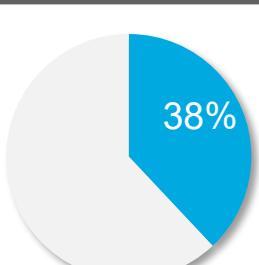

# 主要プロダクト 世界市場シェア (CY2024)

コーティング/デベロッパ

ドライエッチング装置

成膜装置

洗浄装置

ウェーハボンダー

ALD

CVD

酸化/拡散

ウェーハプローバ

## 出所

Gartner®, Market Share: Semiconductor Wafer Fab Equipment, Worldwide, 2024, Bob Johnson and Menglin Cao, 21 April 2025, Revenue from Shipments basis.

チャートはガートナーリサーチに基づき、東京エレクトロンが作成。ここに記載のある数値は、東京エレクトロンにより算出されたものです。

コーティング/デベロッパ: Photoresist Processing (Track), ドライエッチング装置: Dry Etch, 成膜装置: Tube CVD + Atomic Layer Deposition Tools + Oxidation/ Diffusion Furnaces + Nontube LPCVD, ALD: Atomic Layer Deposition Tools,

CVD: Tube CVD + Nontube LPCVD, 酸化/拡散: Oxidation/Diffusion Furnaces, 洗浄装置: Single Wafer Processors + Wet Stations + Batch Spray Processors + Scrubbers + Other Clean Equipment ウェーハボンダー: Wafer Bonder

GARTNERは、Gartner Inc.または関連会社の米国およびその他の国における登録商標およびサービスマークであり、同社の許可に基づいて使用しています。All rights reserved. Gartnerは、Gartnerリサーチの発行物に掲載された特定のベンダー、製品またはサービスを推薦するものではありません。また、最高のレーティング又はその他の評価を得たベンダーのみを選択するようにテクノロジーユーザーに助言するものではありません。Gartnerリサーチの発行物は、Gartnerリサーチの見解を表したものであり、事実を表現したものではありません。Gartnerは、明示または黙示を問わず、本リサーチの商品性や特定目的への適合性を含め、一切の責任を負うものではありません。

本書に記載するGartnerのコンテンツ（以下「Gartnerコンテンツ」）は、Gartnerシンジケート・サブスクリプション・サービスの一部としてGartner, Inc.(以下「Gartner」)が発行したリサーチ・オピニオンまたは見解を表すものであり、事実を述べているものではありません。Gartnerコンテンツの内容はいずれも、そのコンテンツが発行された当時の内容であり、本書が発行された日の内容ではありません。また、Gartnerコンテンツに記載されている見解は予告なく変更されることがあります。

## 出所

半導体製造装置（ウェーハプローバ）: Auto Probers,: TechInsights Inc., April 2025

図はTechInsights Inc.に基づき、東京エレクトロンが作成。

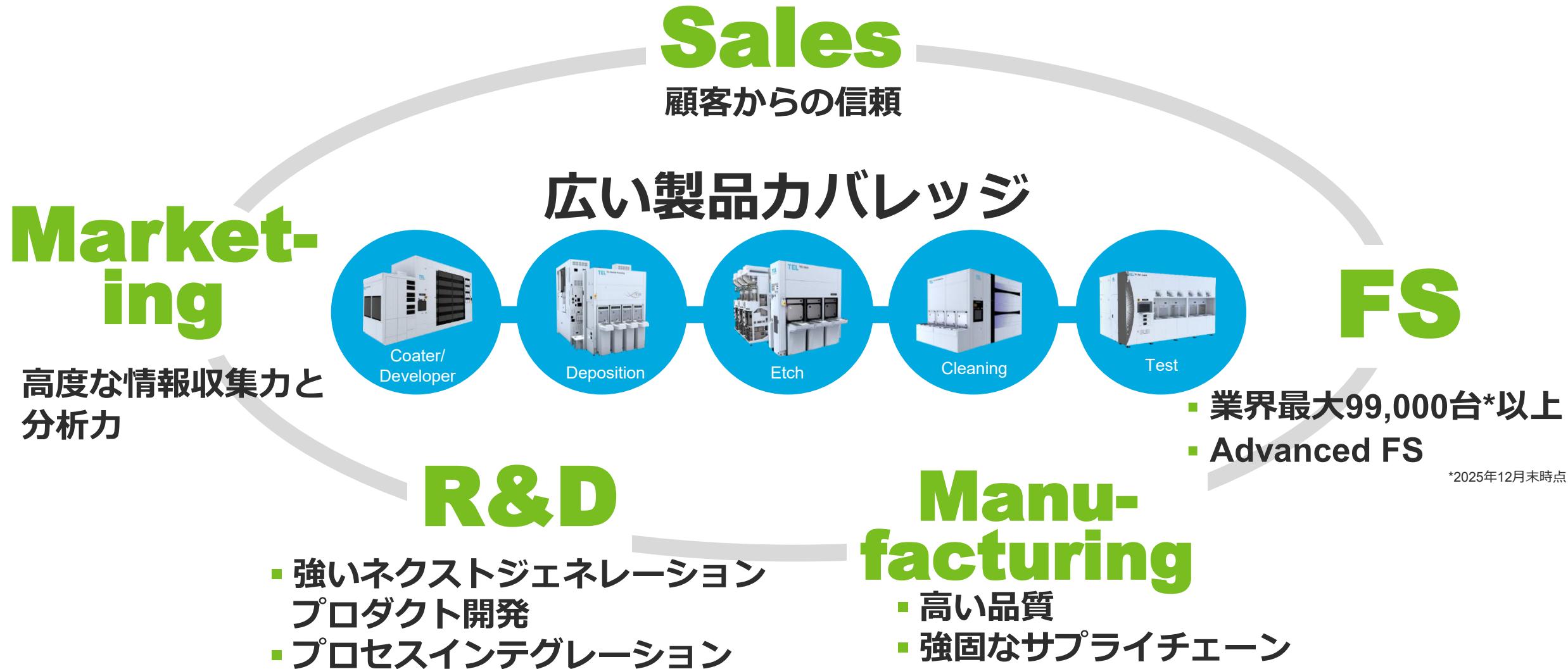

# TELの強み

4つのキープロセスに先端装置をもつ

## No.1/No.2

シェア世界1・2位の製品群

主要製品と世界シェア\*

1位 2位 2位 1位 1位 1位 2位 1位 2位

\*当社推定

# 100%

EUV露光用

塗布/現像装置シェア

\*当社推定

# No.1

世界装置出荷台数

年間装置出荷台数

約4,000～6,000台<sup>\*1</sup>

世界装置出荷台数 業界最大の

# 99,000台<sup>\*2</sup>

\*<sup>1</sup> 2025年3月末時点

\*<sup>2</sup> 2025年12月末時点

# グローバル開発拠点

(2026年2月1日現在)

# 開発体制のさらなる強化

## 山梨開発棟

成膜、ガスケミカルエッチ、コーポレート開発

(2023年7月 竣工)

## 宮城開発棟

エッティング装置

(2025年4月 竣工)

## 熊本開発棟

コーティング装置、洗浄装置、ボンディング装置

(2025年10月 竣工)

## 宮城技術革新センター

エッティング装置

(2021年9月 竣工)

## TEL デジタル デザイン スクエア

DX、ソフトウェア開発

(2020年11月 開設)

# Best Products、Best Serviceの継続的追求のために

## Front-loading

## Advanced field solutions

- 顧客との複数世代にわたる技術ロードマップ共有

- Early engagementの推進

- 量産初期より顧客製品デバイスの歩留まりと装置稼動率の最大化を実現、また環境負荷も低減

- 仕事の効率化と1人当たりの生産性向上を推進し、人材・開発への投資をさらに増加

- 業界最大の出荷済装置**99,000台\***を生かしたビジネス展開

- 遠隔保守 TELeMetrics™

- Machine learningによる予知保全

\*2025年12月末時点

TELの総合力を最大限に生かす

## 2. 半導体および半導体製造装置市場の見通し

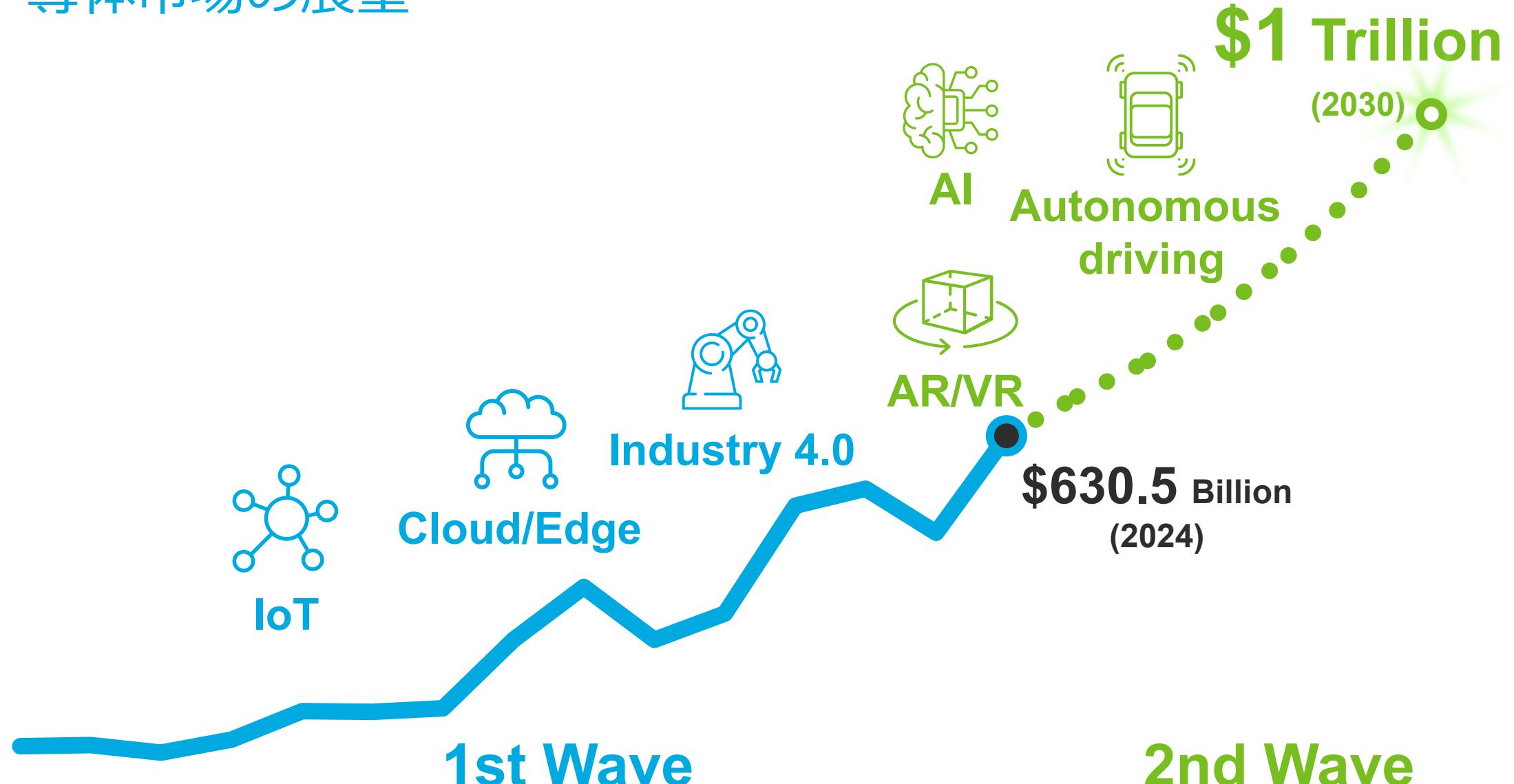

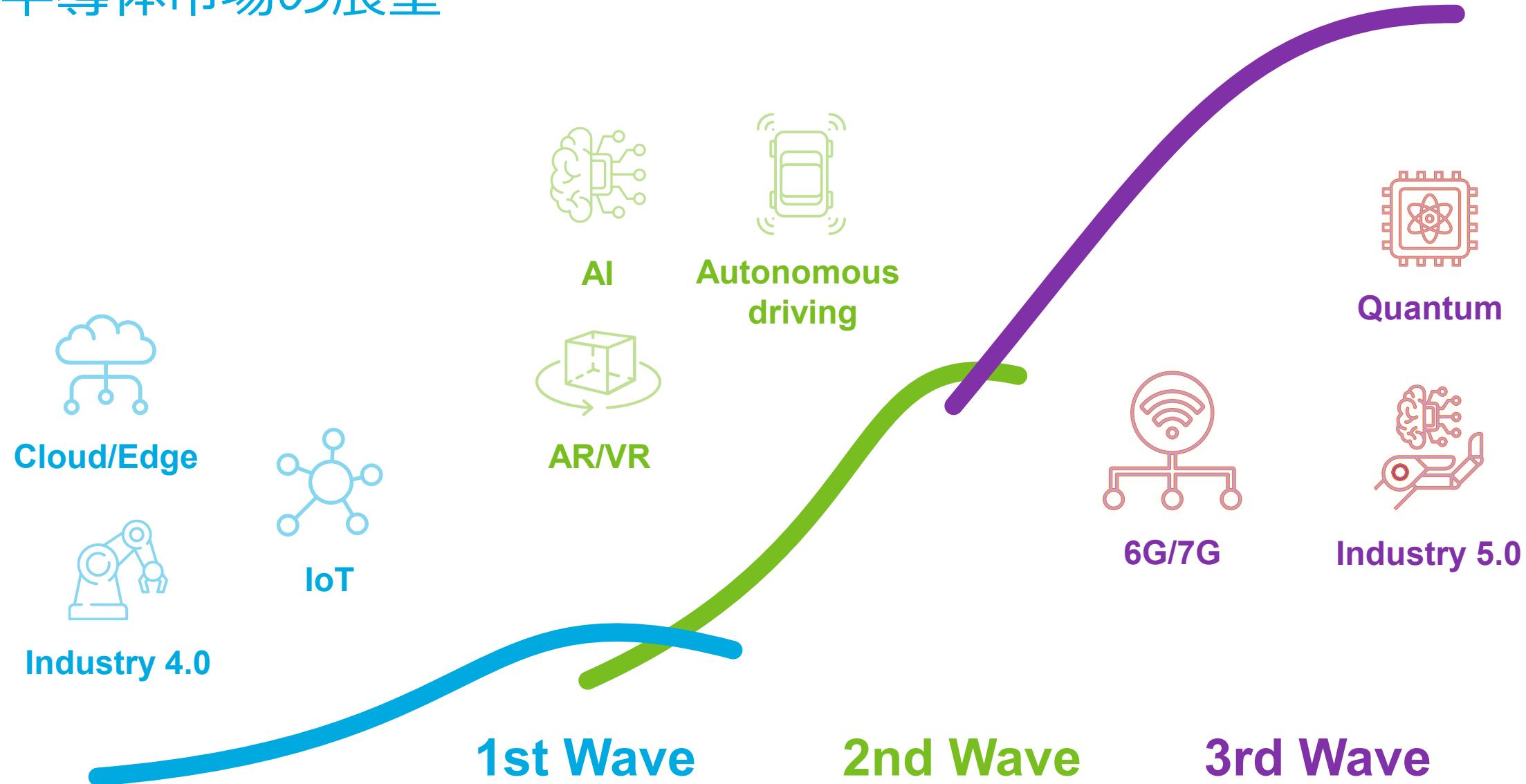

# 半導体市場の展望

# 半導体市場の展望

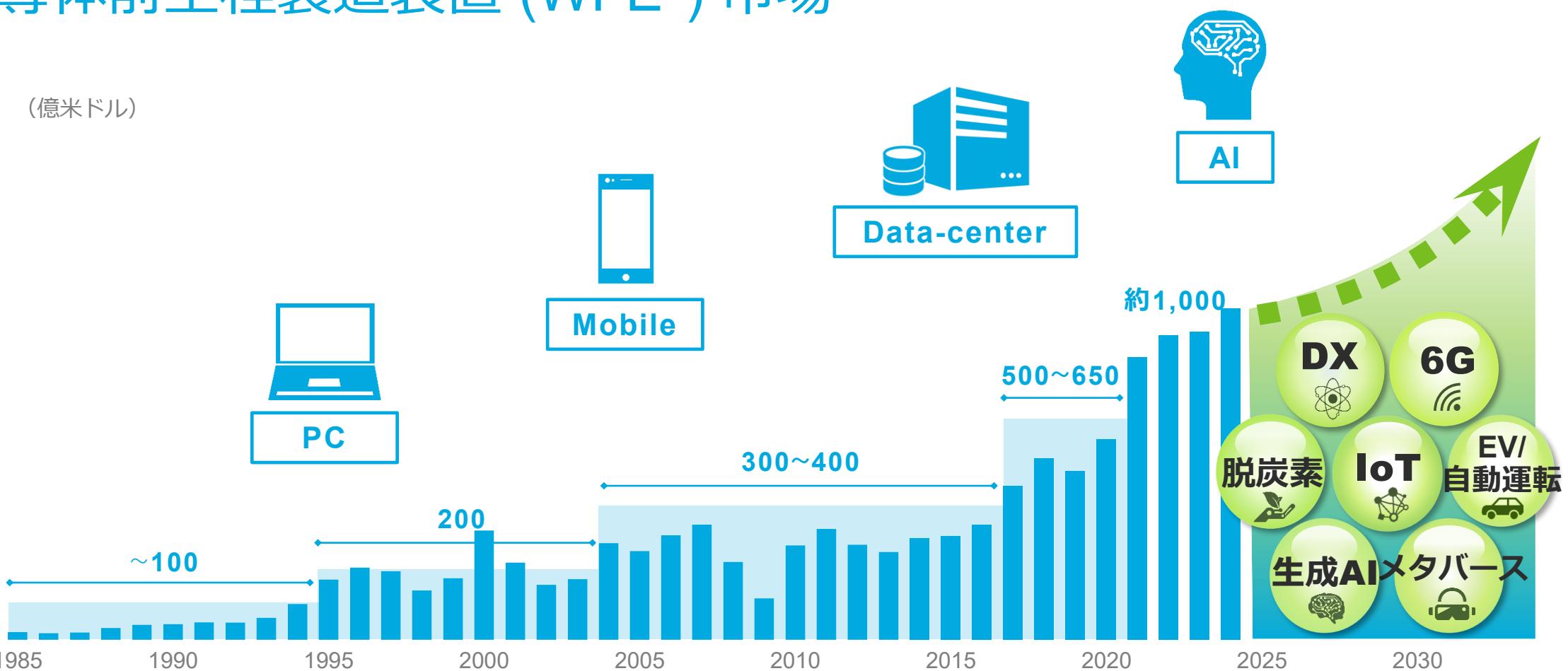

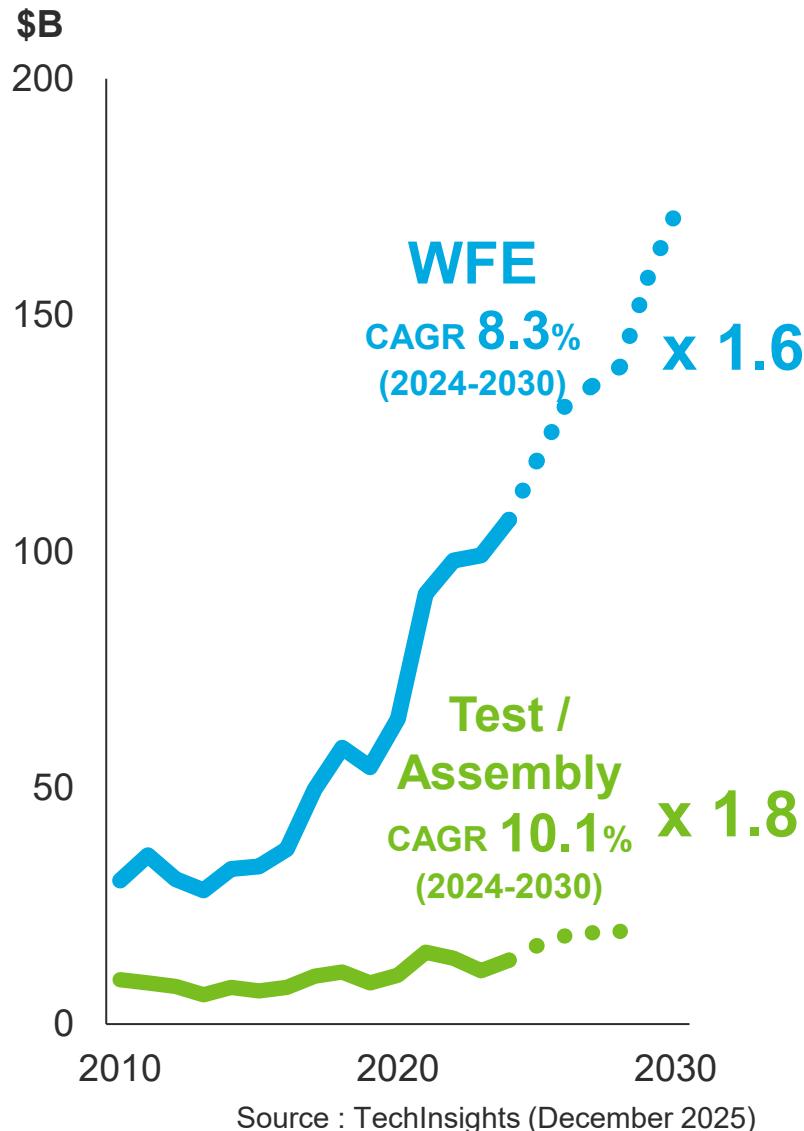

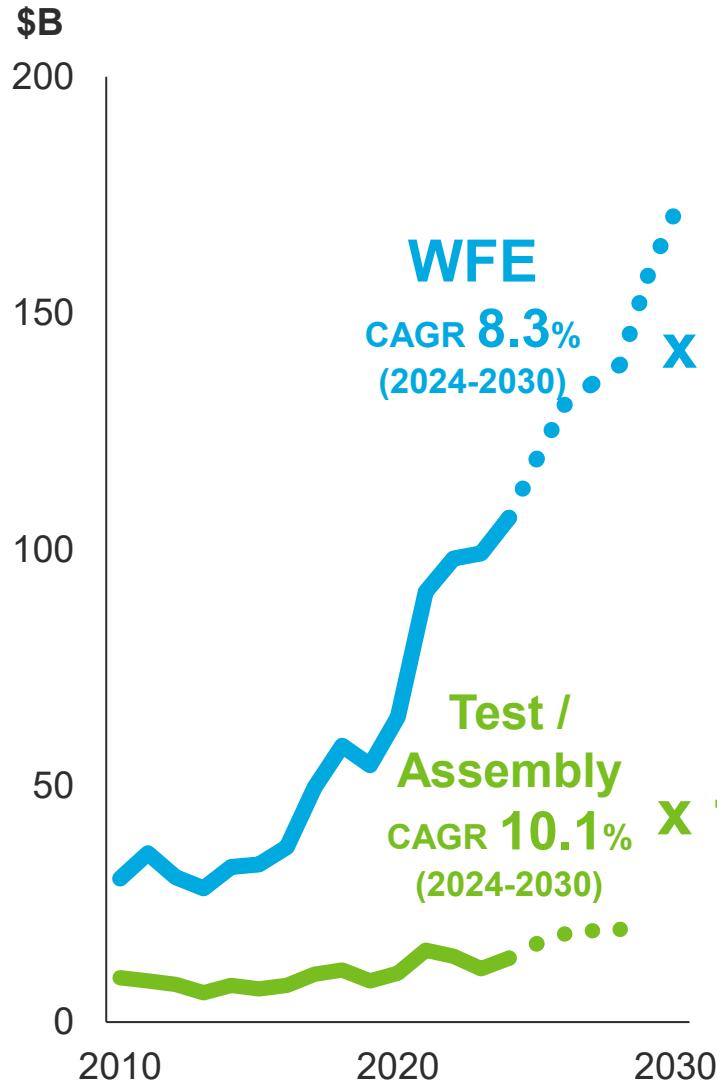

# 半導体前工程製造装置 (WFE\*) 市場

デジタル化の一層の進展とさらなる半導体の進化で

製造装置市場は一段と成長

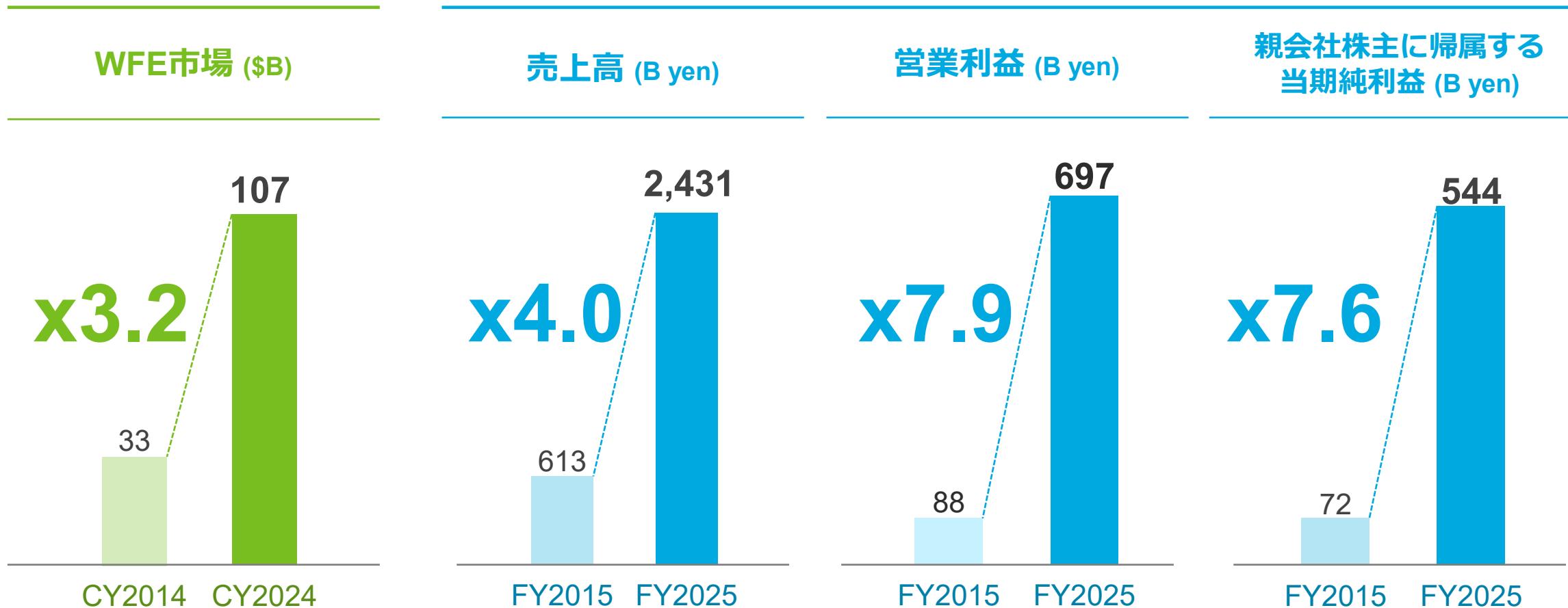

# 市場成長と業績成長 (FY2025 vs. FY2015)

市場成長を大きくアウトパフォーム

Source : TechInsights Inc.

Investor Relations / February 13, 2026

TEL

21

# Green Future Through Semiconductor Evolution

## Digital & Green

Higher Speed

Larger Capacity

Superior Reliability

Lower Power Consumption

Physical Scaling

Heterogeneous Integration

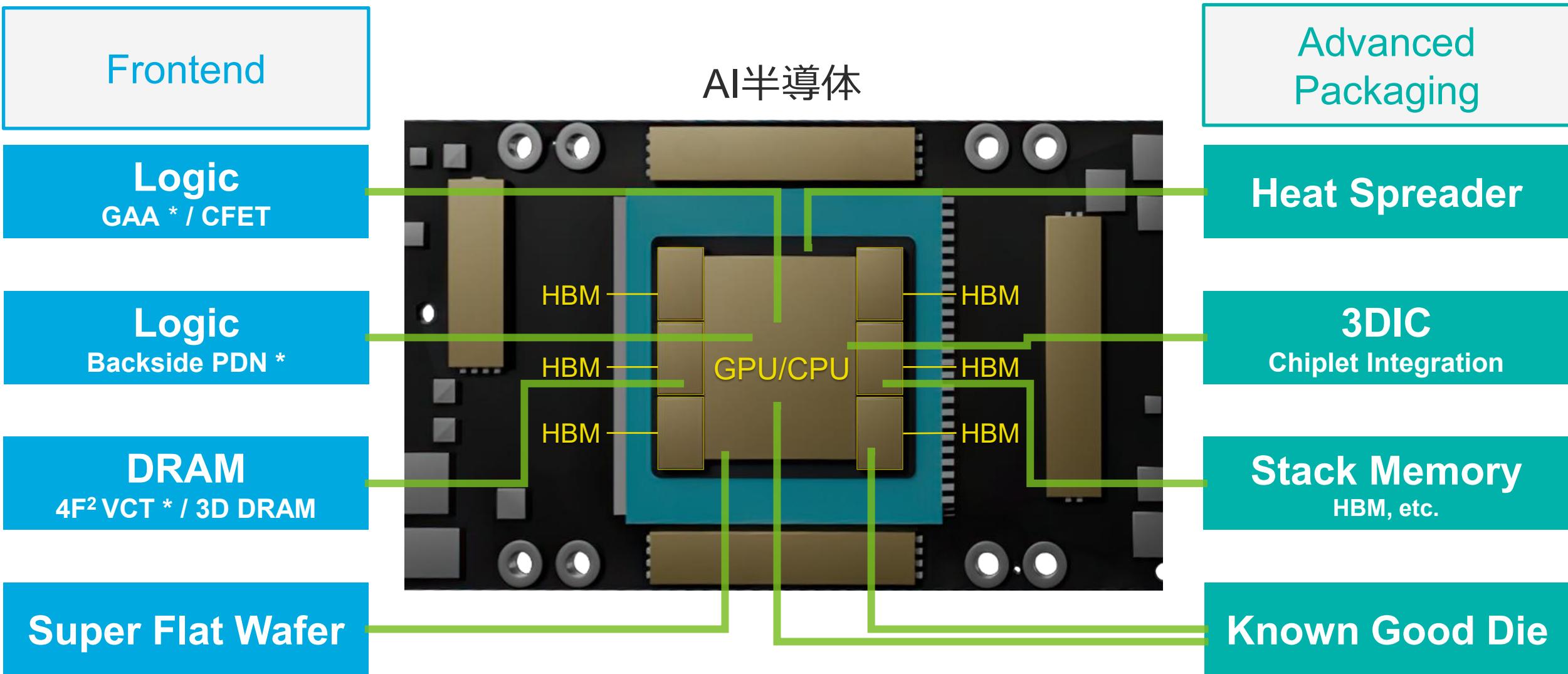

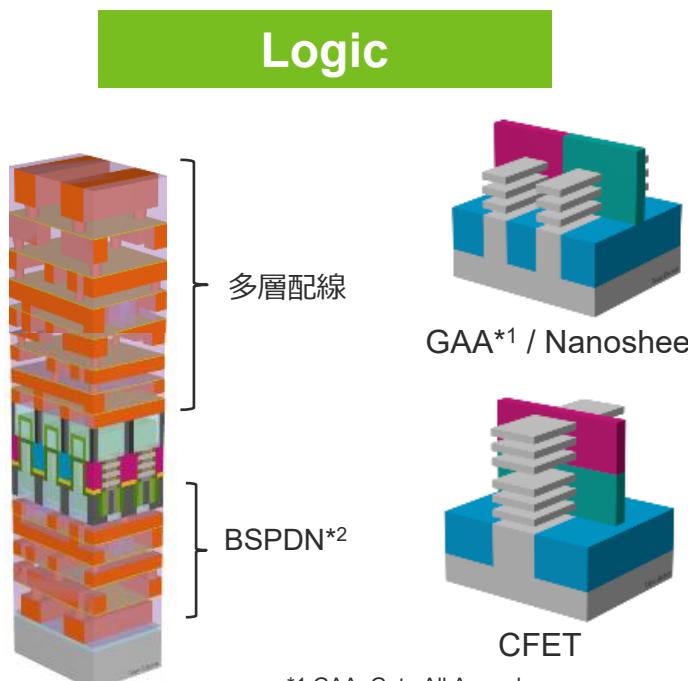

# Physical Scaling x Heterogeneous Integration

\* GAA : Gate All Around

\* Backside PDN : Backside Power Delivery Network

\* VCT : Vertical Channel Transistor

# 拡大する事業機会：豊富な製品ラインアップ

Frontend

Advanced Packaging

Deposition

Batch Deposition    Semi-batch Deposition    Single Deposition

Lithography

Coater/

Developer

Etch

Gas Chemical Etch

Cleaning

Cleaning

Cleaning

Testing

Prober

Bonding /

Debonding

Wafer Bonder/

Debonder

Wafer Edge

Trimming/

XLO\*

\*XLO: Extreme Laser Lift Off

# 今後の成長を見据えた注力技術

| Frontend                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Logic : GAA, BSPDN</b>                                                                                                                                                                                                                                                                                                                                             | <b>DRAM: 2D &amp; 3D DRAM</b>                                                                                                                                                                                                                                                                         | <b>NAND: Beyond 4xx</b>                                                                                                                                                                                                |

| <ul style="list-style-type: none"> <li>▪ EUV Coater/Developer</li> <li>▪ Gas Chemical Etch</li> <li>▪ Conductor Etch</li> <li>▪ PVD Metal Overburden</li> <li>▪ CFET/Inner Spacer Plasma CVD for filling film</li> <li>▪ Double-sided scrubber</li> <li>▪ Backside/bevel cleaning</li> <li>▪ Pattern Shaping</li> <li>▪ Wafer Bonder</li> <li>▪ Laser Tool</li> </ul> | <ul style="list-style-type: none"> <li>▪ EUV Coater/Developer</li> <li>▪ Capacitor Mold Etch</li> <li>▪ Batch High-k Capacitor deposition</li> <li>▪ PVD Metal Hardmask</li> <li>▪ Supercritical Cleaning</li> <li>▪ Backside/bevel Cleaning</li> <li>▪ Wafer Bonder</li> <li>▪ Laser Tool</li> </ul> | <ul style="list-style-type: none"> <li>▪ Slit Etch</li> <li>▪ Channel Hole Etch (Plug)</li> <li>▪ Batch Mo deposition</li> <li>▪ Batch Cleaning WL Separation</li> <li>▪ Wafer Bonder</li> <li>▪ Laser Tool</li> </ul> |

| Advanced Packaging                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                        |

| <b>Logic Packaging</b>                                                                                                                                                                                                                                                                                                                                                | <b>HBM Packaging</b>                                                                                                                                                                                                                                                                                  | <b>Advanced Logic / Memory Test</b>                                                                                                                                                                                    |

| <ul style="list-style-type: none"> <li>▪ Interposer, Polyimide &amp; PR Coater/Developer</li> <li>▪ TDV Etch</li> <li>▪ Batch High-k Capacitor depo</li> <li>▪ Wafer Bonder</li> <li>▪ Laser Tool</li> </ul>                                                                                                                                                          | <ul style="list-style-type: none"> <li>▪ Polyimide &amp; PR Coater/Developer</li> <li>▪ Metal Etch for HBM</li> <li>▪ Aerosol Cleaning</li> <li>▪ Temporary Bonder/Debonder</li> </ul>                                                                                                                | <ul style="list-style-type: none"> <li>▪ Prober</li> </ul>                                                                                                                                                             |

# 拡大するTELの事業機会

# 微細化×異種デバイス集積

Etch

>5,000億円

Bonder

Laser

>5,000億円

Prober

CAGR

>15%

Die Prober

PECVD

SAM

+10%

- DRAM配線工程エッチング装置：

特に配線層数の多いHBM向け投資増加により事業機会が拡大。

2030年までに累計5,000億円以上の売上を見込む

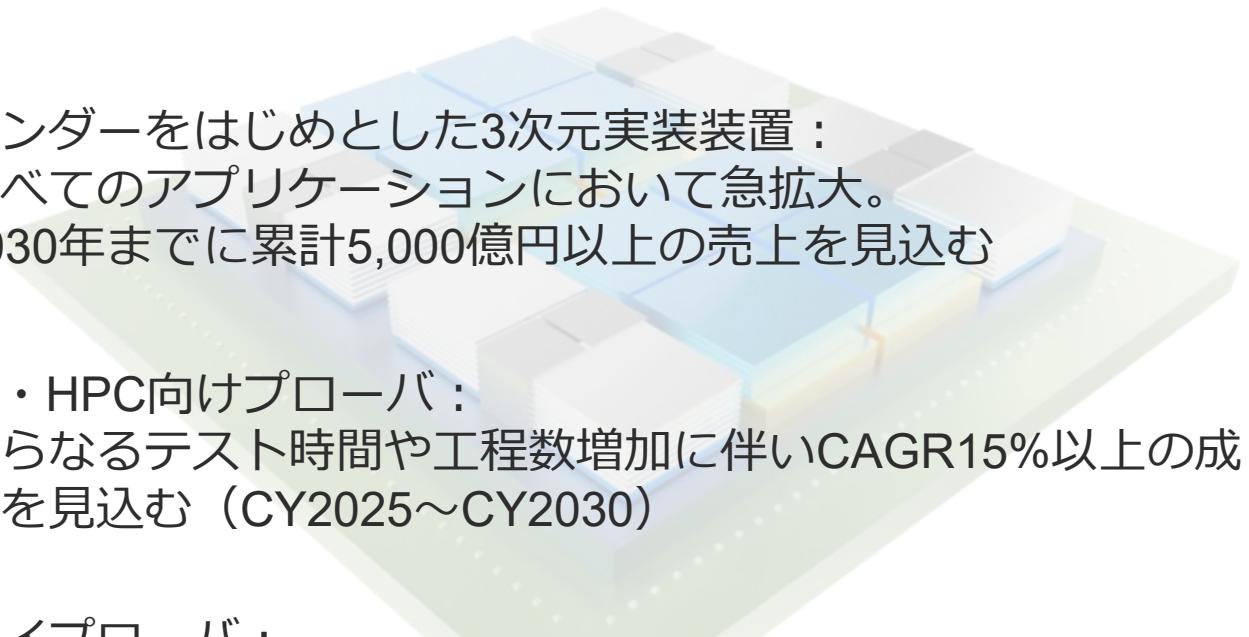

- ボンダーをはじめとした3次元実装装置：

すべてのアプリケーションにおいて急拡大。

2030年までに累計5,000億円以上の売上を見込む

- AI・HPC向けプローバ：

さらなるテスト時間や工程数増加に伴いCAGR15%以上の成長を見込む (CY2025～CY2030)

- ダイプローバ：

顧客との開発評価合意。プローバ市場の10～15%のSAM創出

- 埋め込み膜用 枚葉プラズマCVD：

PECVD市場の約10%。複数顧客にて評価進捗中

### 3. 企業理念体系と中期経営計画

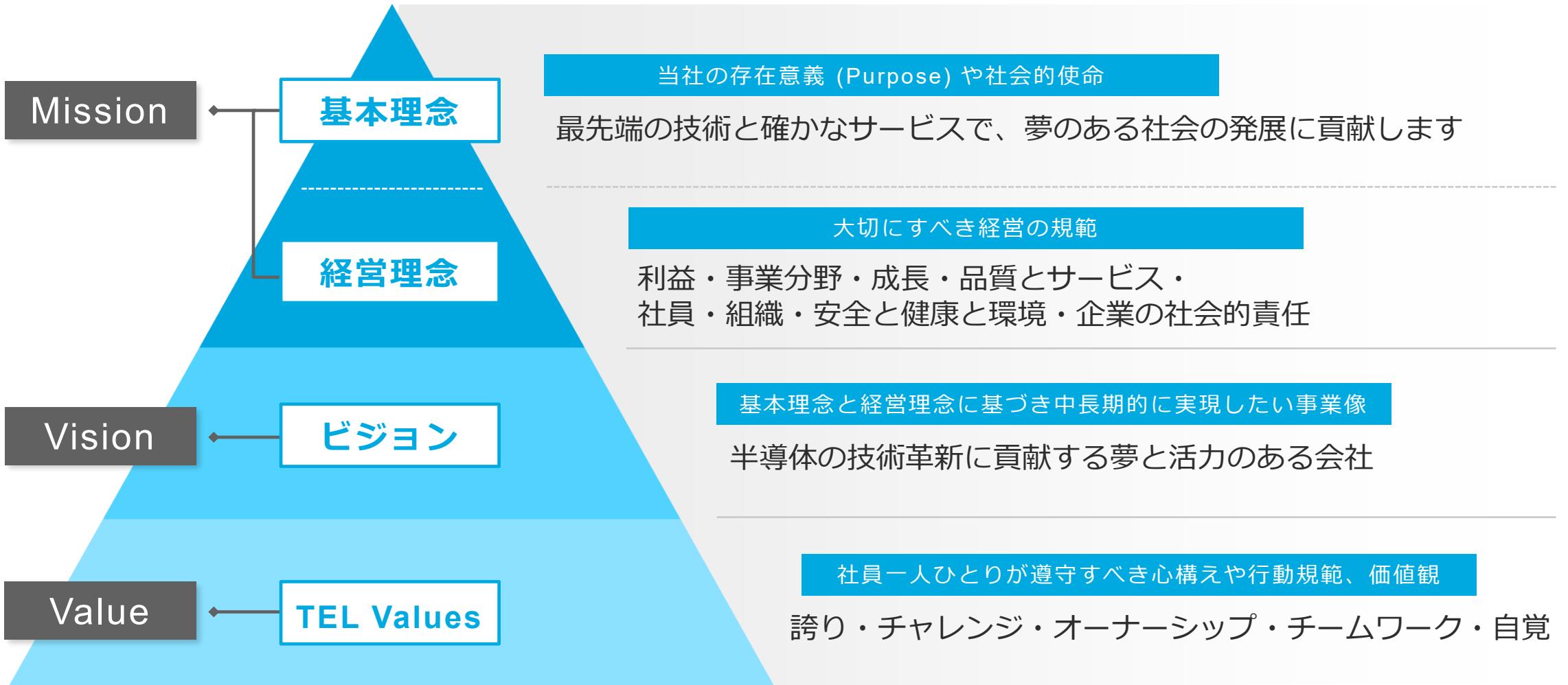

# 企業理念体系

# ビジョン

## 半導体の技術革新に貢献する夢と活力のある会社

東京エレクトロンは、世の中の持続的な発展を支える半導体の技術革新を追求します。

当社の専門性を生かし、付加価値の高い最先端の装置と技術サービスを継続的に創出することで、中長期的な利益の拡大と継続的な企業価値の向上を目指していきます。

そして、企業の成長は人、社員は価値創出の源泉と位置づけ、ステークホルダーとのエンゲージメントを通じて、このビジョンの実現に向けて活動してまいります。

# Technology Enabling Life

Technology Enabling Lifeは

企業理念(基本理念、経営理念、ビジョン、TEL Values)を

表現したコーポレートメッセージです。

**CSV**

(Creating Shared Value : 共有価値の創造)

企業の専門性を活用して社会課題を解決する

ことで社会的価値と経済的価値を創出

それにより企業価値の向上と持続的な成長を

実現するという考え方

- ・世の中の持続的な発展を支える半導体の技術革新を追求

- ・付加価値の高い最先端の装置と技術サービスを継続的に創出

- ・中長期的な利益の拡大と継続的な企業価値の向上

- ・ステークホルダーとのエンゲージメント

### ビジョンの実現 = TELにおける共有価値の創造

# 社会課題に対する当社のアプローチ

# ビジョンと中期経営計画のつながり

FY2023

FY2027

FY2031 (CY2030)

## ■ 2030年に向けた目標

- ・世の中の持続的な発展を支える

① 半導体市場を技術革新により牽引 / ② 持続可能な地球環境に貢献

- ・中長期的な利益の拡大と継続的な企業価値の向上

- ・ステークホルダーとのエンゲージメント

## ■ 中期経営計画 (FY2023~2027)

- ・財務目標の達成

(2030年を見据えた5年間の目標)

## “ビジョンの実現”

半導体の技術革新に貢献する

夢と活力のある会社

2030年でのビジョンの実現を視野に

FY2027までに中期経営計画の達成を目指す

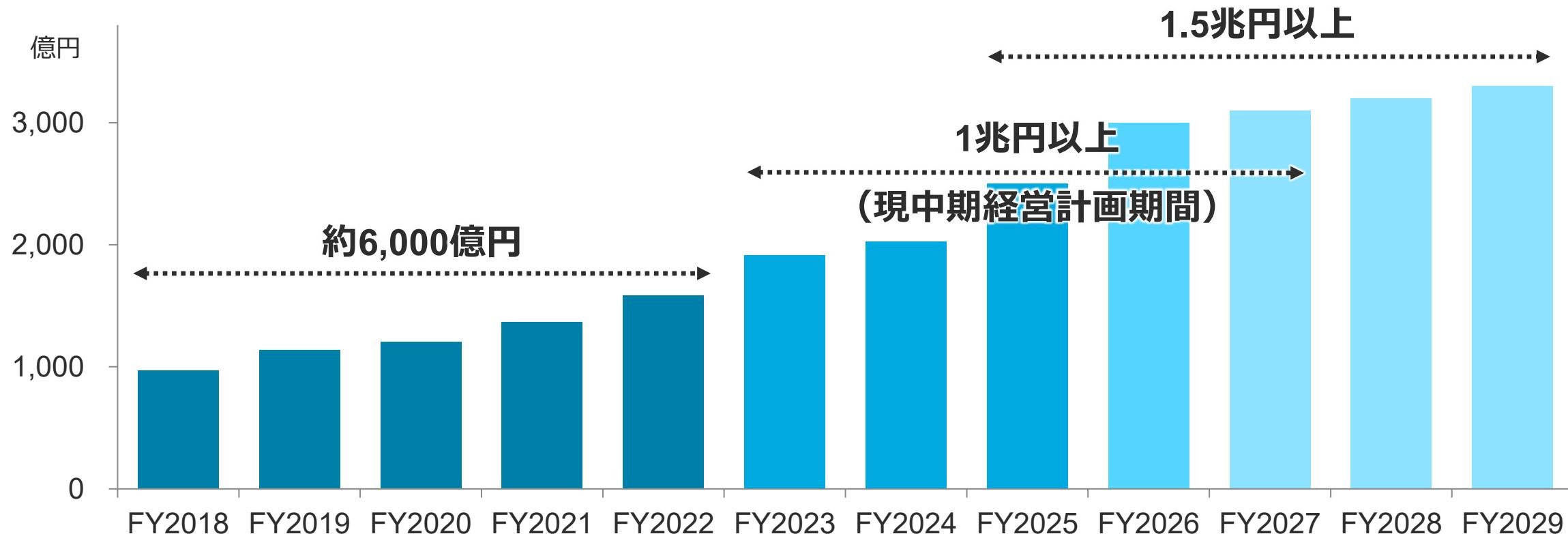

# 中期経営計画 財務目標

| 財務目標 (FY2023~FY2027) |       |

|----------------------|-------|

| 売上高                  | ≥ 3兆円 |

| 営業利益率                | ≥ 35% |

| ROE                  | ≥ 30% |

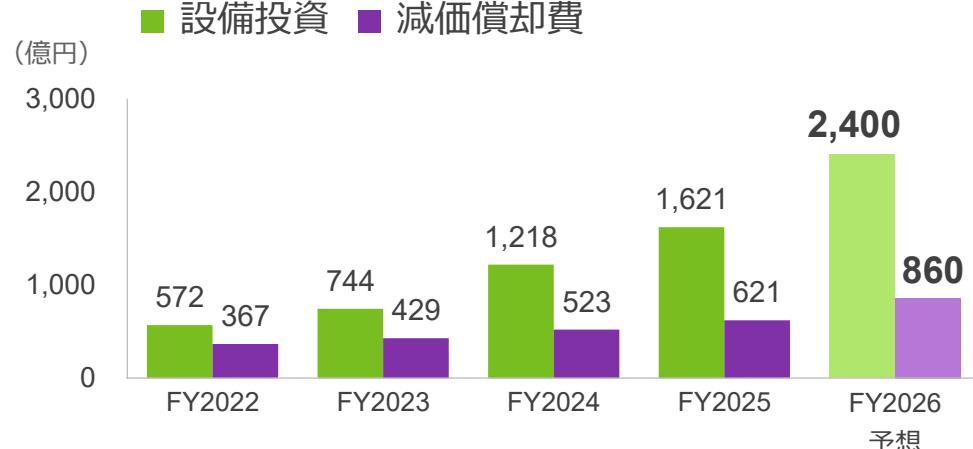

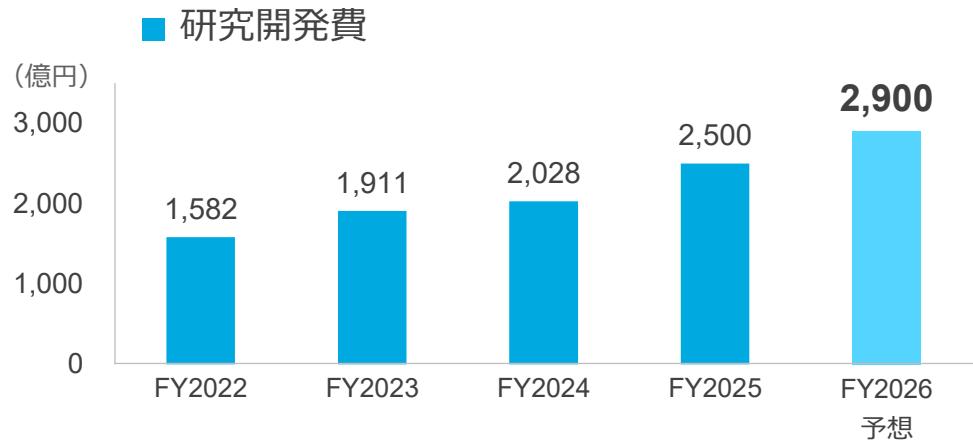

# 積極的な研究開発投資

付加価値の高いnext-generation productsの創出へ

さらなる成長投資を実施

# 現中計以降を見据えた成長投資（FY2025～FY2029）

## 研究開発費

1.5兆円

## 設備投資

7,000億円

## 人材採用

10,000人

毎年2,000人

## 4. 事業環境と業績予想

## 事業環境 (2026年2月時点でのWFE市場の見方)

- CY2026 : 15%以上の成長を見込む

- AIサーバー向け半導体需要の急速な拡大に伴い、先端ロジックとDRAM投資が大幅に増加

- 変動要因 : 顧客工場のクリーンルームスペース、納期（部材供給、労働力）、為替など

- 今後も旺盛なAIアプリケーション需要に牽引され、先端半導体向け投資は中長期的に拡大傾向が続くと見込む

- DRAM : HBMのみならず汎用DRAM向け投資も急増。投資前倒し要求も強い

- NAND : SSD向け需要が急増。稼動率も上昇し新規投資につながる勢い

- ロジック/ファウンドリ : 先端向け投資は今後もさらに増加。

アドバンストパッケージングも進展

- 成熟世代デバイス : 現状と同規模程度のWFEが継続すると予測

付加価値の高い最新装置の需要拡大を見込む

# 先端エリアで拡大する事業機会

\* POR (Process of Record)

: 顧客の半導体製造プロセスにおける装置採用の認定

|             |                                                                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| エッチング       | <ul style="list-style-type: none"><li>・ HBM 配線工程POR、キャパシタ工程 大手POR独占 (DRAM)</li><li>・ Slit工程、チャネルホール工程 POR (NAND)</li><li>・ アドバンストパッケージ向け POR (ロジック)</li></ul>                                |

| 塗布現像        | <ul style="list-style-type: none"><li>・ メタルオキサイドレジスト対応 究極のウェット現像技術評価進捗</li><li>・ 新製品CLEAN TRACK™ LITHIUS Pro DICE™リリース</li></ul>                                                             |

| 成膜          | <ul style="list-style-type: none"><li>・ アドバンストパッケージ向けキャパシタHigh-k POR (ロジック)</li><li>・ 埋め込み膜用 枚葉プラズマCVD 評価開始 (ロジック)</li><li>・ 新低抵抗メタルワードライン工程POR (NAND)</li></ul>                             |

| 洗浄          | <ul style="list-style-type: none"><li>・ 次世代超臨界装置、複数顧客において評価開始 (DRAM)</li><li>・ レジスト剥離 複数顧客で評価中、1社POR獲得済 (ロジック/メモリ)</li><li>・ バッチ+枚葉のハイブリッド装置評価開始 (ロジック/メモリ)</li></ul>                        |

| プローバ        | <ul style="list-style-type: none"><li>・ AI/HPC向け先端Logicで市場を席捲。プローバ全体でFY2027売上1,000億円超</li><li>・ ダイプローバ、複数顧客で評価開始。4月リリース予定</li></ul>                                                          |

| ボンダー / レーザー | <ul style="list-style-type: none"><li>・ ボンダー : HBM薄化向け、NANDメモリセル+周辺回路、ロジック裏面配線、アドバンストパッケージ向け POR</li><li>・ レーザーリフトオフ・トリミング、複数顧客にてプロセス評価進捗</li><li>・ ボンダー/レーザー売上 今後5年で5,000億円以上を見込む</li></ul> |

| ディスプレイ      | <ul style="list-style-type: none"><li>・ エッチング シェア80%以上、IT OLED向け高付加価値製品投入</li></ul>                                                                                                          |

先端アプリケーション装置における展開とともに、

AI関連需要によるフィールドソリューションの事業機会も拡大

## 事業進捗

- 生産性と環境性能を向上させる新製品2種リリース

- CLEAN TRACK™ LITHIUS Pro DICE™:

世界最高クラスの生産性と革新的な欠陥制御技術を備えた最新鋭の塗布現像装置

- EVAROS™:

最大処理能力200枚、高精度・高品質な成膜コントロールを叶えたCVD/ALD装置

- Clarivate Top 100 グローバル・イノベーター 2026受賞

- 高度な発明を継続的に生み出していることが評価され、5年連続 6度目の受賞

- 半導体製造装置業界で世界1位を誇る保有特許件数：26,029件（2025年末時点）

革新的で付加価値の高い独自の技術を継続的に創出するべく、

積極的な研究開発投資を実施

# 2026年3月期 業績予想

(億円)

|                 | FY2025<br>(実績) | FY2026  |          |          |           |        | ご参考：FY2026<br>10/31時点予想 |          |

|-----------------|----------------|---------|----------|----------|-----------|--------|-------------------------|----------|

|                 |                | H1 (実績) | H2 (新予想) | 通期 (新予想) | vs FY2025 | 通期修正額* | H2                      | 通期       |

| 売上高             | 24,315         | 11,796  | 12,303   | 24,100   | -0.9%     | 300    | 12,003                  | 23,800   |

| 売上総利益           | 11,462         | 5,388   | 5,531    | 10,920   | -4.7%     | 130    | 5,401                   | 10,790   |

| 売上総利益率          | 47.1%          | 45.7%   | 45.0%    | 45.3%    | -1.8pts   | -      | 45.0%                   | 45.3%    |

| 販管費             | 4,489          | 2,357   | 2,632    | 4,990    | +11.1%    | 60     | 2,572                   | 4,930    |

| 研究開発費           | 2,500          | 1,348   | 1,551    | 2,900    | +16.0%    | -      | 1,551                   | 2,900    |

| 研究開発費以外の販管費     | 1,989          | 1,009   | 1,081    | 2,090    | +5.1%     | 60     | 1,021                   | 2,030    |

| 営業利益            | 6,973          | 3,031   | 2,898    | 5,930    | -15.0%    | 70     | 2,828                   | 5,860    |

| 営業利益率           | 28.7%          | 25.7%   | 23.6%    | 24.6%    | -4.1pts   | -      | 23.6%                   | 24.6%    |

| 税金等調整前当期純利益     | 7,061          | 3,129   | 4,010    | 7,140    | +1.1%     | 790    | 3,220                   | 6,350    |

| 親会社株主に帰属する当期純利益 | 5,441          | 2,416   | 3,083    | 5,500    | +1.1%     | 620    | 2,463                   | 4,880    |

| 1株当たり当期純利益 (円)  | 1,182.40       | 527.31  | -        | 1,200.05 | +17.65    | 135.28 | -                       | 1,064.77 |

\* 2025年10月31日に発表した通期業績予想からの修正額を示しています。

力強い事業環境を踏まえ、通期の業績予想を上方修正。

政策保有株式の追加売却に伴う特別利益も反映

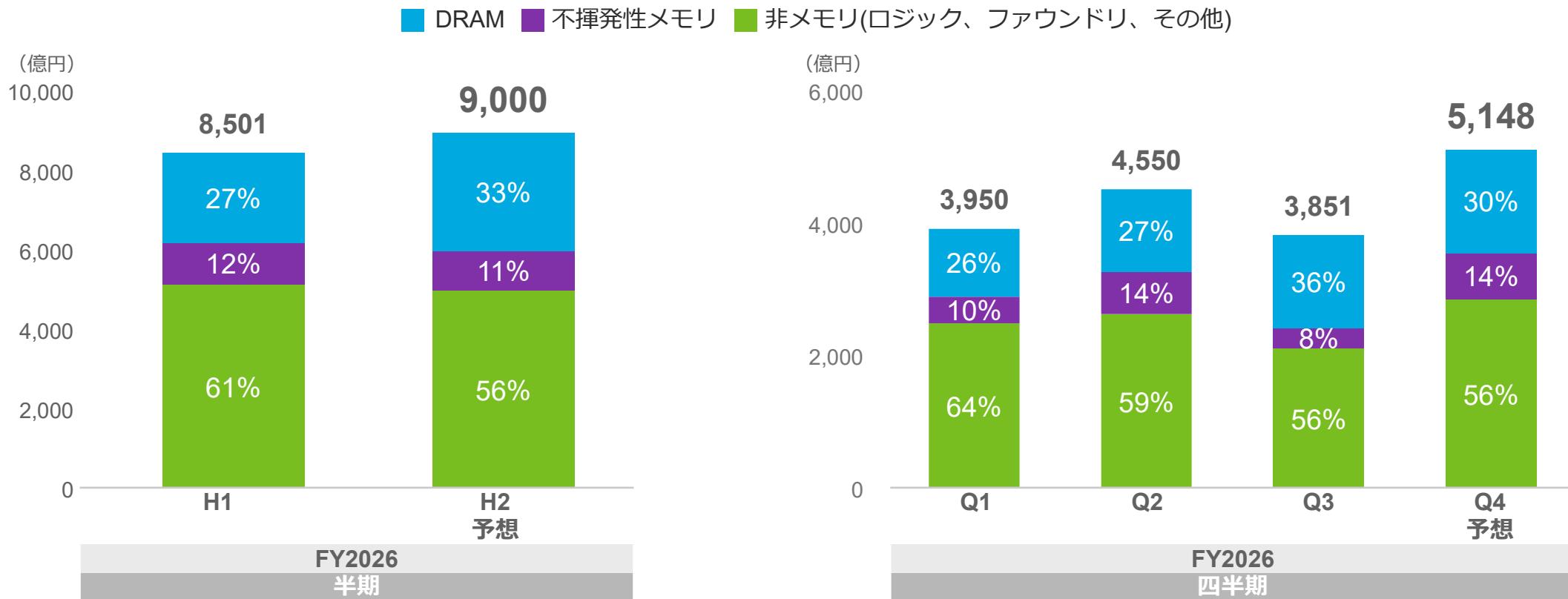

# 2026年3月期 SPE新規装置売上予想

## アプリケーション別売上構成比

\* グラフは新規装置の売上高における構成比を示しています。フィールドソリューション売上高は含まれていません。

FY2026 H2のSPE新規装置売上予想を9,000億円に更新。

Q4の新規装置売上はQ3比 +30%以上を見込む

# 2026年3月期 研究開発費・設備投資計画

宮城 第3開発棟

エッチング装置

宮城県黒川郡

2025年4月 竣工

東北生産・物流センター

成膜装置

岩手県奥州市

2025年11月 竣工

熊本プロセス開発棟

コータ/デベロッパ、洗浄装置

熊本県合志市

2025年10月 竣工

宮城生産革新センター

エッチング装置

宮城県黒川郡

2027年夏 竣工予定

半導体の技術革新を支える対応力と急速な需要拡大に応える生産能力を確立。

今後の収益機会を着実に捉え、企業価値の最大化を目指す

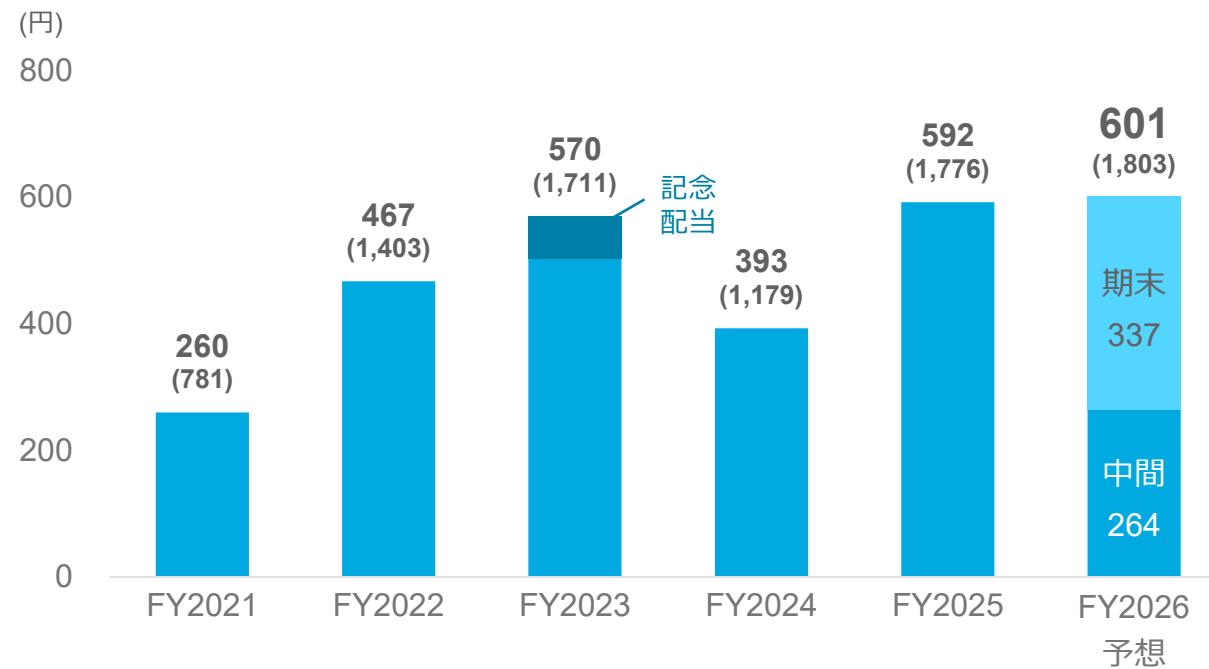

# 2026年3月期 配当予想

## 1株当たり配当金

- FY2021～2023の1株当たり配当額は、FY2021の期首に株式分割がおこなわれたと仮定した金額を記載しています。

- FY2023には60周年記念配当が含まれます。

- 株式分割がおこなわれる以前の金額を（）内で記載しています。

## 当社の株主還元策

### 連結配当性向： 50%

但し、1株当たり年間配当金50円\*を下回らない

2期連続して当期利益を生まなかつた場合は、配当金の見直しを検討する

### 自己株式の取得： 機動的に実施を検討

\*2023年4月1日付の株式分割により、従来の150円から変更しています。

1株当たり通期配当予想は過去最高の601円に上方修正

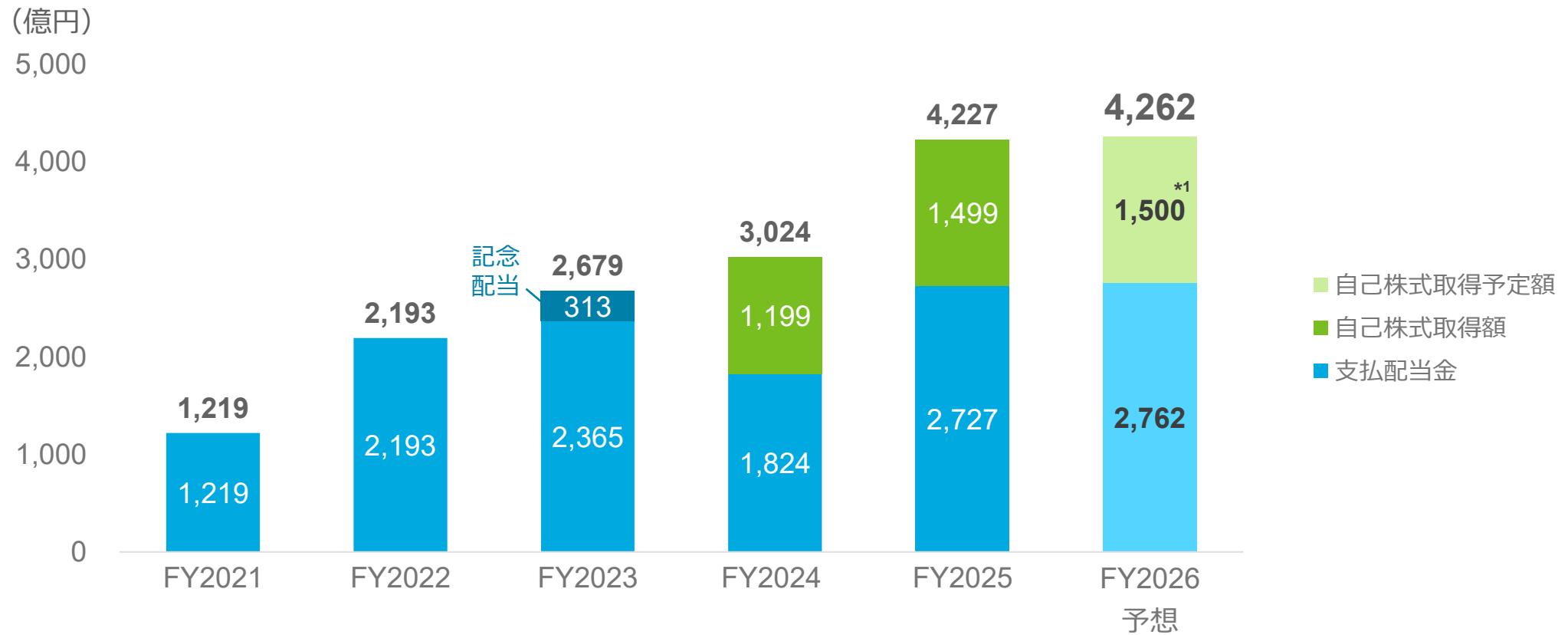

# 自己株式の取得について

## 最大1,500億円の自己株式取得を予定

- 取得対象株式の種類 : 当社普通株式

- 取得し得る株式の総数 : 750万株（上限）

(自己株式を除く発行済株式総数に対する割合 1.6%)

- 株式の取得価額の総額 : 1,500億円（上限）

- 取得する期間 : 2026年2月9日～2026年3月31日

拡大する当社の事業機会とキャッシュ創出力、資本効率の向上を考慮し、

今後も適切なバランスシート・マネジメントを実施

# 総還元額

自己株式取得と合わせ、過去最高の総還元額を見込む

## 5. サステナビリティ

# サステナビリティの取り組み

重要かつ優先的に取り組むべき14のマテリアリティ(重要分野)を特定し、事業を通じたサステナビリティ活動を展開して産業や社会の課題解決と発展に貢献します。

人権の尊重

気候変動とネットゼロ

製品の環境性能

革新的な技術をもつBest Products

付加価値の高いBest Technical Service

顧客満足と信頼

サプライヤーリレーションシップ

従業員のエンゲージメント

安全第一のオペレーション

品質マネジメント

コンプライアンス

高い倫理観に基づく行動

情報セキュリティ

エンタープライズリスクマネジメント

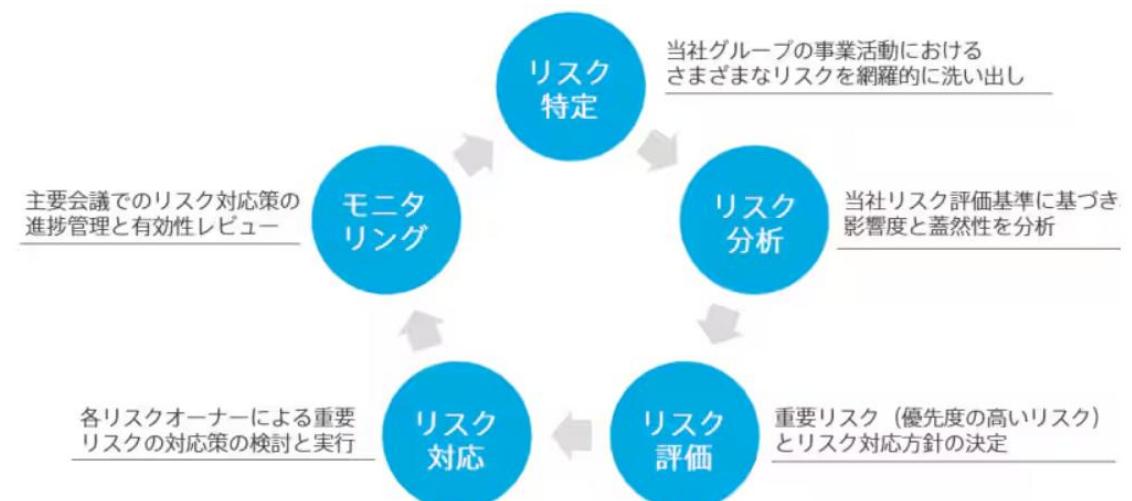

# リスクマネジメントの体制と実行

## 体制

- ・ グループ全体としてより実効的な活動を推進するため、コーポレート企画＆リスクマネジメント推進室 (CPRO) を本社の経営戦略本部に設置。エンタープライズ・リスクマネジメント<sup>\*1</sup>の推進を強化

- ・ 当社グループにおけるリスクマネジメントに関する活動については定期的に取締役会に報告。取締役会はさまざまな取り組みについての監督をおこなう

- ・ リスクマネジメントの意識向上と基礎知識の習得を目的として、当社グループの社員を対象としたリスクマネジメントに関するウェブトレーニングや管理職向け研修などを定期的に実施

## PDCAサイクルの展開

事業活動における重要なリスク<sup>\*2</sup>については、右記のようなPDCAサイクルを展開。

レビューと見直しのサイクルを回すことで、各リスクに対する取り組みを強化。

<sup>\*1</sup> エンタープライズ・リスクマネジメント：リスクマネジメント活動に関する全社的な仕組みやプロセス

<sup>\*2</sup> 重要なリスク：リスク項目の特定 及び 各リスク項目の詳細については、当社ウェブサイト「リスクマネジメント」ご参照

<https://www.tel.co.jp/sustainability/management-foundation/risk-management/index.html>

# 環境へのアプローチ

スコープ1、2 & 3 2041年3月期までにネットゼロを実現

スコープ1、2: 事業活動における電力などのエネルギー使用による排出

スコープ3: 販売した装置の使用や廃棄、資材の購入や物流などにおける排出

# E-COMPASS

Environmental Co-Creation by Material, Process and Subcomponent Solutions

## 半導体

デバイスの高性能化と

低消費電力化

## 製造装置

装置のプロセス性能と

環境性能の両立

## 事業活動

事業活動全体における

CO<sub>2</sub>排出量削減

サプライチェーン全体で半導体の技術革新と環境負荷低減を推進

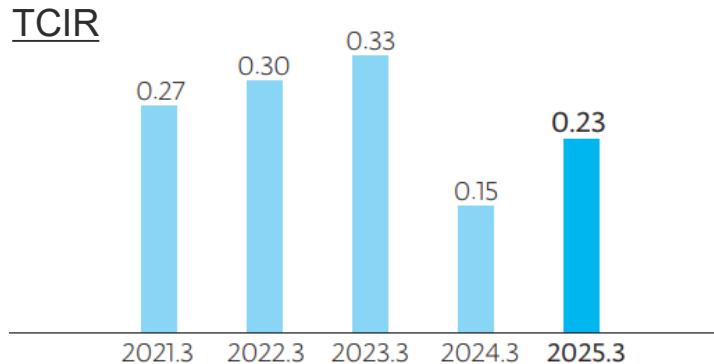

# 安全・品質

## 安全

当社では「Safety First」のスローガンのもと、開発・製造・輸送・据付・メンテナンスなどの各種業務遂行において、トップマネジメントから現場担当者まで、全ての人が安全と健康を最優先とし、安全性向上および健康推進に向けて、積極的かつ継続的な改善に努めています。

2025年3月期は、安全教育の強化や装置安全設計への継続的な取り組みにより、半導体製造装置業界トップクラスの0.23を維持。

安全に関する目標

(~FY2027)

**TCIR ≤ 0.1**

TCIR: Total Case Incident Rate (労働時間20万時間当たりの人身事故発生率)

### 事故防止への取り組み

- ・体感教育とVR (Virtual Reality)

- ・安全総点検

- ・安全使用のフィードバック

- ・お取引様に対する安全活動

## 品質

当社は、提供する製品およびサービスが高い品質であることを目指します。それは開発に始まり製造・据付・保守すべての工程を含む、また営業活動の顧客対応業務も品質とみなします。わたしたちは、お客様の成功を支える高品質の製品とサービスおよび革新的なソリューションを提供し続けます。

### 品質方針

1 「品質優先」

2 フロントローディングと自工程保証

3 品質と信頼

4 継続的改善活動

5 ステークホルダーとのコミュニケーション

## 行動規範としての TEL Values

## エンゲージメント

## キャリア

# 企業の成長は人 社員は価値創出の源泉

## リテンション

## ワークライフバランス

## ダイバーシティ エクイティ&インクルージョン

3G

Global · Generation · Gender

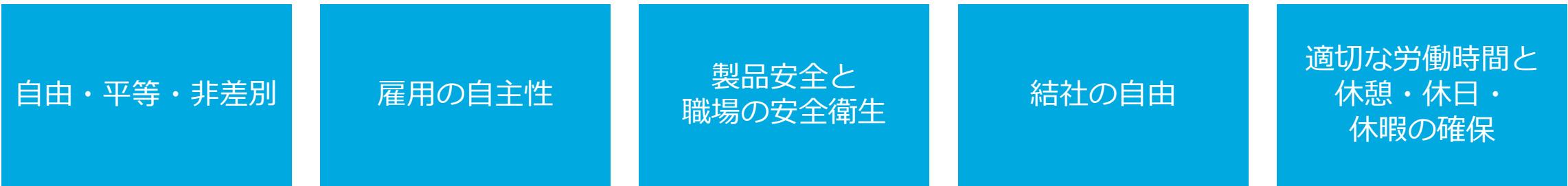

# 人権への取り組み

人権に関する5つの重要項目（東京エレクトロングループ人権方針）

## 人権デューデリジェンス

### 人権尊重のコミットメント

- 「東京エレクトロングループ人権方針」改定

- 周知と徹底

- 教育

### 事業およびサプライチェーン上の人権リスクの評価

- 人権リスクアセスメント

- 人権インパクトアセスメント

### 評価の結果に基づくリスク軽減に向けた行動

- フィートバックシートの発行

- 課題に応じたプログラムの構築とレビュー

### 定期的な情報の開示

- 統合報告書の発行

- ウェブサイトへ掲載

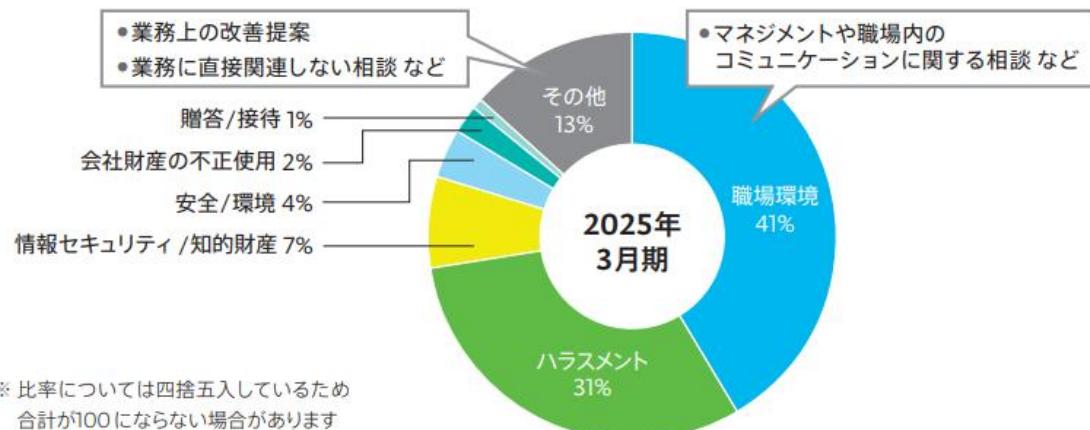

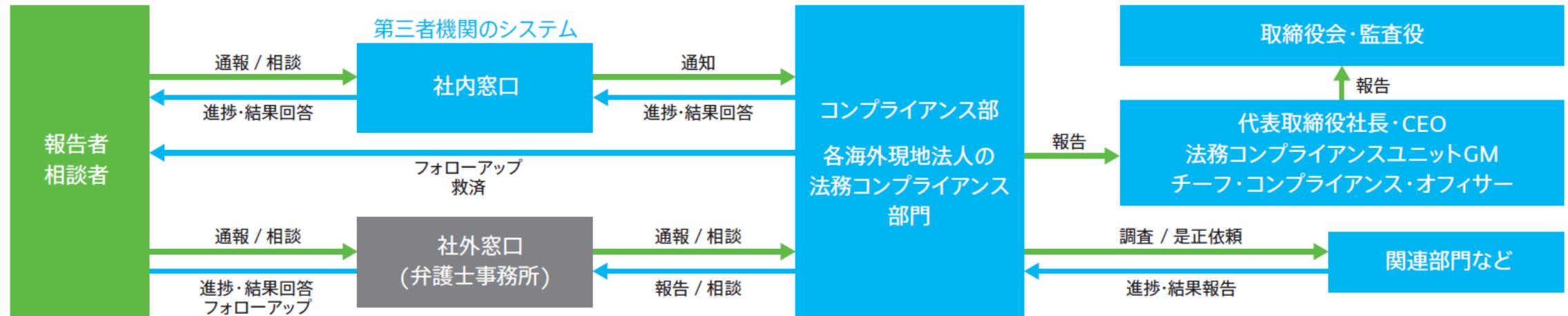

# 内部通報制度

人権を尊重し、真摯な姿勢で対応

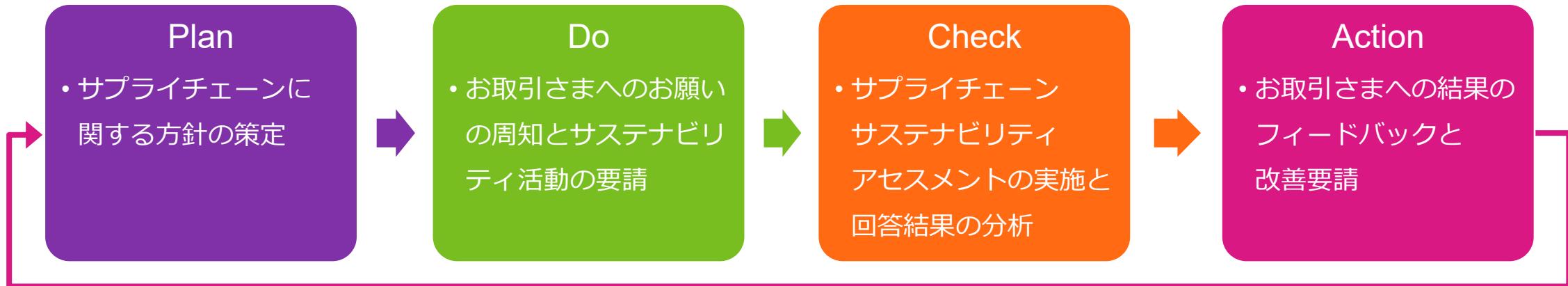

# サプライチェーンマネジメント

サプライチェーンサステナビリティのプロセス

- 年次サステナビリティアセスメント

- RBAの行動規範に基づく評価

- 是正措置計画

- RBAが定める監査基準で調査内容を改定

- 主要な生産拠点で実施

- 各業務の継続的な改善

サプライチェーン全体でサステナビリティを意識したオペレーションを追求

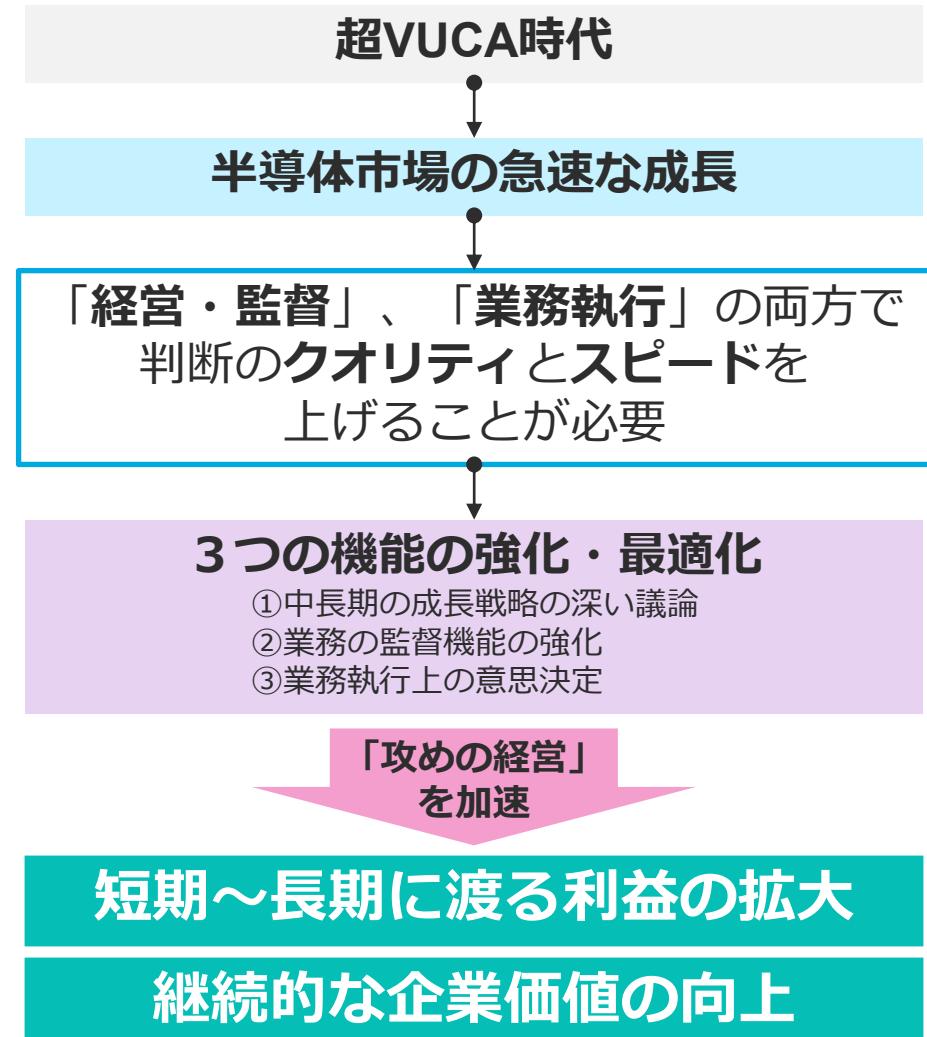

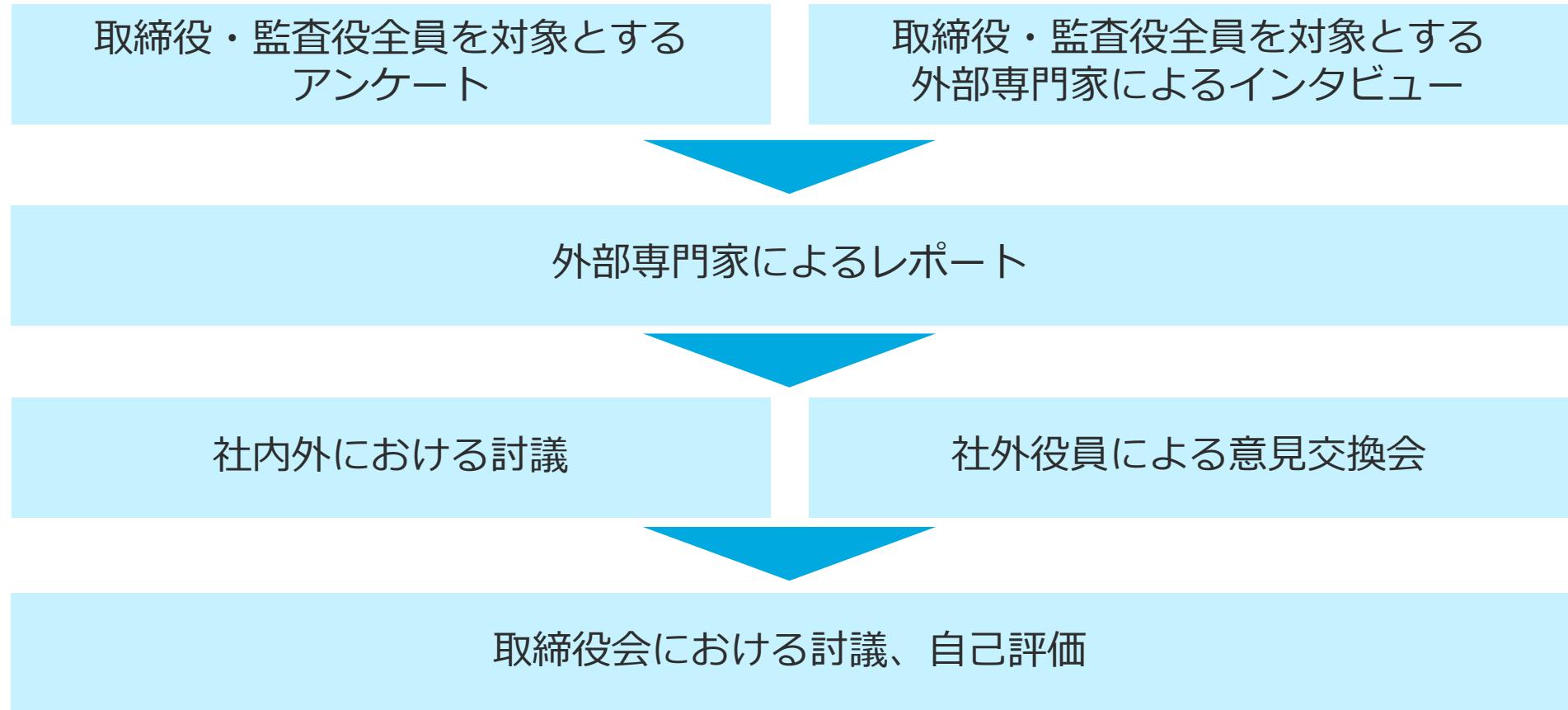

# コーポレート・ガバナンス体制（監査役会設置会社）

<体制図一部抜粋>

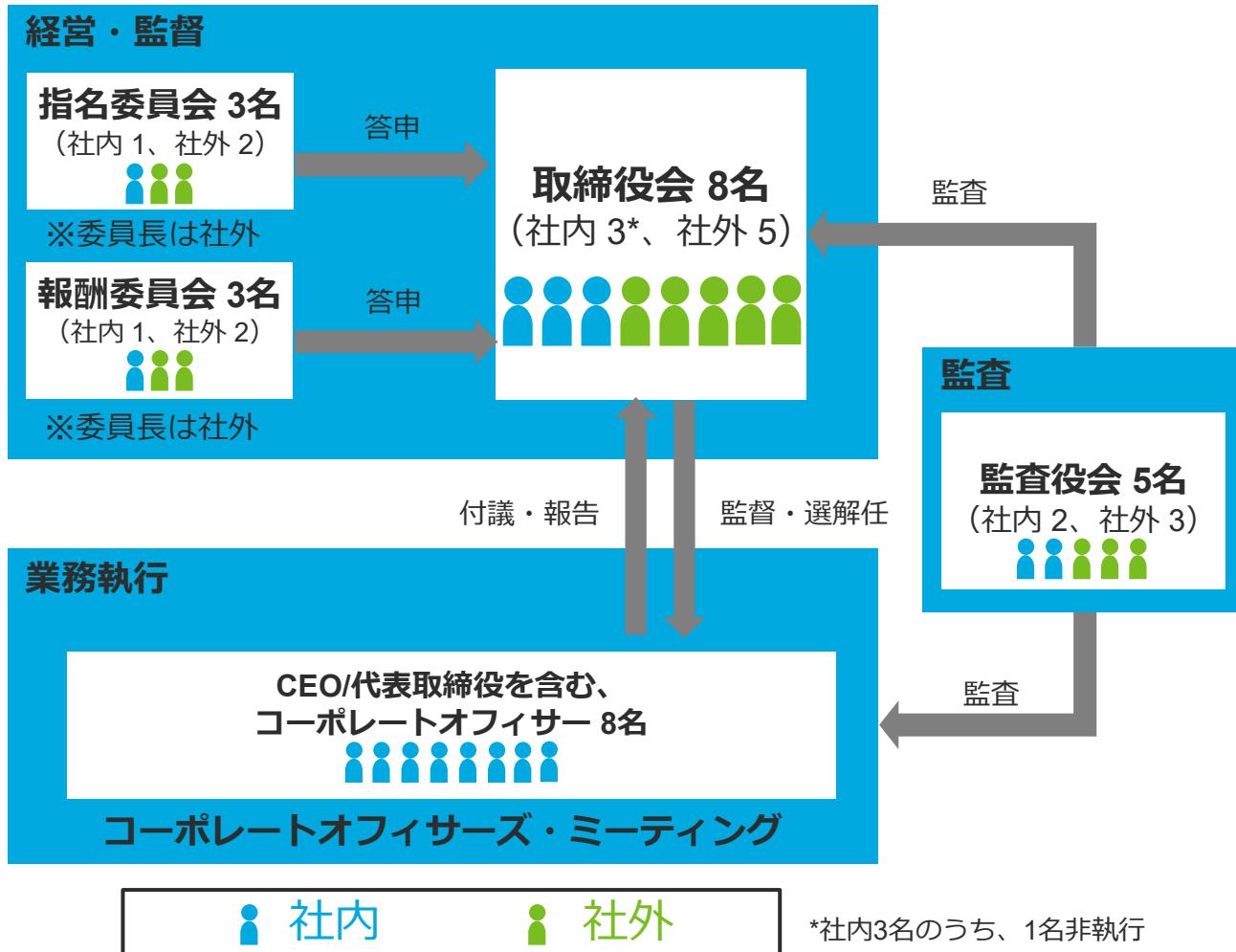

# 取締役会の実効性評価

社内および外部専門家が分析し、取締役会の実効性を評価

# グローバル・イニシアティブ

## SDGs(持続可能な開発目標)

事業を通じた取り組みをマテリアリティごとに明確にし、グループ全体に展開

東京エレクトロンはSDGsを支援しています

## 国際的なイニシアティブへの参画

国連グローバル・コンパクトに署名、Responsible Business Alliance (RBA)に参画、Task Force on Climate-related Financial Disclosures (TCFD)に賛同

## 当社のESGに関する外部評価

世界各国の評価機関より高い評価を獲得

Dow Jones Best-in-Class

Asia Pacific Index

FTSE4Good

東京エレクトロン株式会社のMSCI指数への組み入れ、およびMSCIのロゴ、商標、サービスマークまたは指數名の使用は、MSCIまたはその関係者による東京エレクトロン株式会社の後援、推進またはプロモーションではありません。MSCI指數はMSCIの独占的財産です。

MSCI指數の名前およびロゴはMSCIまたはその関係会社の商標またはサービスマークです。

TEL

56

## 6. 多様化する半導体技術～技術ロードマップ～

# 半導体デバイス：開発の方向

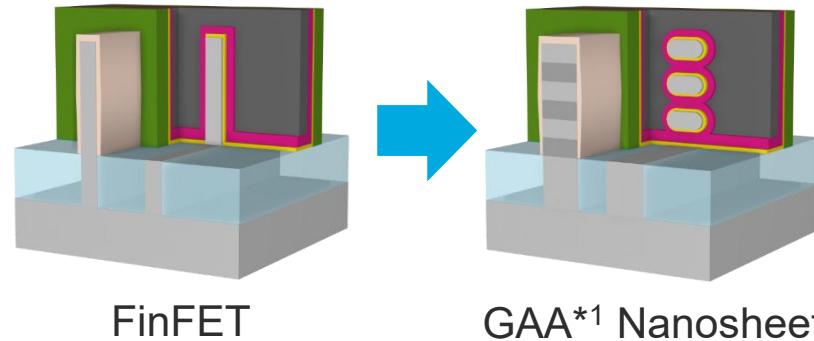

\*1 GAA: Gate All Around

\*2 BSPDN: Backside Power Delivery Network

## 構造変化を伴う微細化による

- ・トランジスタ当たりのコスト低減

- ・低消費電力化

- ・高速化

## 微細化による

- ・ビット当たりのコスト低減

- ・低消費電力化

- ・高速化

## 新構造による

- ・ビット当たりのコスト低減

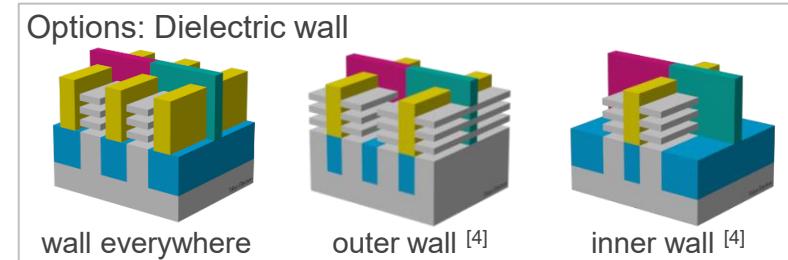

# Logic技術ロードマップ (Generic)

- [1] Chih-Hao Chang (TSMC) et al., IEDM 2022

- [2] Shien-Yang Wu (TSMC) et al., IEDM 2022

- [3] Sandy Liao (TSMC) et al., IEDM 2024

- [4] Mertens and Horiguchi (imec), EDTM 2024

Source: TEL estimates

| Year of HVM<br>(20k/month) | 2022~24                                   | 2025~2026   | 2027~28        | 2030~31                     | 2033~34                        | 2036~37                                                                     | 2039 and beyond           |                   |

|----------------------------|-------------------------------------------|-------------|----------------|-----------------------------|--------------------------------|-----------------------------------------------------------------------------|---------------------------|-------------------|

| Node                       | 3nm                                       | 2nm/18A/16A | 14A            | 10A                         | 7A                             | 5A                                                                          | 3A                        | 2A                |

| Transistor                 | 2~1 Fin                                   | GAA NS      | GAA NS scaling | GAA NS extension            | CFET                           | 2 <sup>nd</sup> Gen. CFET                                                   | 3 <sup>rd</sup> Gen. CFET | 2D material stack |

| Poly Pitch [nm]            | 48~45 <sup>[1]</sup>                      |             | 45~42          |                             | 48 <sup>[3]</sup> ~42          | 45~39                                                                       |                           | 36                |

| Min. Metal Pitch [nm]      | 23 <sup>[2]</sup>                         |             | 20             | 18                          | 17                             | 16                                                                          | 14                        | 12                |

| Interconnect booster       | Cu Barrier/Seed CIP<br>Backside PDN (HPC) |             |                | Cu CIP or<br>Ru subtractive | Ru subtractive<br>AR>3, Airgap | New alloy AR>5, Airgap,<br>BEOL Transistor (OS <sup>*5</sup> , 2D material) |                           |                   |

| EUV Patterning Technology  | EUV MP <sup>*1</sup> , SE <sup>*2</sup>   |             |                | EUV MP, SE<br>High-NA SE    |                                | High-NA MP, SE<br>EUV MP, SE                                                |                           |                   |

| Resist                     | CAR <sup>*3</sup>                         |             |                | CAR (+MOR <sup>*4</sup> )   |                                | CAR+MOR                                                                     |                           |                   |

\*1 MP: Multi-Patterning, \*2 SE: Single-Exposure, \*3 CAR: Chemically Amplified Resist, \*4 MOR: Metal Oxide Resist, \*5 OS: Oxide Semiconductor

Logicの微細化は、トランジスタの構造と材料を変えながら続していく

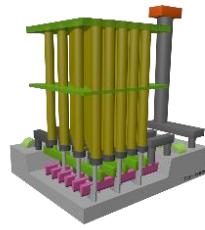

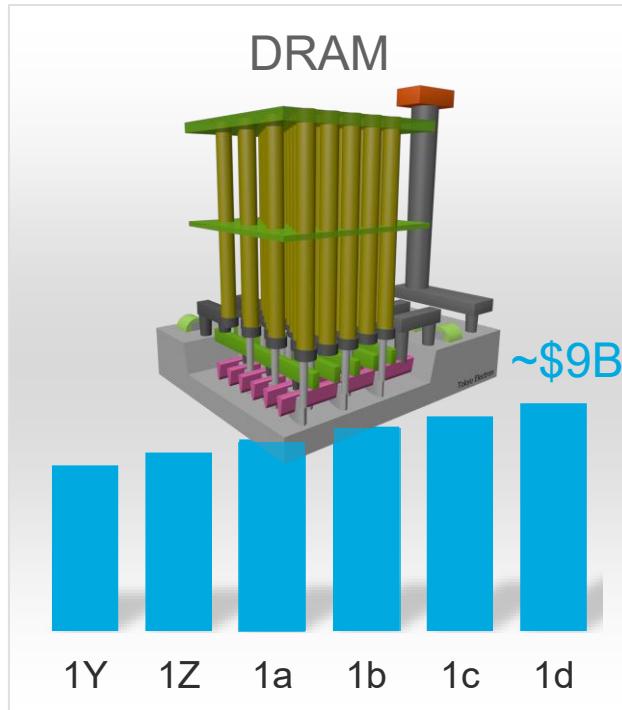

# DRAM 技術ロードマップ(Generic)

Source: TEL estimates

| Year of HVM<br>(20k/month) | 2025                                                                              | 2026                  | 2027                                                                               | 2028                             | 2029                                                                                | 2030                      | 2031                                                                                | 2032                                  | 2033                                                                                 | 2034       | 2035 | 2036 |

|----------------------------|-----------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------|------------|------|------|

| Node                       | 1c                                                                                | 1d                    | 0a                                                                                 | 0b                               |                                                                                     | 0c                        | 0d                                                                                  | 0e                                    |                                                                                      |            |      |      |

| Cell layout / Structure    |  | <b>6F<sup>2</sup></b> |  | <b>4F<sup>2</sup> VCT* [1-3]</b> |  | <b>4F<sup>2</sup> VCT</b> |  | <b>3D※</b>                            |                                                                                      |            |      |      |

| F [nm]                     | 12~11                                                                             | 10                    | (6F <sup>2</sup> )<br>(VCT)                                                        | 9<br>15                          | 8<br>13.5                                                                           | 12                        |                                                                                     |                                       | (3D ~1xxL)                                                                           | (3D >1yyL) |      |      |

| Capacitor pitch [nm]       | 36~33                                                                             | 30                    | (6F <sup>2</sup> )<br>(VCT)                                                        | 27<br>30                         | 24<br>27                                                                            | 24                        |                                                                                     |                                       |                                                                                      |            |      |      |

| Capacitor aspect ratio     | 40                                                                                | >40                   |                                                                                    | >40                              |                                                                                     | >40                       |                                                                                     |                                       |                                                                                      |            |      |      |

| Word line                  | TiN                                                                               |                       |                                                                                    | Low R metal                      |                                                                                     |                           |                                                                                     |                                       |  |            |      |      |

| Peri. CMOS                 | <b>Gate First HKMG</b>                                                            |                       |                                                                                    |                                  | <b>Bonding</b>                                                                      |                           |                                                                                     | <b>Gate last Planer MOS or FinFET</b> |                                                                                      |            |      |      |

| HBM                        | HBM4                                                                              | HBM4E                 | HBM5                                                                               |                                  | HBM5E                                                                               |                           | HBM6                                                                                |                                       | HBM6E                                                                                | HBM7       |      |      |

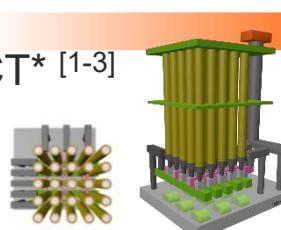

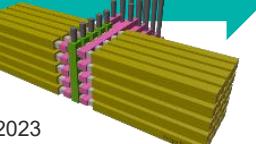

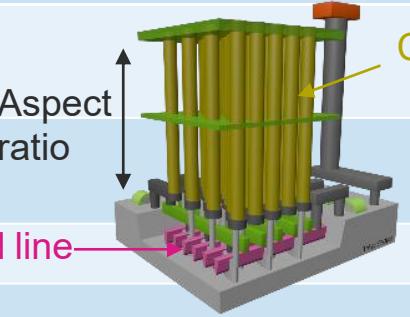

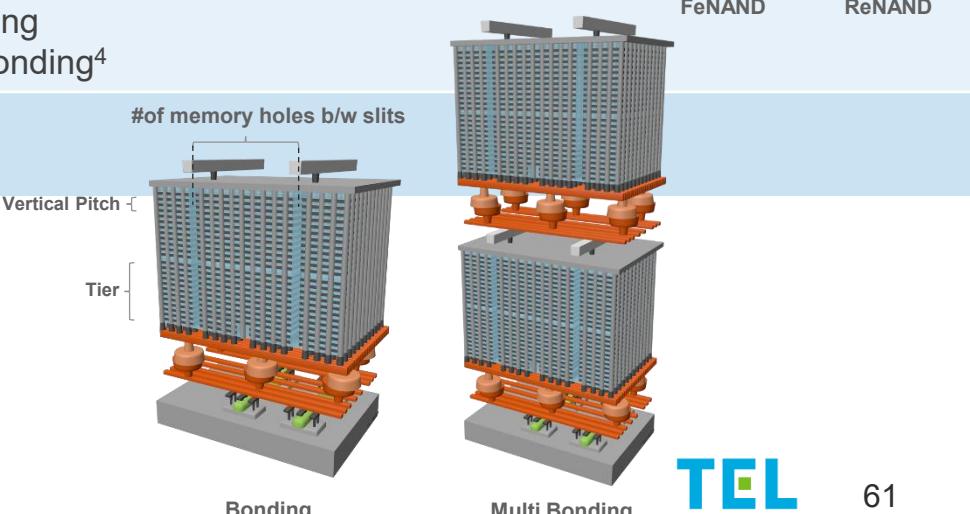

# NAND 技術ロードマップ(Generic)

Source: TEL estimates

| Year of HVM<br>(20k/month) | 2025                      | 2026    | 2027   | 2028                                | 2029                                     | 2030                       | 2031 | 2032   | 2033 | 2034   | 2035 | 2036    |

|----------------------------|---------------------------|---------|--------|-------------------------------------|------------------------------------------|----------------------------|------|--------|------|--------|------|---------|

| Stack<br>(~1.3x/1.5years)  | 3xxL                      | 4xxL    | 5xxL   | 6xxL                                |                                          | 8xxL                       |      | *1xxxL |      | *1yyyL |      | *1zzzL  |

| Tier                       | 2 or 3                    | 3       | 3 or 4 | 3 or 4                              |                                          | 4 - 6                      |      |        |      |        |      |         |

| Min vertical pitch         | 40 nm                     | 39 nm   | 38 nm  | 37 nm                               |                                          | 36 nm                      |      |        |      |        |      | ~ 30 nm |

| Max memory height          | 14 µm                     | 19 µm   | 25 µm  |                                     | 40 µm                                    |                            |      |        |      |        |      |         |

| Charge trap (CT)           | Continuous CT             |         |        |                                     | CT isolation <sup>1</sup>                |                            |      |        |      |        |      |         |

| Channel                    | Poly Si grain CIP         |         |        | MILC <sup>2</sup> /MIC <sup>3</sup> |                                          |                            |      |        |      |        |      |         |

| WL metal                   | W or Mo                   |         |        | Mo                                  |                                          |                            |      |        |      |        |      |         |

| Layout/Structure           | Under array<br>or Bonding | Bonding |        |                                     | Bonding<br>or Multi Bonding <sup>4</sup> |                            |      |        |      |        |      |         |

| Peri. CMOS                 | Poly Si Gate              |         | HKMG   |                                     |                                          | #of memory holes b/w slits |      |        |      |        |      |         |

\* Trend Extrapolation

<sup>1</sup> 2021 IRPS Memory's journey towards the future information and communications technology (ICT) world - SK hynix

<sup>2</sup> Metal induced lateral crystallization

<sup>3</sup> Metal induced crystallization

<sup>4</sup> 2023 IEDM Fundamental Issues in VNAND Integration Toward More Than 1K Layers - Samsung

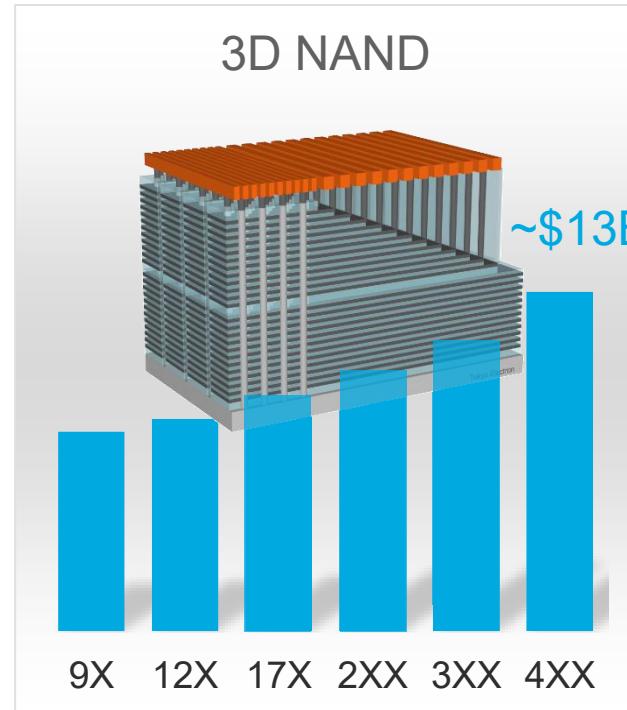

# 高まる半導体製造装置の付加価値

月産10万枚当たりWFE投資額 (Greenfield、当社予測)

新たなアプリケーションの登場と技術難易度の高まりが、

半導体製造装置メーカーの事業機会を拡大

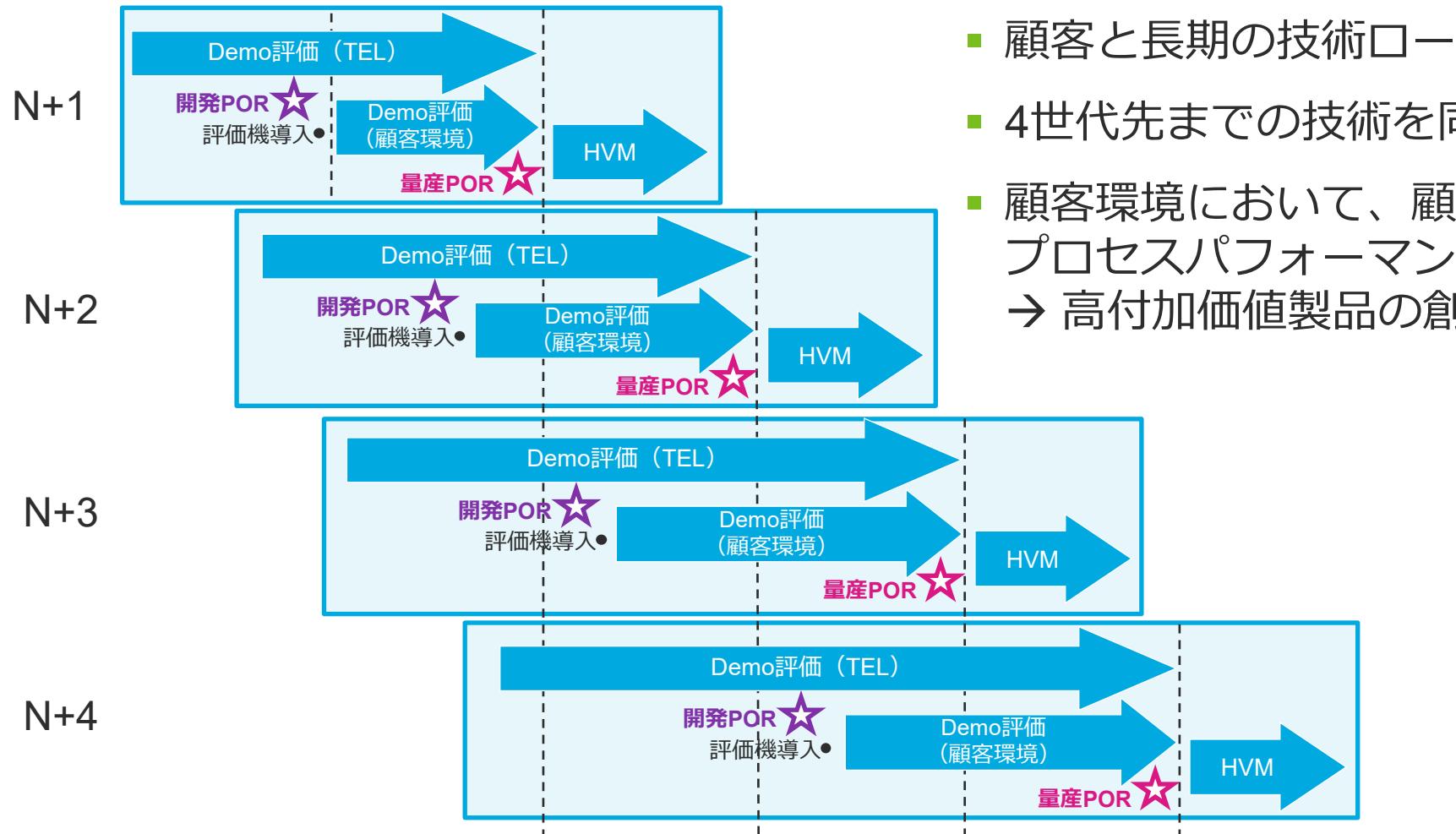

## 7. 新規装置事業の取り組み

# 開発の取り組み

## 4世代同時開発

- 顧客と長期の技術ロードマップ・アライメント

- 4世代先までの技術を同時に開発、評価

- 顧客環境において、顧客の評価ウェーハ上でプロセスパフォーマンスを早期に実証

→ 高付加価値製品の創出およびPOR獲得

# 前工程における当社の成長機会

- AI関連デバイスの牽引によりWFEのCAGRは引き続き高い水準で成長

- TELの強みを生かし、高い市場成長領域に対応

- 先端ロジック：エッチャングが2.7倍/成膜が2.5倍の市場成長見込む\*

- DRAM：エッチャングの市場が2.3倍と、WFEのCAGRを超える成長を見込む\*

- 技術変革点への対応を中心とした新製品の投入により、参入領域をさらに拡大

\* TEL Estimates

# 前工程の技術変革点における成長機会

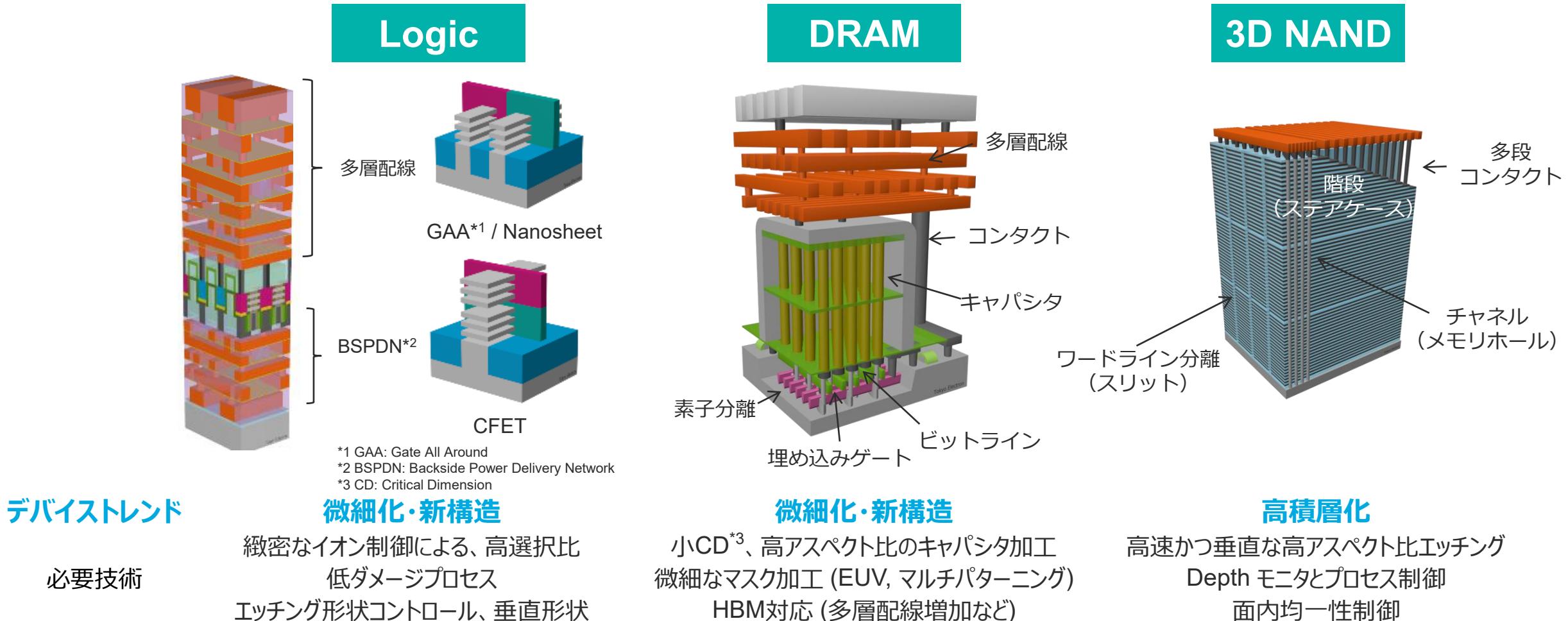

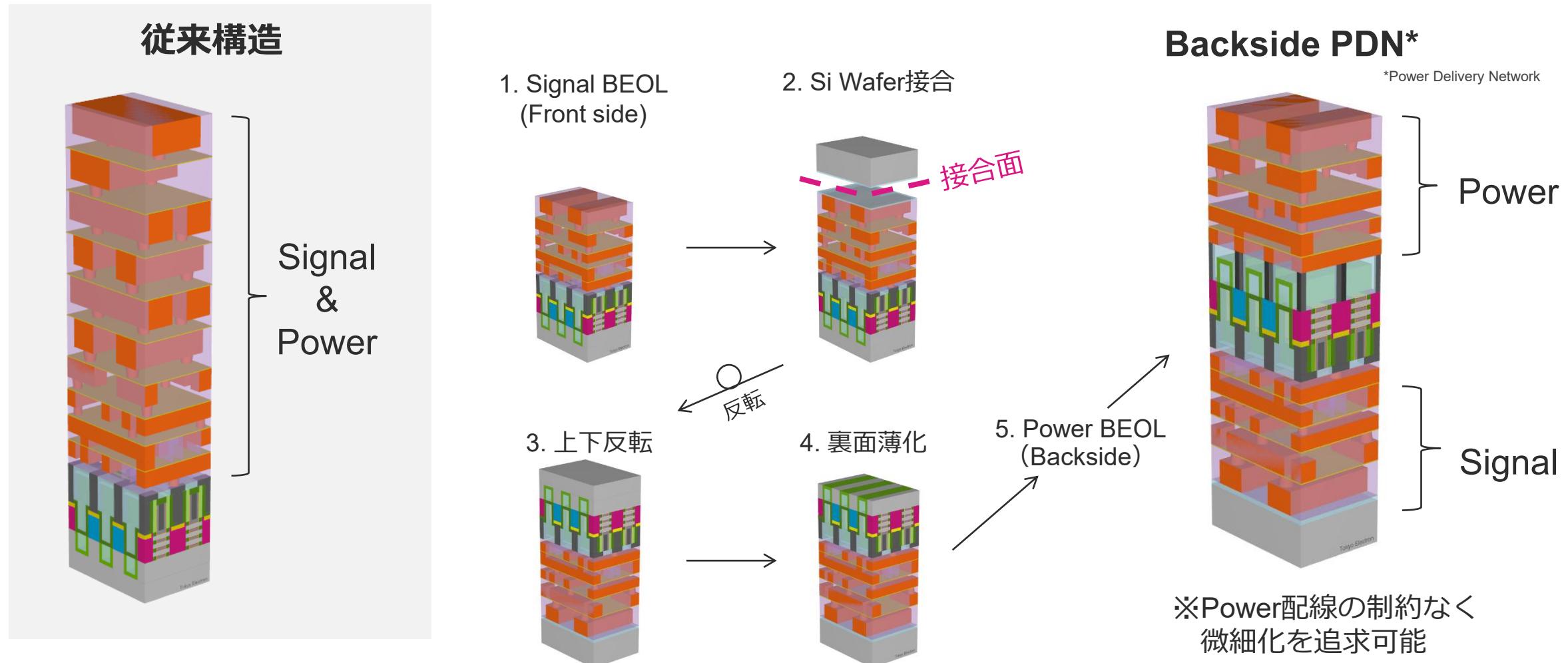

## ■ Logic : GAA<sup>\*1</sup>, Backside PDN<sup>\*2</sup>, CFET

- ・リソグラフィ技術でHigh-NA化、マルチパターニングとの併用、MOR化が進み、新技術Acrevia™に機会

- ・マルチパターニングにより成膜、エッチング、洗浄などの工程数増加

- ・GAA、CFETトランジスタによりガスケミカルエッチングの工程数増加

- ・Ruなど新材料、Airgapのような構造変更も新機会となる

## ■ DRAM : HBM, VCT<sup>\*3</sup>, 3D DRAM

- ・マルチパターニング採用で成膜、エッチング工程数増加

- ・キャパシタ形成の重要性継続し、エッチング、成膜に強い技術ニーズ継続

- ・3D DRAMで成膜、エッチング、ガスケミカルエッチング工程数増加

## ■ NAND : Beyond 4xx

- ・層数増による成膜、エッチング工程の投資増加

- ・高アスペクト比エッチングがより重要に

- ・Moなど新材料、チャネルSi低抵抗化

\*1 GAA: Gate All Around

\*2 Backside PDN: Backside Power Delivery Network

\*3 VCT: Vertical Channel Transistor

## 7-1. 前工程 パターニング

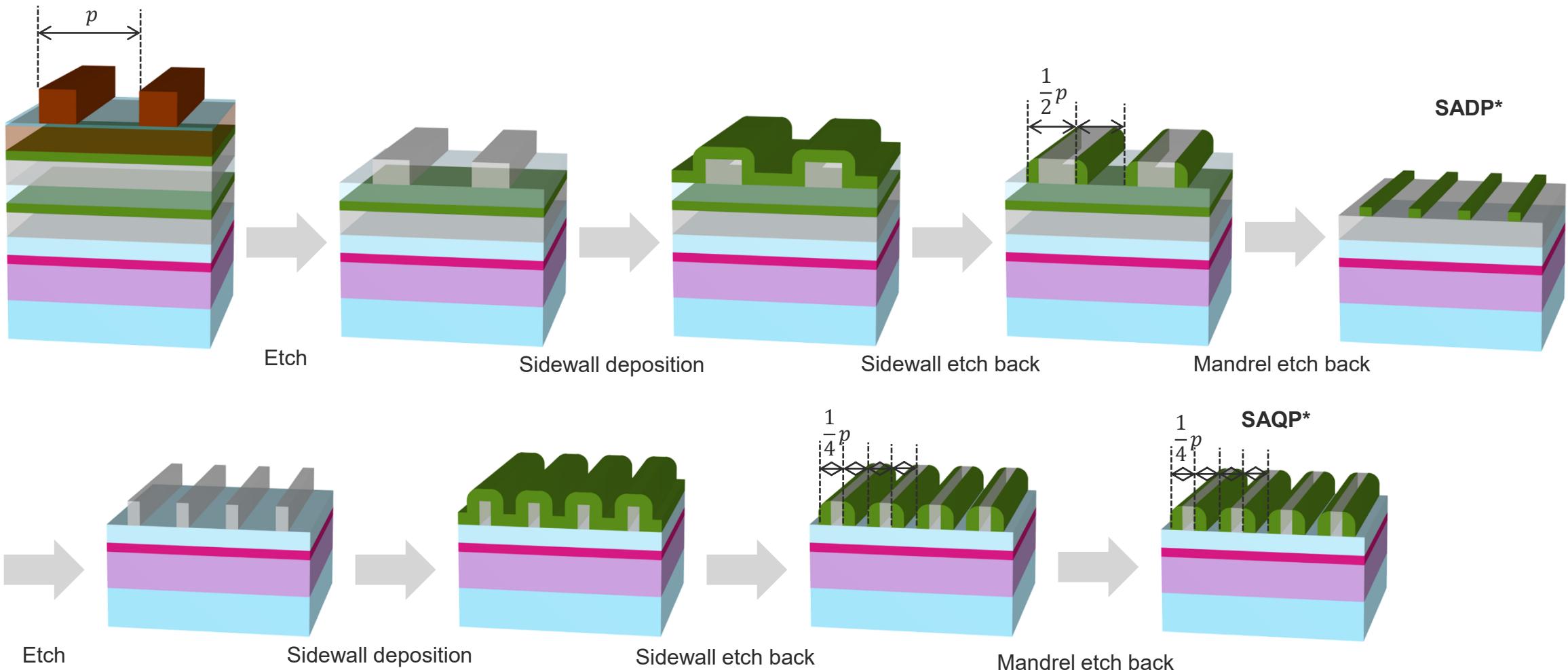

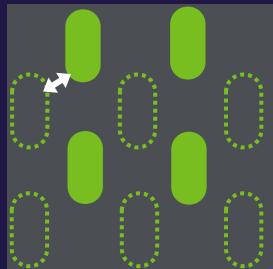

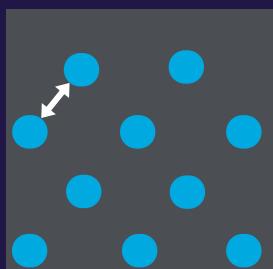

# リソグラフィを補完するパターニング技術 : SADP/SAQP

SADP: Self-aligned double patterning

SAQP: Self-aligned quadruple patterning

# ロジック技術のロードマップと EUVリソグラフィ技術の推移

[<sup>1</sup>] Chih-Hao Chang (TSMC) et al., IEDM 2022

[<sup>2</sup>] Shien-Yang Wu (TSMC) et al., IEDM 2022

[<sup>3</sup>] Sandy Liao (TSMC) et al., IEDM 2024

[<sup>4</sup>] Mertens and Horiguchi (imec), EDTM 2024

Source: TEL estimates

| Year of HVM<br>(20k/month)   | 2022~24                                 | 2025~2026   | 2027~28                   | 2030~31                         | 2033~34                 | 2036~37                   | 2039 and beyond                     |                   |

|------------------------------|-----------------------------------------|-------------|---------------------------|---------------------------------|-------------------------|---------------------------|-------------------------------------|-------------------|

| Node                         | 3nm                                     | 2nm/18A/16A | 14A                       | 10A                             | 7A                      | 5A                        | 3A                                  |                   |

| Transistor                   | 2~1 Fin                                 | GAA NS      | GAA NS scaling            | GAA NS extension                | CFET                    | 2 <sup>nd</sup> Gen. CFET | 3 <sup>rd</sup> Gen. CFET           | 2D material stack |

| Poly Pitch [nm]              | 48~45 [ <sup>1</sup> ]                  |             | 45~42                     |                                 | 48 [ <sup>3</sup> ] ~42 |                           | 45~39                               | 36                |

| Min. Metal Pitch [nm]        | 23 [ <sup>2</sup> ]                     |             | 20                        | 18                              | 17                      | 16                        | 14                                  | 12                |

| EUV Patterning<br>Technology | EUV MP <sup>*1</sup> , SE <sup>*2</sup> |             |                           | EUV MP, SE<br><b>High-NA SE</b> |                         |                           | <b>High-NA MP, SE</b><br>EUV MP, SE |                   |

| Resist                       | CAR <sup>*3</sup>                       |             | CAR (+MOR <sup>*4</sup> ) |                                 |                         |                           | CAR+MOR                             |                   |

\*1 MP: Multi-Patterning, \*2 SE: Single-Exposure, \*3 CAR: Chemically Amplified Resist, \*4 MOR: Metal Oxide Resist

塗布現像装置で、MORや高NA EUVなど将来EUVリソグラフィ技術へ向けて汎用性拡大中

# 塗布現像装置 CLEAN TRACK™ LITHIUS Pro™ Z EUV

2012年 LITHIUS Pro™ Zリリース（累計>3000台出荷）

EUV CAR/MOR対応新機能を順次リリース

高信頼性

EUV市場での高シェア

高生産性

EUV露光機の性能を最大限発揮、薬液消費量低減

高汎用性

化学増幅型レジスト(CAR)に加え、

メタルオキサイドレジスト(MOR)や下層膜にも対応

\*1 CAR: Chemically Amplified Resist

\*2 MOR: Metal Oxide Resist

さまざまな光源の露光機向けに長年の量産実績のあるLITHIUS Pro™ Z プラットフォームで、

EUV露光機向けにも高信頼性、高生産性を担保。次世代EUV向け高汎用性も実現

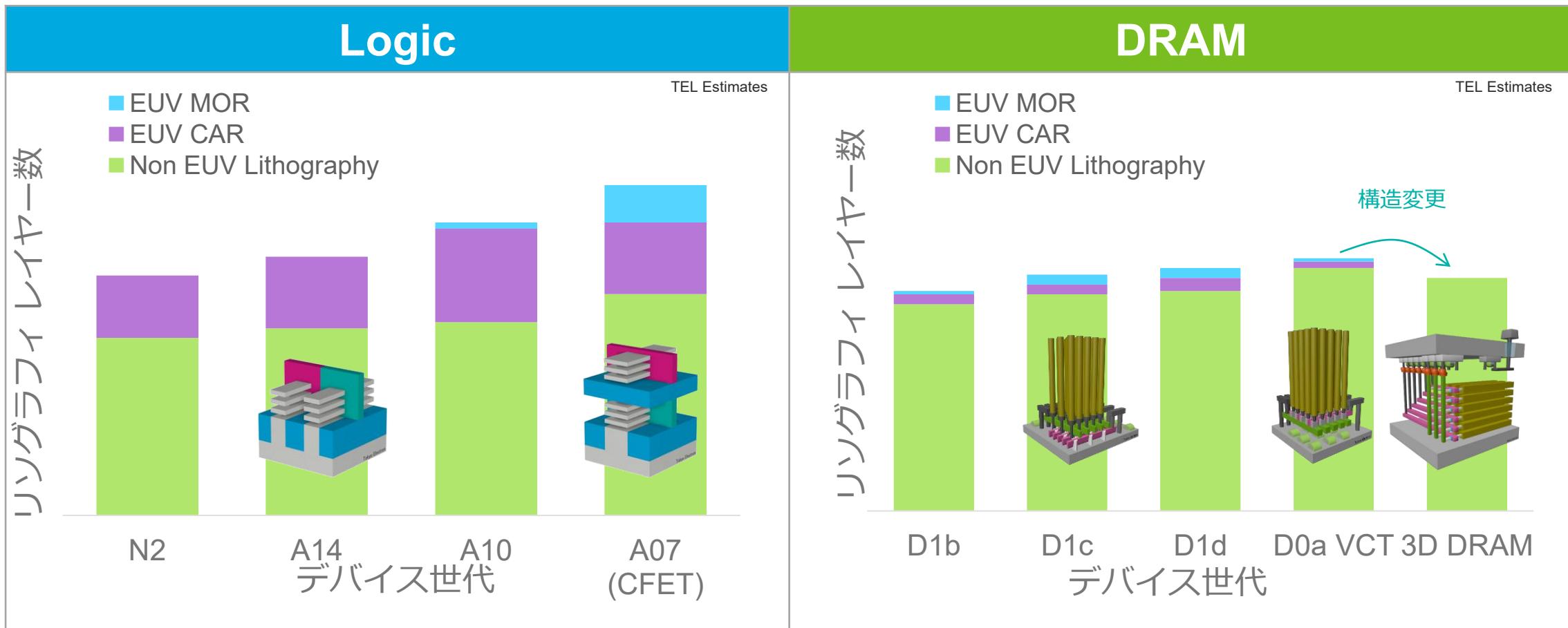

# リソグラフィレイヤー数の見通し

MORはLogic 10A、DRAM D1b世代に適用見込みにつき、MOR対応技術開発中

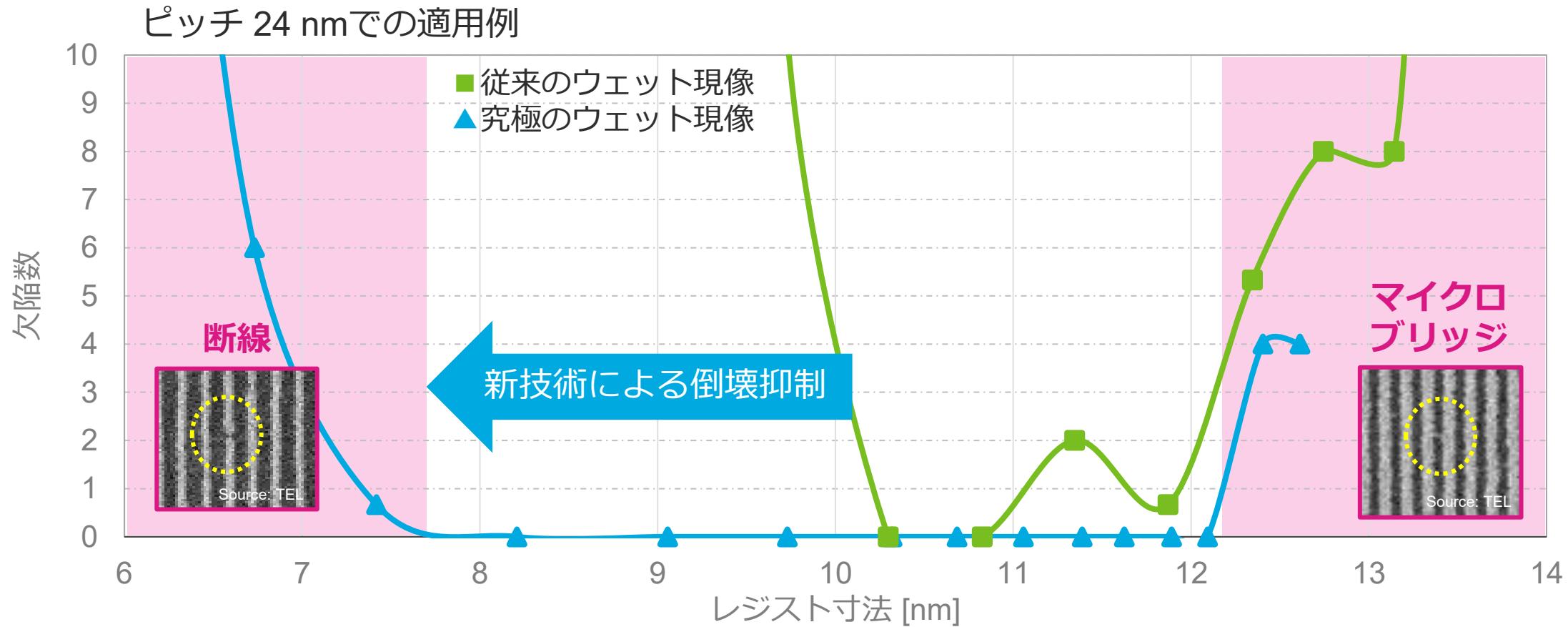

# MORソリューション：究極のウェット現像技術

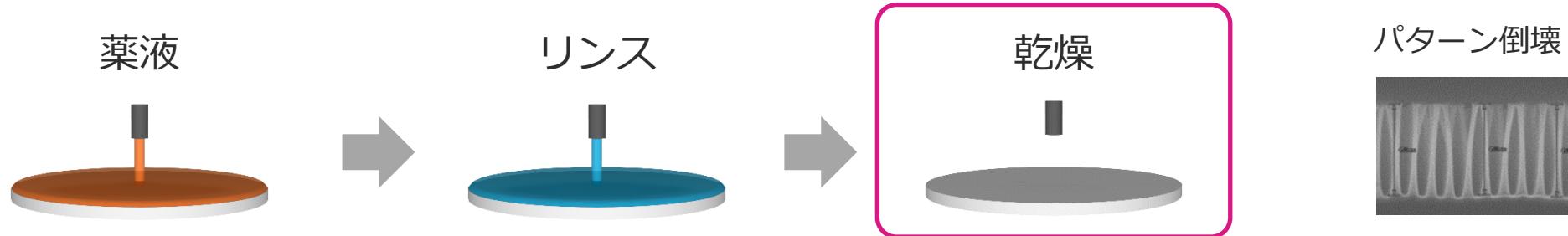

究極のウェット現像技術を適用することで従来ウェット現像の課題であったパターン倒壊の抑制を実現

# MORソリューション：究極のウェット現像技術開発

\*1 当社認識および開発ターゲットに基づく特徴づけ

\*2 ピッチ 24 nm ライン形成時の実施例に基づく特徴づけ

|                        | 究極の<br>ウェット現像技術      | 従来の<br>ウェット現像技術       | 代替技術                     |

|------------------------|----------------------|-----------------------|--------------------------|

| ベース技術                  | コーナ/デベロッパ            | コーナ/デベロッパ             | エッチング装置                  |

| 環境                     | 大気                   | 大気                    | 減圧                       |

| 反応                     | 薬液                   | 薬液                    | 腐食性ガス                    |

| スループット <sup>*1</sup>   | x 4                  | x 4                   | x 1                      |

| 薬液使用量 <sup>*1</sup>    | 50% (従来比)            | 100 %                 | N/A (ガス使用)<br>使用後は燃焼除害処理 |

| パターン倒壊性能 <sup>*1</sup> | < 8 nm <sup>*2</sup> | > 10 nm <sup>*2</sup> | < 8 nm <sup>*1</sup>     |

| 追加スペース <sup>*1</sup>   | インライン組み込み可能          | インライン組み込み可能           | 必要                       |

量産性（スループット・フットプリント・メンテナンス性・既存設備使用）を考慮した

究極のウェット現像技術を主要顧客と評価中

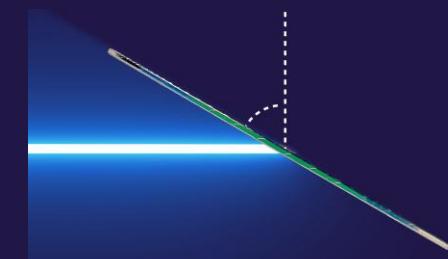

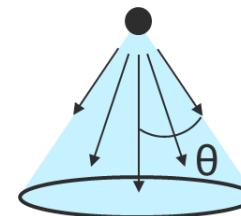

# Acrevia™

## TEL独自のGas Cluster Beam (GCB) System

- ビーム入射角を自由に調整可能

- LSP (Location Specific Processing) ウエーハスキャン

→ 縦・横・高さのエッチング制御が可能

- ✓ 微細パターンにおけるEUV露光回数削減

EUV装置の生産性を大幅に向上

- ✓ 微細パターン間の欠陥除去、LER/LWR\* 改善

歩留まり向上を実現

\* LER/LWR: Line Edge Roughness / Line Width Roughness

### Too Narrow

1<sup>st</sup> EUV

2<sup>nd</sup> EUV

Etch

### Wide

1<sup>st</sup> EUV

Acrevia™

Etch

生産性

x 2

## 7-2. 前工程 ユニットプロセス

## 7-2-1. エッチング装置

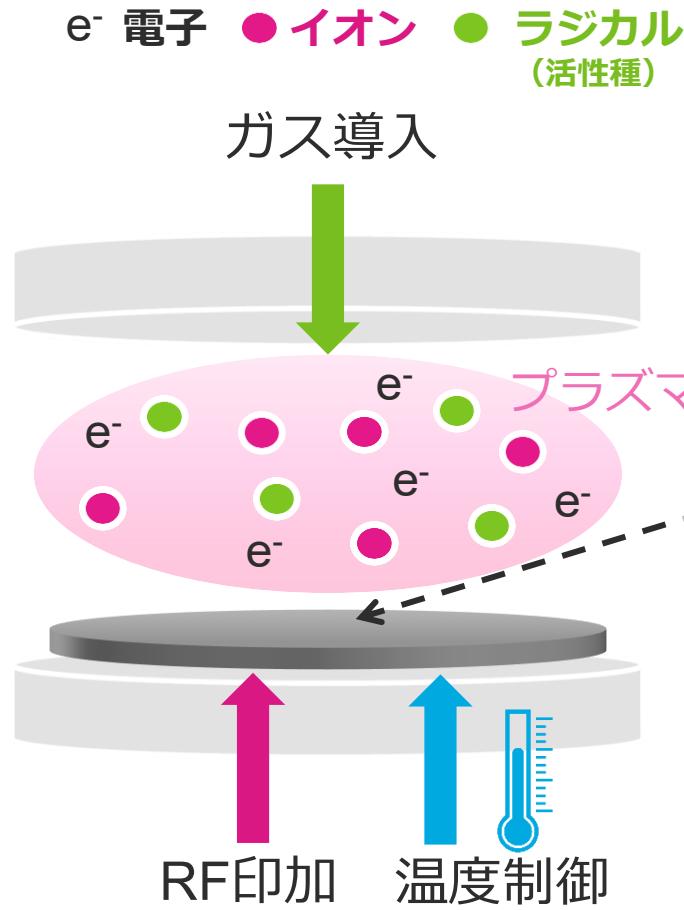

# 多様なエッチングと求められる技術

デバイスの更なる進化には、エッチングの緻密な制御技術が必要

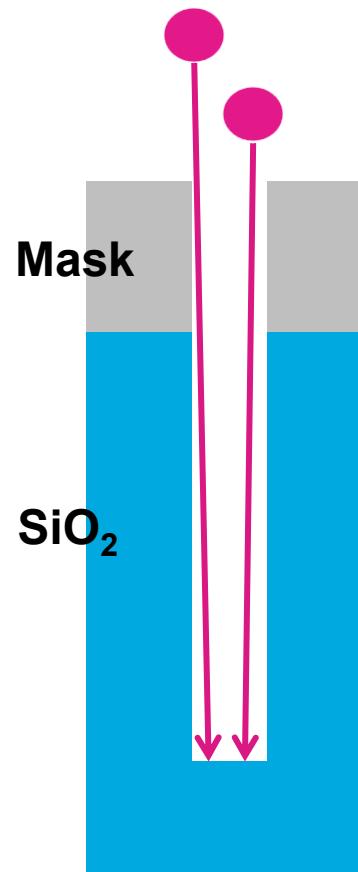

# エッチング概要とKeyとなる制御パラメーター

## Key制御パラメーター

### イオン輸送

Mask

SiO<sub>2</sub>

- ・ イオンエネルギー

- ・ イオン入射角

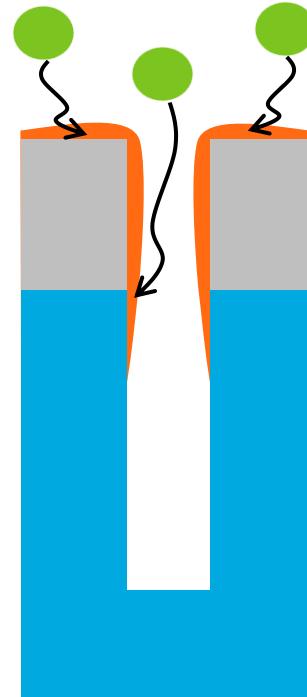

### ラジカル輸送

- ・ ガス種

- ・ ウェーハ温度

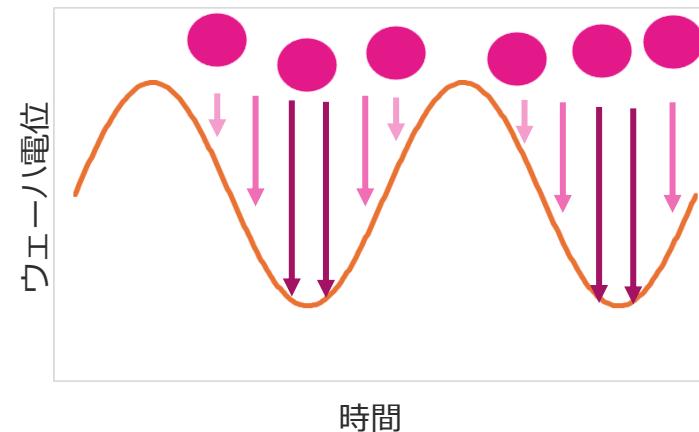

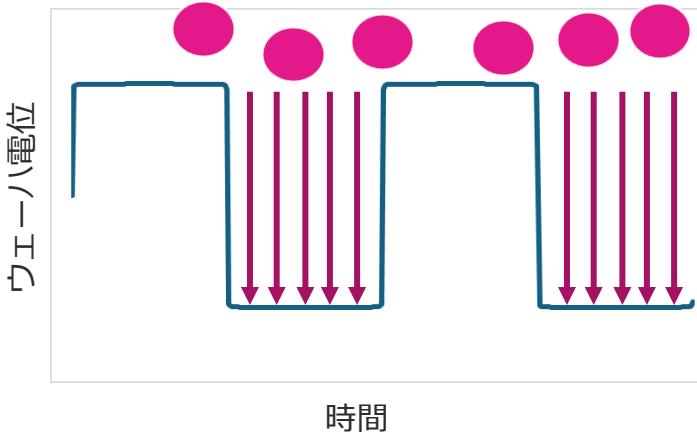

# TEL独自技術によるソリューション 1: HERB™

## イオン輸送

## 従来技術（正弦波）

イオンを引き込む力がばらつく

=入射角がばらつく

(HERB™: High Efficiency Rectangular Bias™)

## 新技術（HERB™）

イオンを引き込む力が強く一定

=入射角も垂直化

# TEL独自技術によるソリューション 2: PHastIE™

## ラジカル輸送

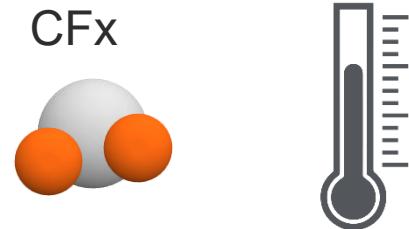

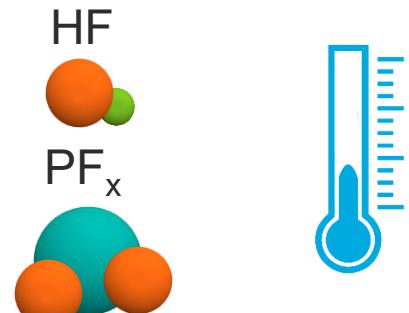

## 従来技術 ( $CF_x$ + 常温)

$CF_x$ はポリマー化して吸着しやすい

間口に堆積すると輸送を阻害

## 新技術 (PHastIE™)

新規ガスを採用することで上記課題を克服

低温との組み合わせで高速Etchingを実現

(PHastIE™: Phosphorus + Hydrogen based “Fast” Ion Etch™)

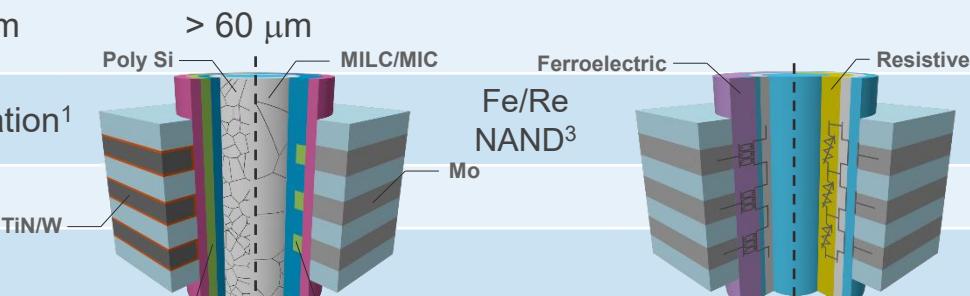

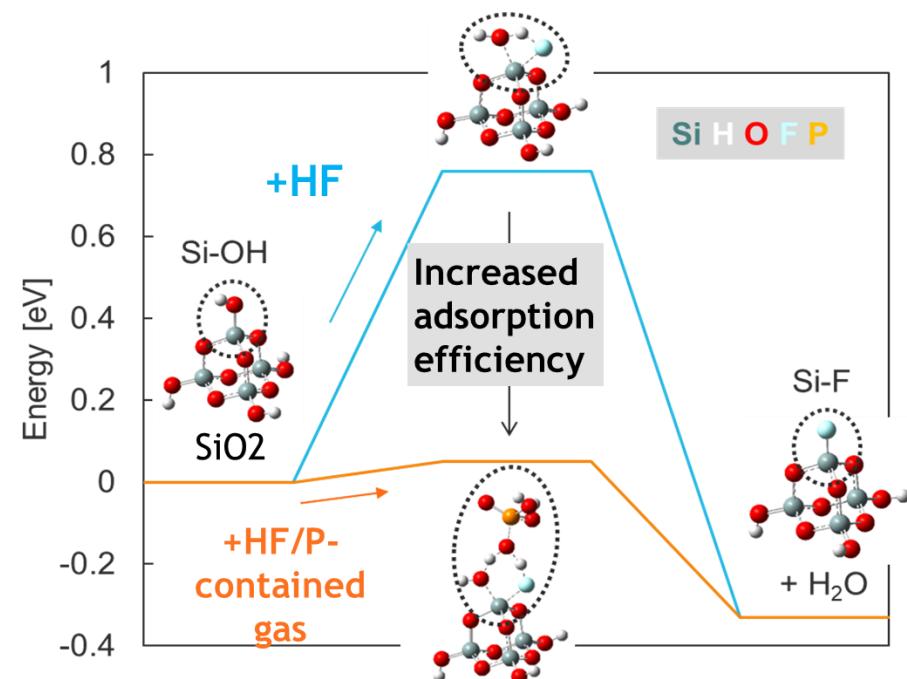

# Novel Cryogenic HARC Etch

Beyond

**10 μm**

2.5x Faster

A large green downward-pointing arrow is positioned to the left of the text, indicating a comparison or result of the technology.

世界初、新Cryogenicプロセスを2023年に発表 (@VLSI 2023)

高いプロセス性能と環境性能を両立

## プロセス性能

### 極低温プロセス

より直線的、

より深く、

より速く

### プラズマ制御

深層学習を用いた最適化

## 環境性能

### 消費電力 -43%

Less Power

### CO<sub>2</sub>排出量 -83%

Less Carbon Footprint

# 新たなエッチング技術の展開

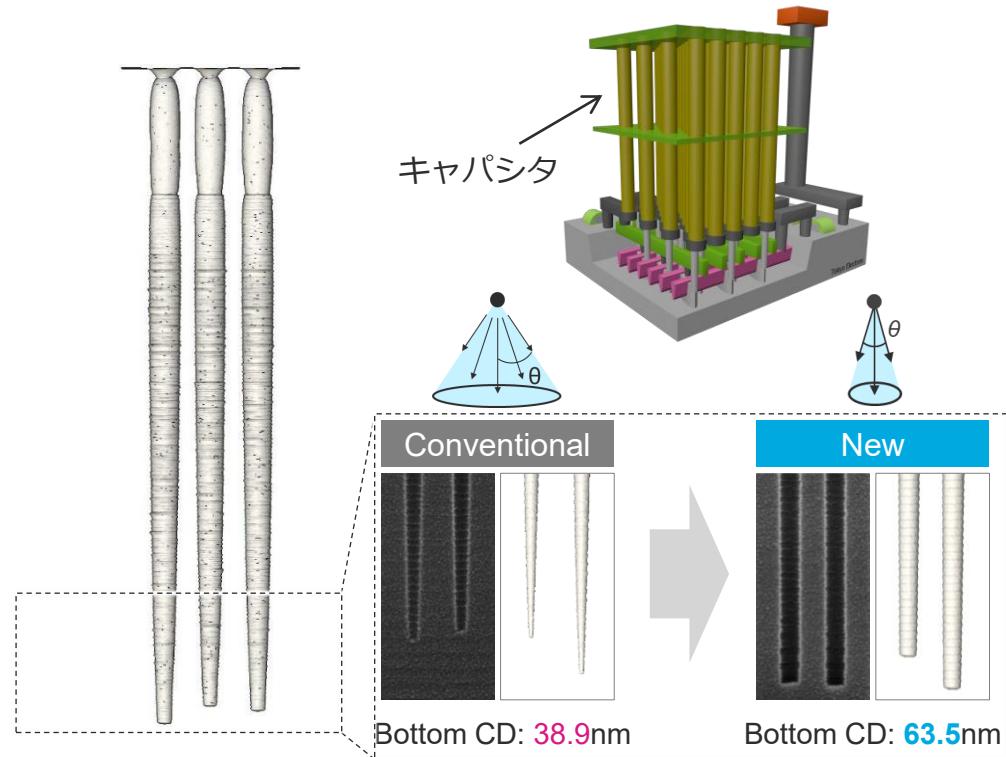

## DRAM: Capacitor SiO<sub>2</sub>加工

## Logic: Gate Silicon加工

理想のエッチングプロセス開発で培った新技術を

多様なCriticalプロセスにも展開

# ロジックにおける事業機会

\*1 GAA: Gate all around

\*2 SAMP: Self-aligned multiple patterning

\*3 PDN: Power delivery network

微細化が進むことによるデバイス構造の変化やEUVリソグラフィーに対応

TEL

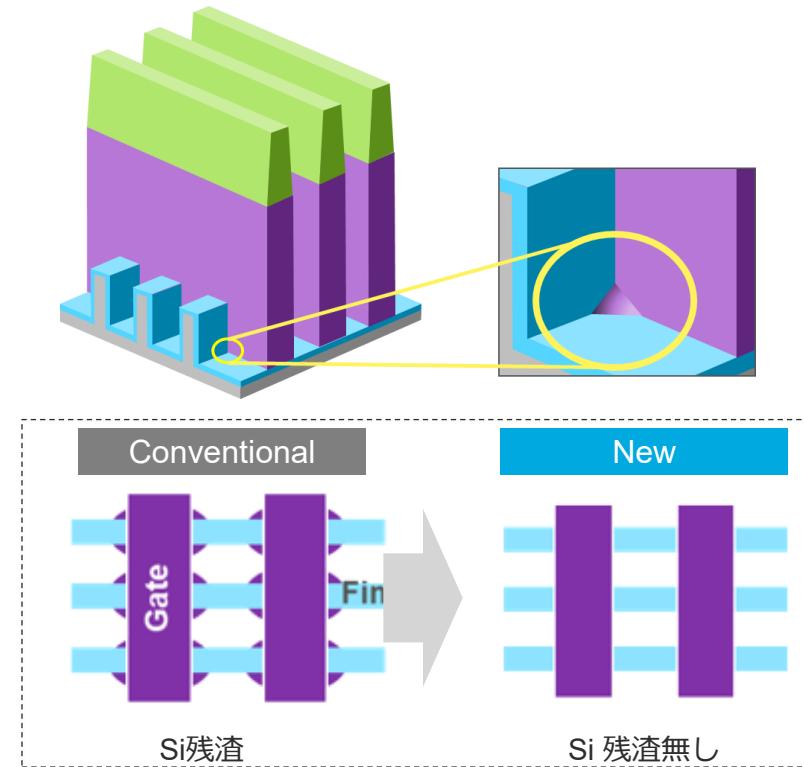

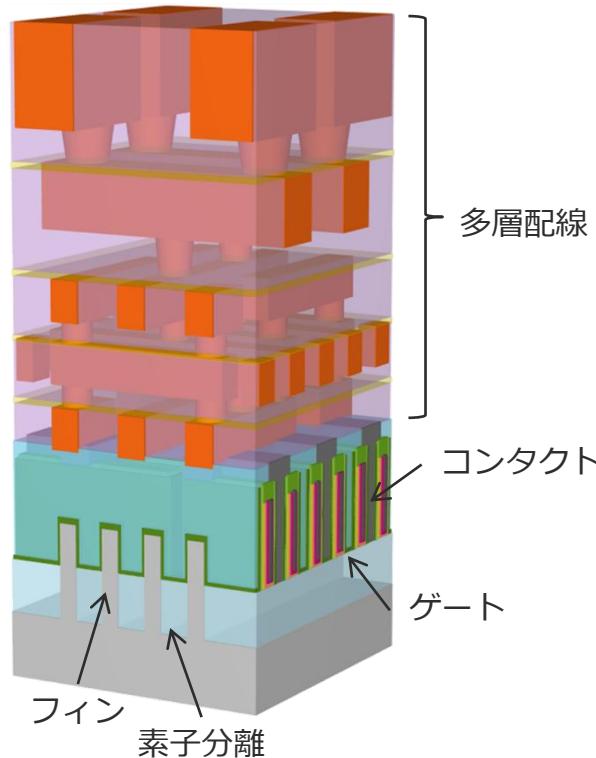

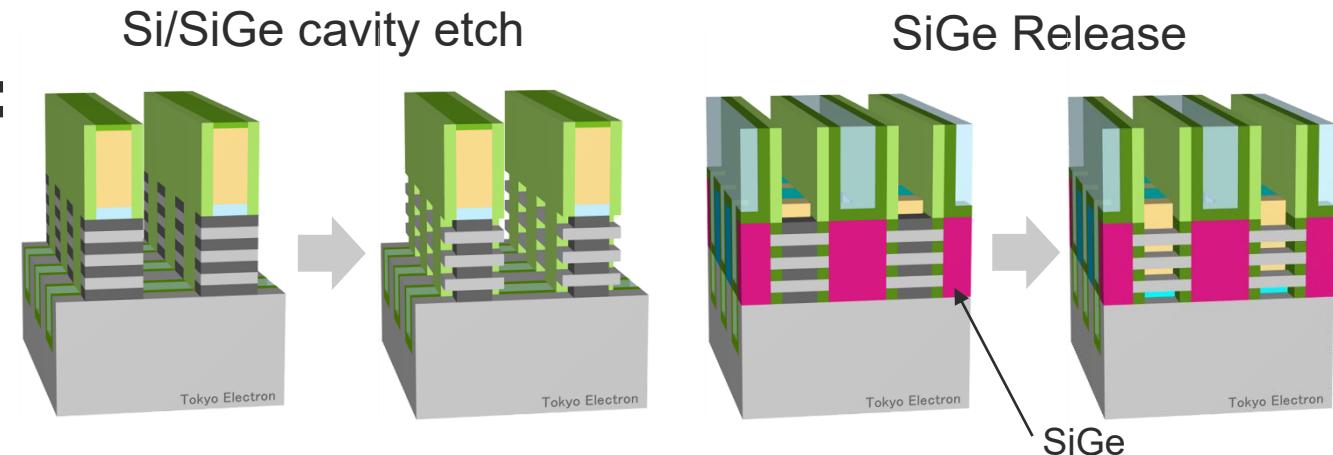

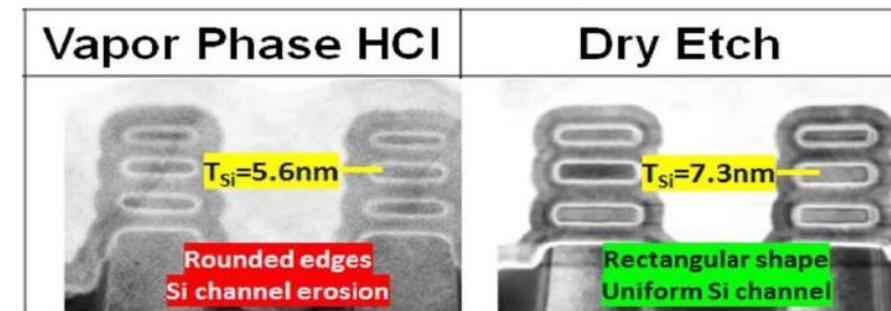

# GAA Nano Sheet FET構造への取り組み

## GAA Nano Sheetプロセスの課題：

- パターン形状（矩形）の均一性

- パターン表面のラフネス・残渣

## TELの取り組み：ガスケミカルエッチング

- 高いエッチング選択性

- 高い均一性

- 残渣除去・ラフネス低減

Source: N. Loubet, et al., IBM, TEL Technology Center, America (IEDM2019)

ガスケミカルエッチングのメリットを生かして先端プロセスへ貢献

## 7-2-2. 成膜装置

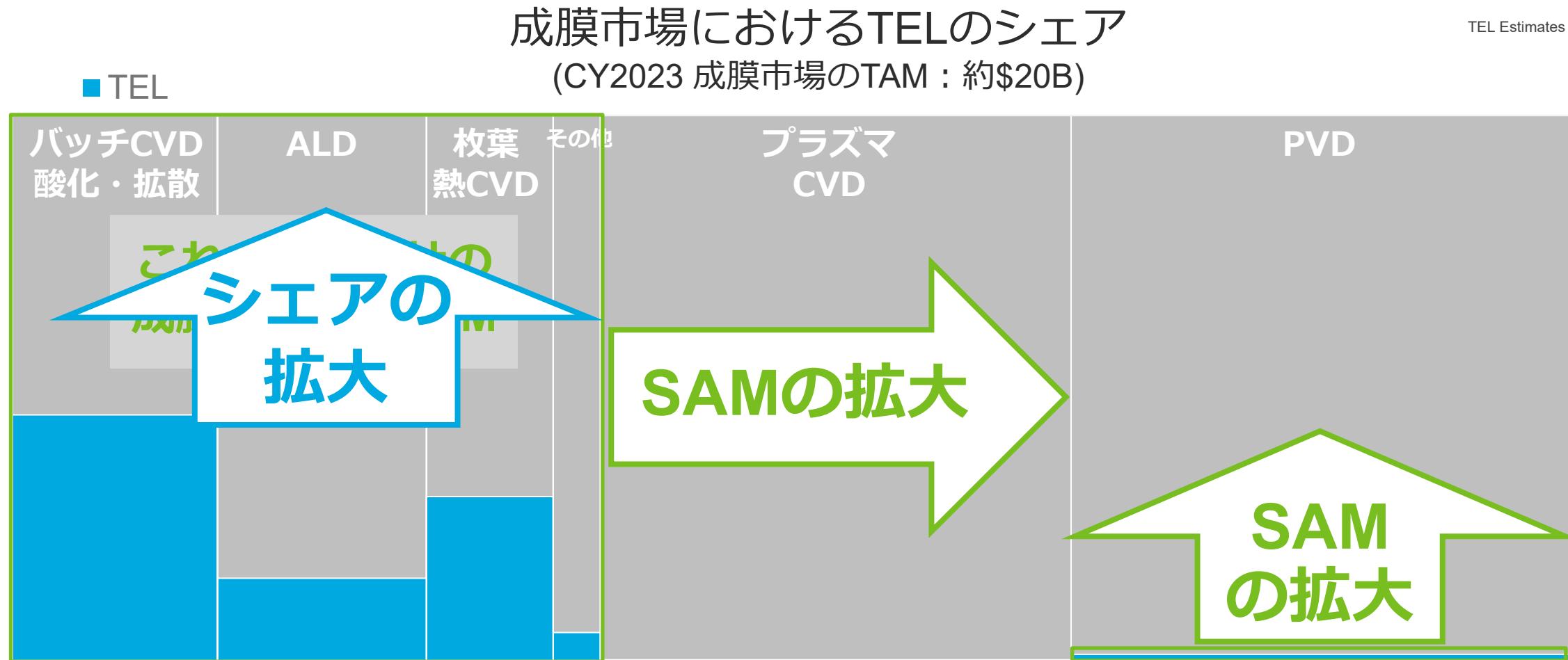

# 成膜における事業戦略：シェアの拡大・SAM\*の拡大

# 成膜ビジネスにおける戦略 1：枚葉CVD成膜装置のSAMの拡大

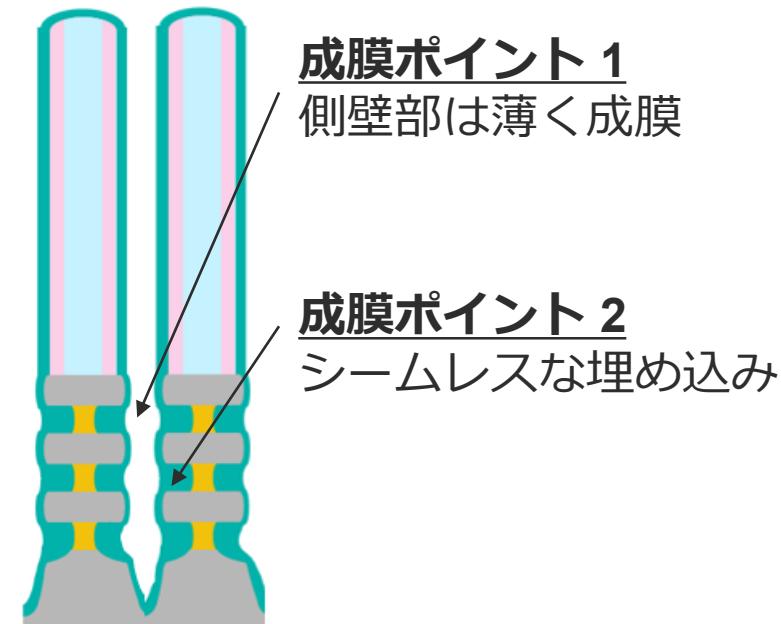

Triase<sup>TM</sup>

**Single Reactor**

既存プラットフォーム

Episode<sup>TM</sup> 1

**Single Reactor**

最大8基のプロセスモジュール搭載

Episode<sup>TM</sup> 2 DMR\*

**\*Duo Matched Reactor** \*\*Quad Matched Reactor

2枚葉で高い生産性を実現

新開発高密度プラズマ源搭載

2024年7月リリース

Episode<sup>TM</sup> 2 QMR\*\*

2026年リリース予定

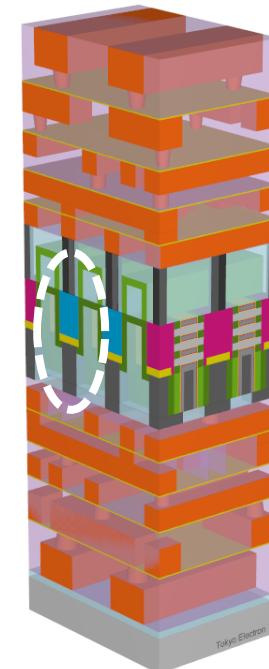

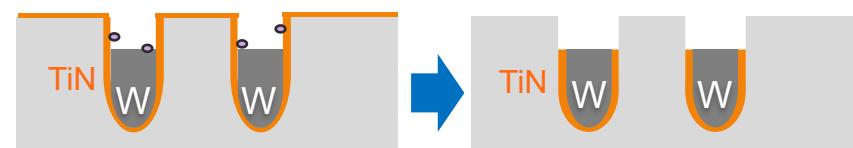

# Episode™ 1：コンタクト形成工程

- プロセスフローの一例

\*1 COR: Chemical Oxide Removal

\*2 PHT: Post Heat Treatment

高真空度の同一プラットフォーム上で酸化膜除去工程とメタル成膜を連続処理

⇒コンタクトの低抵抗化実現に寄与

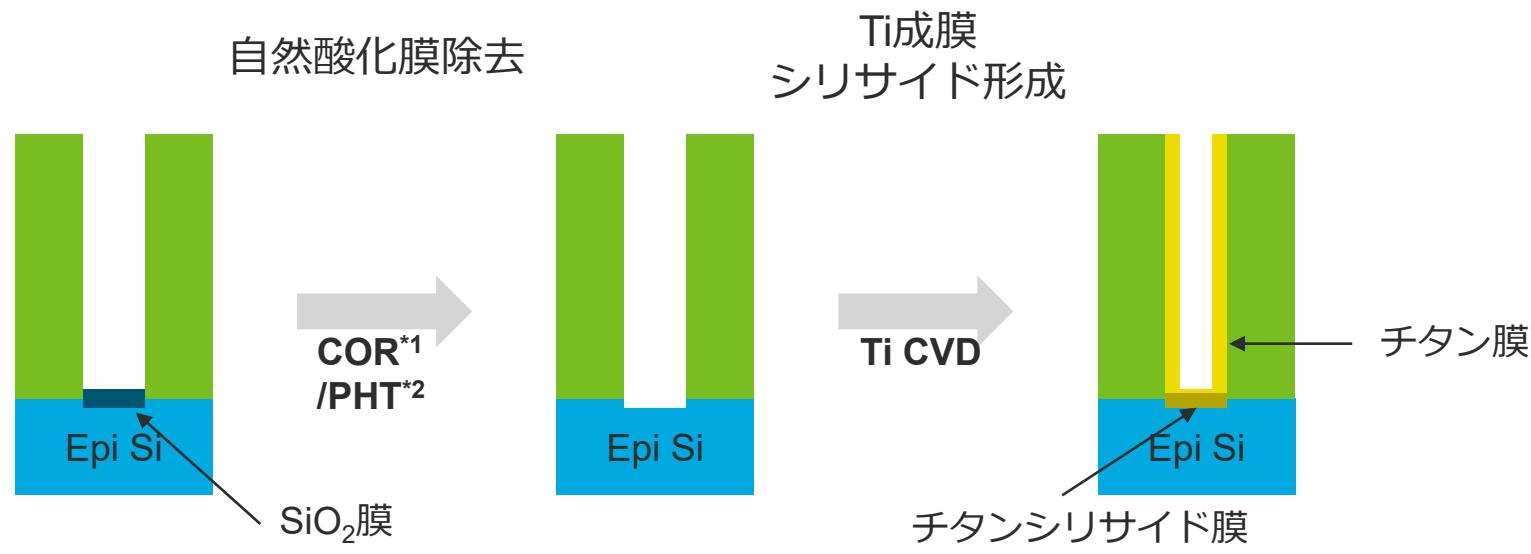

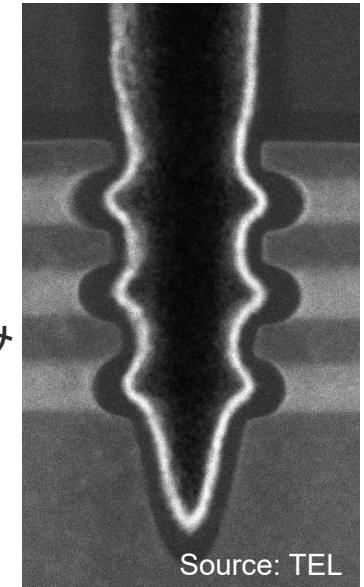

# Episode™ 1 : Inner Spacer工程—横方向の埋め込み性

## ■ 技術課題 :

成膜後のエッチングによるリーク発生懸念

## ■ 解決策 :

埋め込み性能の改善

ユニークな成膜手法によるシームレスな埋め込みと

新開発の高密度プラズマによる横方向に均一な膜の改質を実現

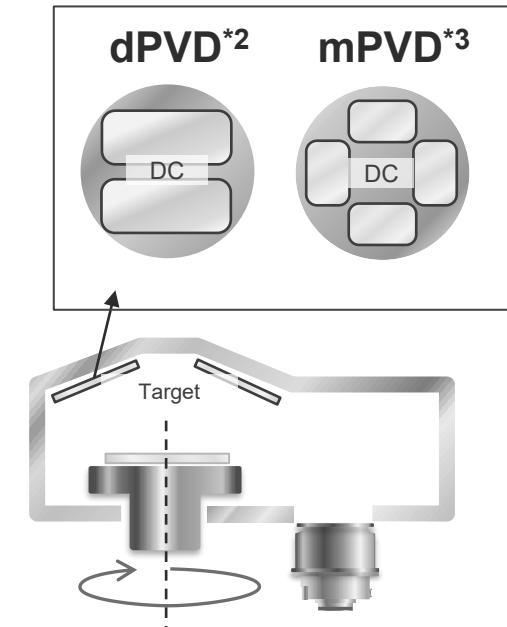

# 成膜ビジネスにおける戦略 2 : PVD装置におけるSAM拡大

LEXIA™ -EX    2024年12月リリース

- ウエーハ回転機構を備えた斜め入射PVD装置

(Oblique Angle Sputtering)

- 良好な膜厚均一性 ( $1\sigma$  0.5%)

- 独自のマルチカソード<sup>\*1</sup>仕様

- 高い成膜率を実現

- 複数材料による組成比制御が可能

- 高い生産性を実現 (~100WPH)

- 従来機種から大幅な省スペース化を実現

\*1 カソード: 成膜材料を取り付ける電極

\*2 dPVD: Dual cathode PVD

\*3 mPVD: Multiple cathode PVD

# 成膜ビジネスにおける戦略 3：縦型熱処理/成膜装置での成長

## ■ 主要アプリケーション

- Siプロセス全般 (ダミーゲート、チャネルSi, etc.)

- Batch ALD high-k (キャパシタ絶縁膜)

- Plasma/Thermal ALD-SiN/SiO<sub>2</sub>

- Batch molybdenum (word line)

TELINDY™ PE-II

## ■ 今後の開発計画

- ロードポートサイズアップ (8ロット、1バッチ200枚処理)

- 疎密差があるパターンにも均一な成膜するために、排気特性を改善

- 省エネの追求 (ヒーター性能のさらなる向上)

- 省人化 (One-Touch立上げ、セルフメンテナンス、DXの活用)

## 7-2-3. 洗净装置

# 枚葉洗浄における戦略

## ■ 枚葉洗浄

### - ベベルウェットエッチング

- ・ 市場は年率10%程度の成長見込み

- ・ 顧客歩留まり改善に貢献。精密な外周部の膜除去性能により差別化し、高いシェアを維持

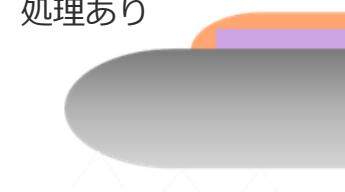

処理なし

処理あり

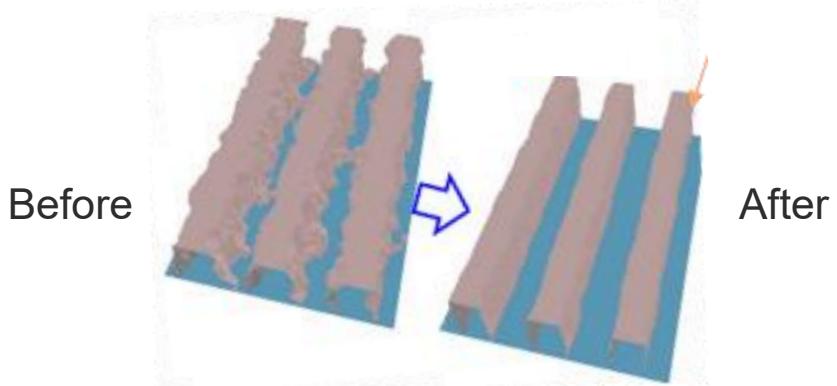

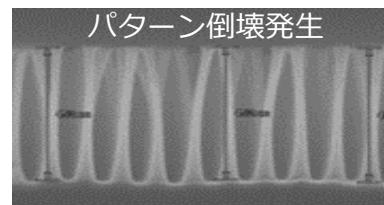

### - パターン倒壊抑制

高アスペクト比のパターンの倒壊を抑制する当社独自の技術により、シェアを拡大

既存乾燥技術

新乾燥方式

### - メタルエッチング

メタルとの選択比を制御する新規SPM専用チャンバーを販売開始。ドライエッチングのダメージや残渣による歩留まり低下の課題を解決

メタルエッチング工程イメージ

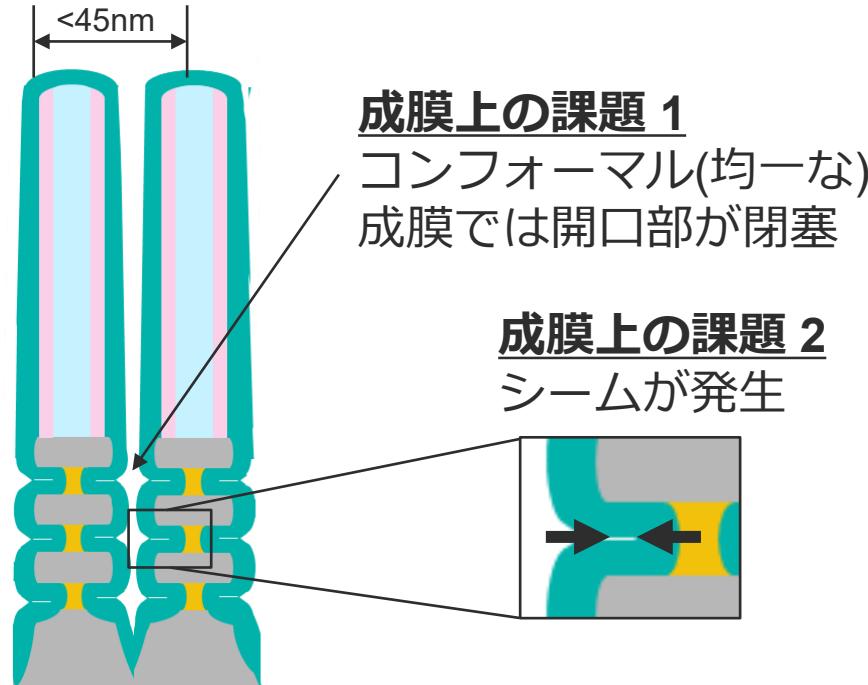

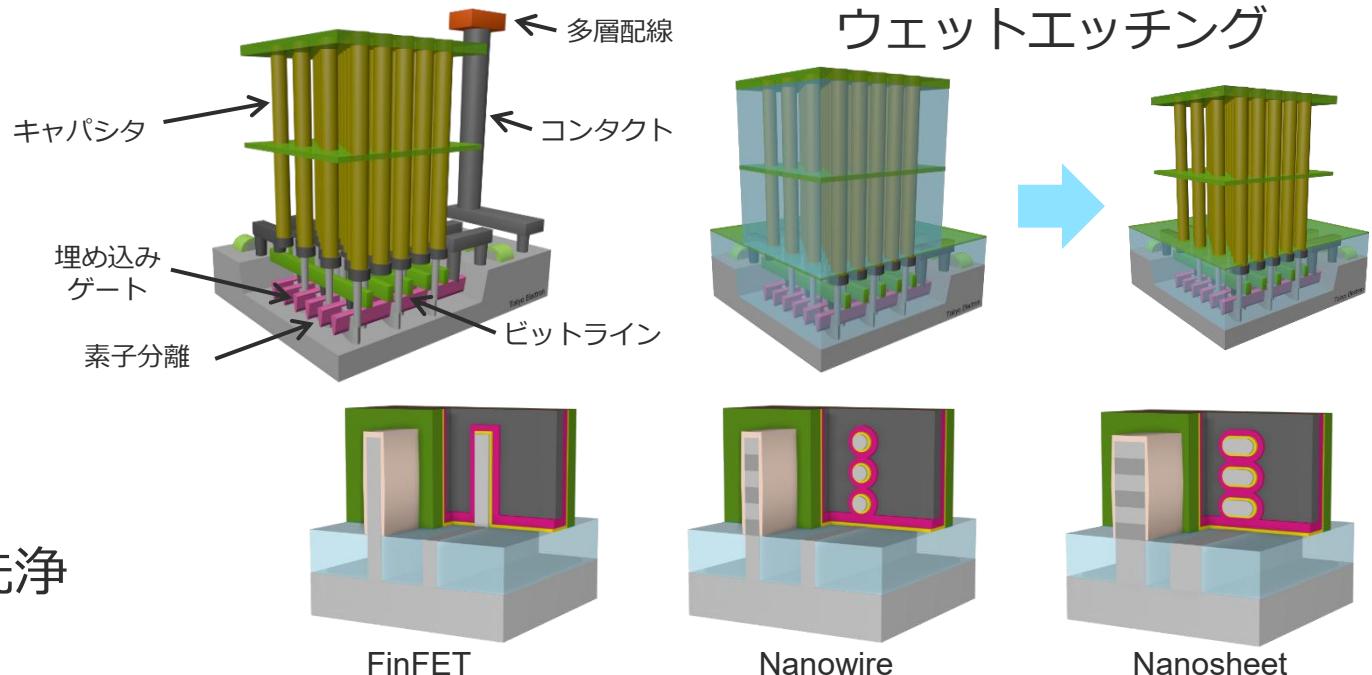

# 先端デバイスが抱える洗浄工程における技術課題

## ■ DRAM

- 素子分離エッチング後の洗浄

- キャパシタ電極形成後のモールドのウェットエッチング

## ■ ロジック

- Fin エッチング後の洗浄

- Nanowire/Nanosheet 形成後の洗浄

デバイス構造の微細化・高アスペクト比化により、乾燥技術の難度が増加

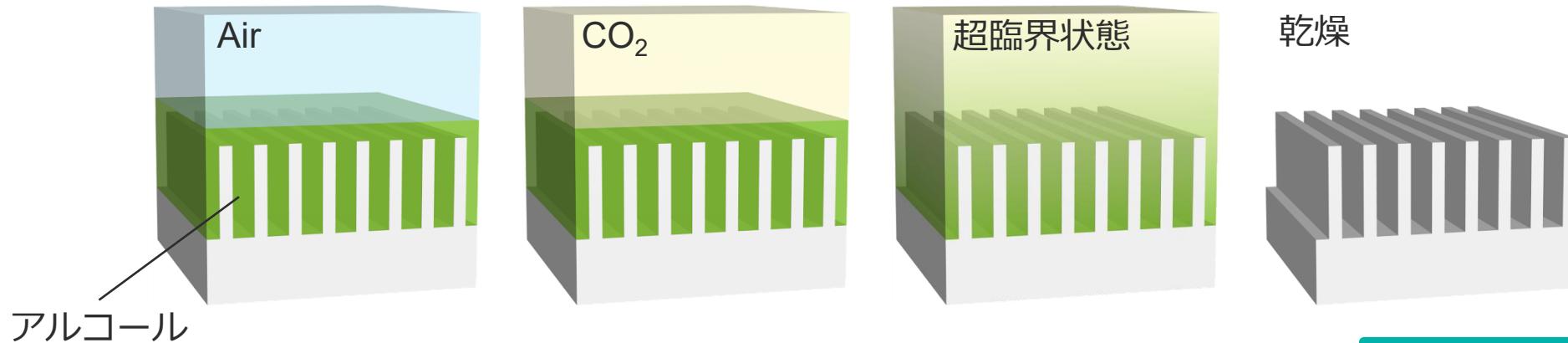

# 超臨界乾燥技術

|           | 従来の乾燥 | TELの超臨界乾燥 |

|-----------|-------|-----------|

| Top View  |       |           |

| Side View |       |           |

超臨界乾燥技術によりパターン倒壊を抑制

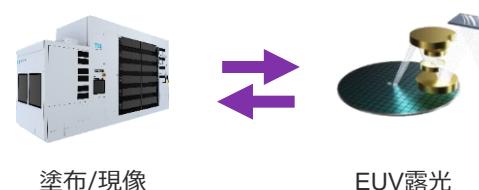

# バッチ・スクラバー洗浄における戦略

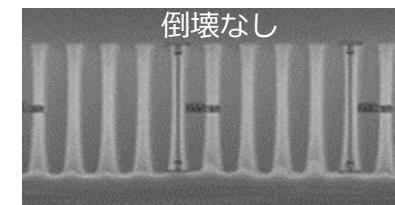

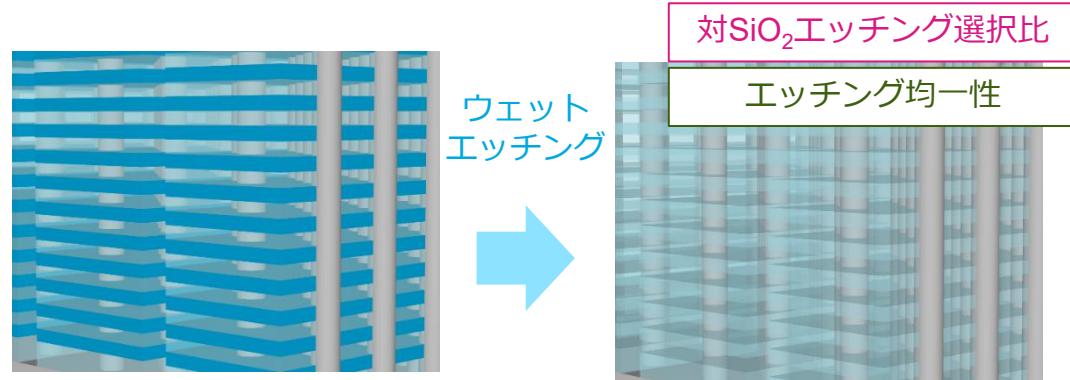

## ■ バッチ洗浄

- 3D NAND向けSiNエッティング、Wエッティング

長時間かつ高いプロセス技術が要求される工程に注力。ウェットエッティングにおける高均一性、高選択性および高生産性の実現により差別化

SiNエッティング工程イメージ

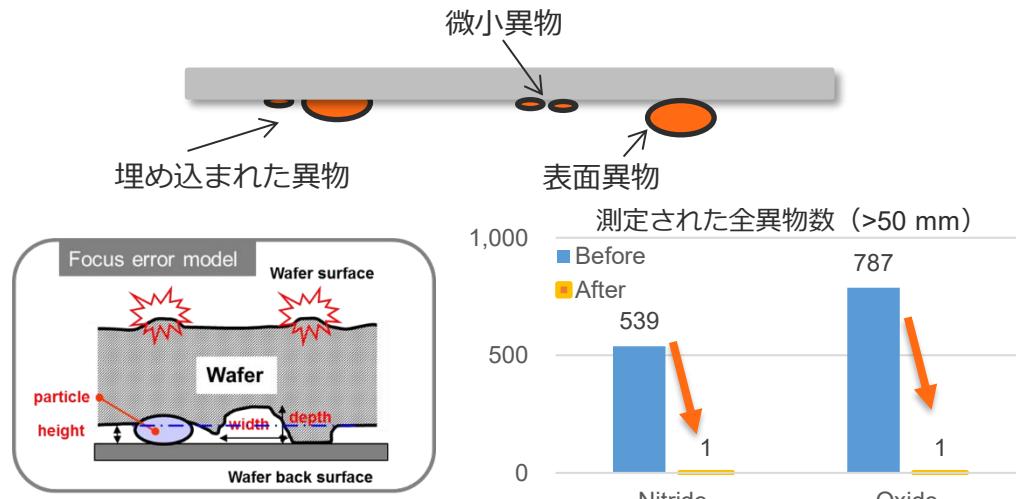

## ■ スクラバー洗浄

- Pre-lithography工程

EUVの導入によってますます重要度が増す

露光機の稼動率向上に貢献する、異物低減など、価値の高いソリューションを提供

ウェーハ裏面とディフォーカスのイメージ

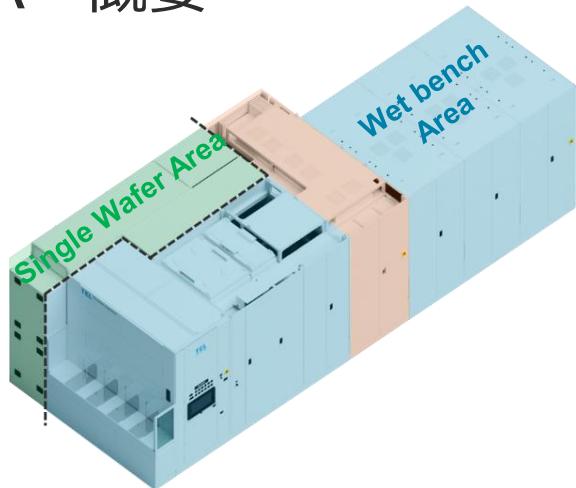

# ZEXSTA™

## ■ ZEXSTA™ 概要

Wet Benchと枚葉洗浄の

コンビネーション処理を提案

| 処理手法      | 特色                 |

|-----------|--------------------|

| Wet Bench | 高温・長時間処理、ウェットエッチング |

| 枚葉洗浄      | 高度な乾燥技術、パーティクル制御   |

## ■ Target Application

- 高度なウェットエッティングと高度な乾燥技術が求められる工程

3D NANDに加え、今後、DRAMの積層化にも伴い、

高度な選択等方ウェットエッティング技術が求められる

- 高生産性と表面清潔度の両立が求められる工程

Wet Bench

LogicやDRAMにおいて、高度な表面清潔度が求められる

これまでの装置区分に捉われること無く、新たな価値創造にChallengeし、顧客技術開発に貢献します

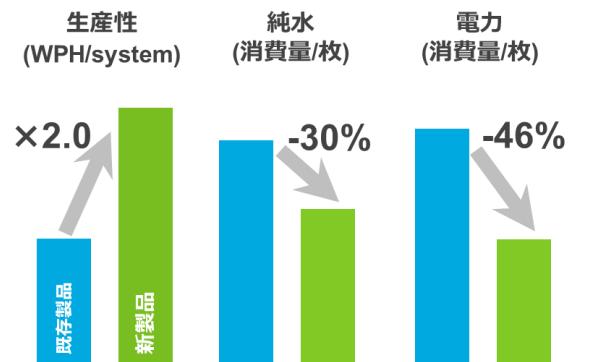

# 洗浄装置開発取り組み

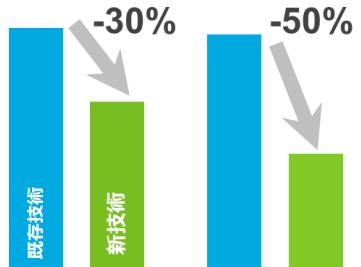

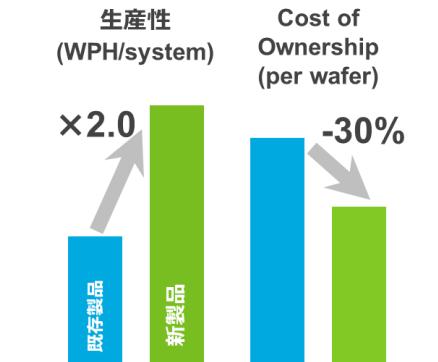

## 高生産性Wet Bench (EXPEDIUS™-R)

業界初Large Batch処理（一度に処理する枚数を拡大）を実現する装置

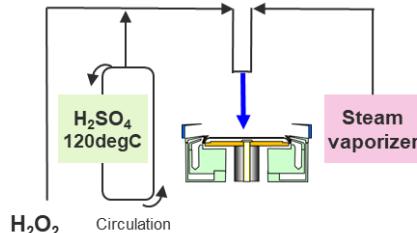

## SPM<sup>\*1</sup> Vapor技術 (CELLESTA™ Pro VP)

薬液に水蒸気を添加し、効率的な化学反応により処理温度の高温化を実現

\*1 SPM : Sulfuric Acid and Hydrogen Peroxide Mixture

薬液処理時間 薬液消費量/枚

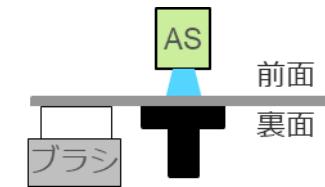

## 両面スクラバ (CELLESTA™ MS2)

Wafer表面のAS<sup>\*2</sup>処理、Wafer裏面のBrush処理を一つのChamberで同時処理が可能

\*2 AS : Atomized Spray

## 7-3. 後工程 事業戦略

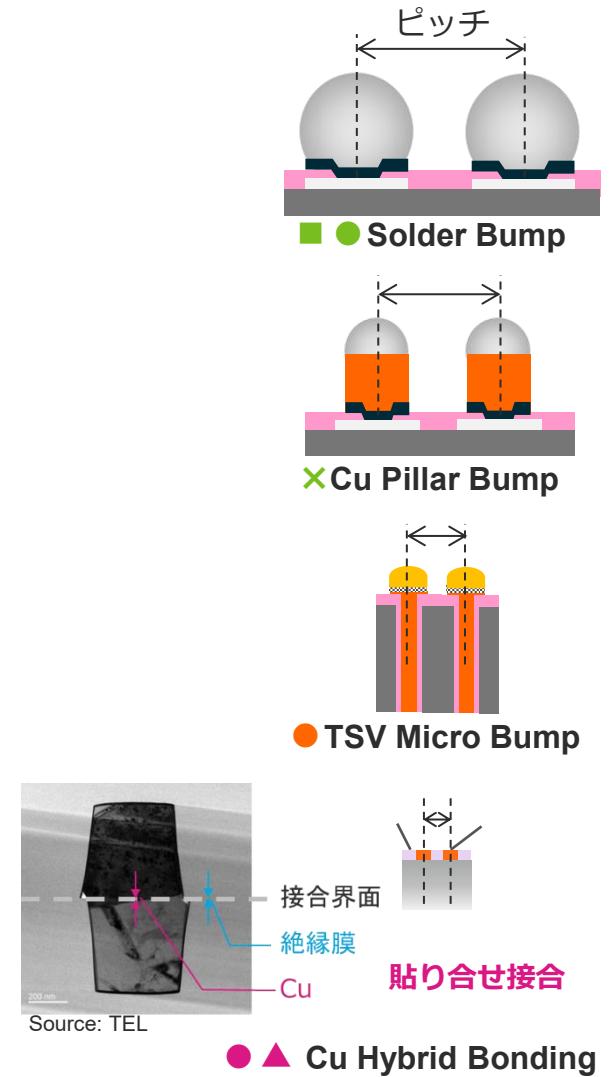

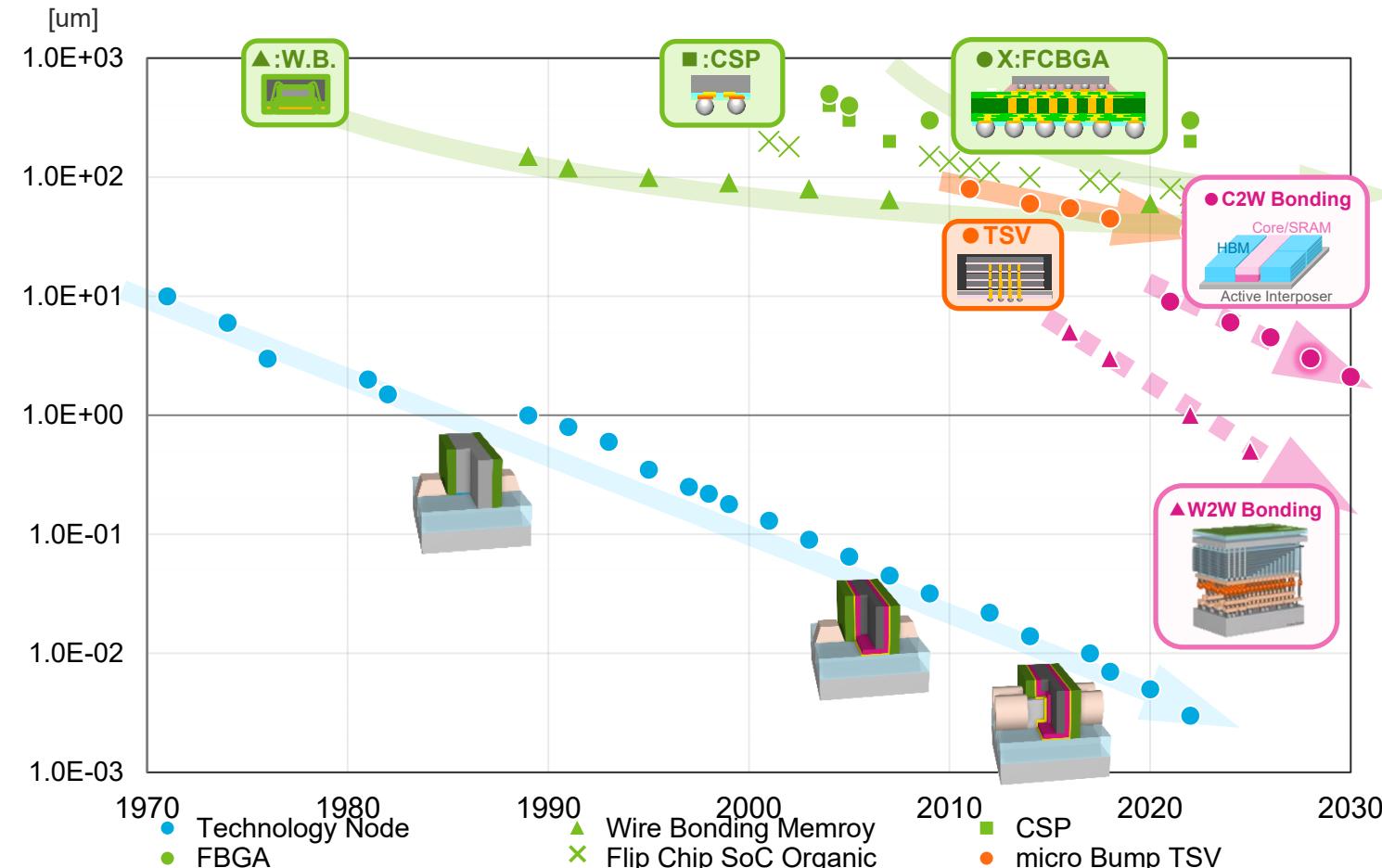

# 半導体テクノロジーノードと実装電極ピッチ

貼り合わせ接合技術の導入が、実装電極ピッチのさらなる縮小を加速

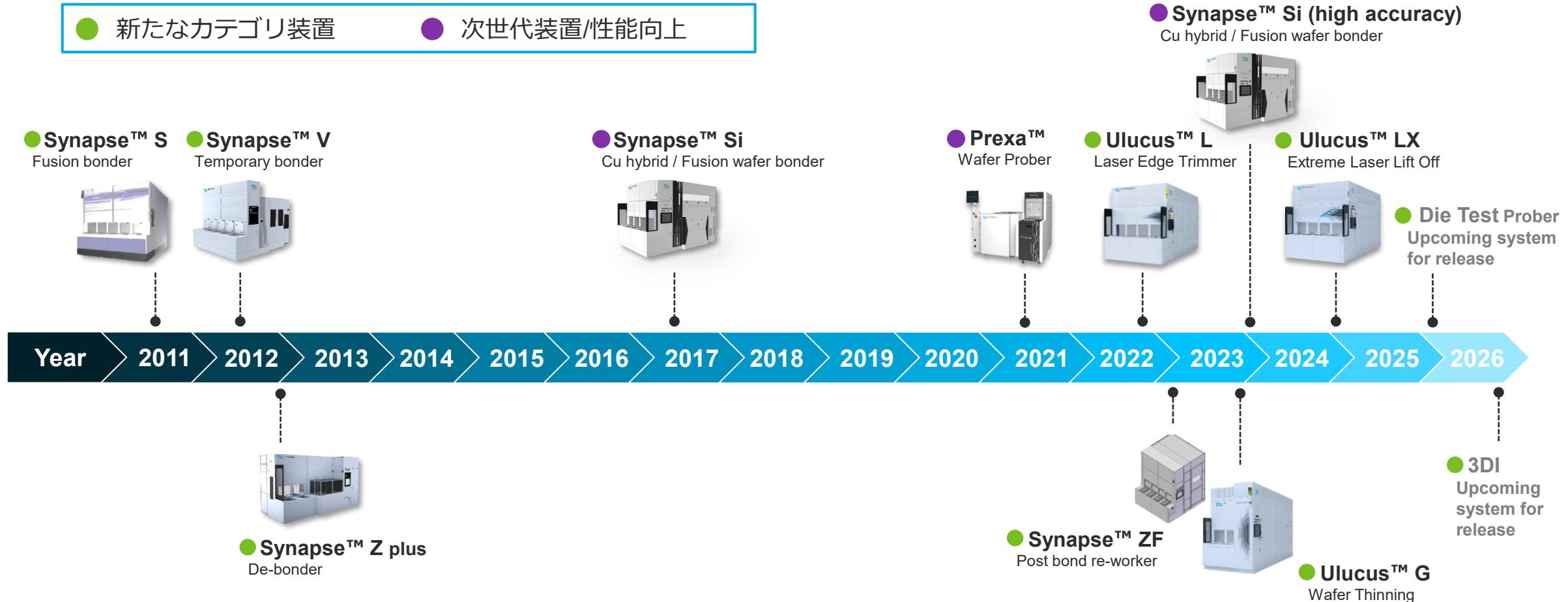

# アッセンブリー・テスト\*向け製造装置投入の歴史

3Dインテグレーション時代へ向け、新装置/次世代装置開発を加速

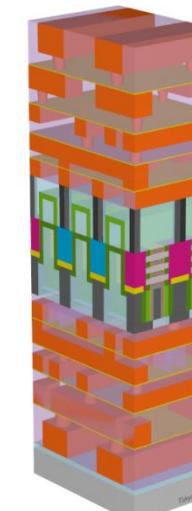

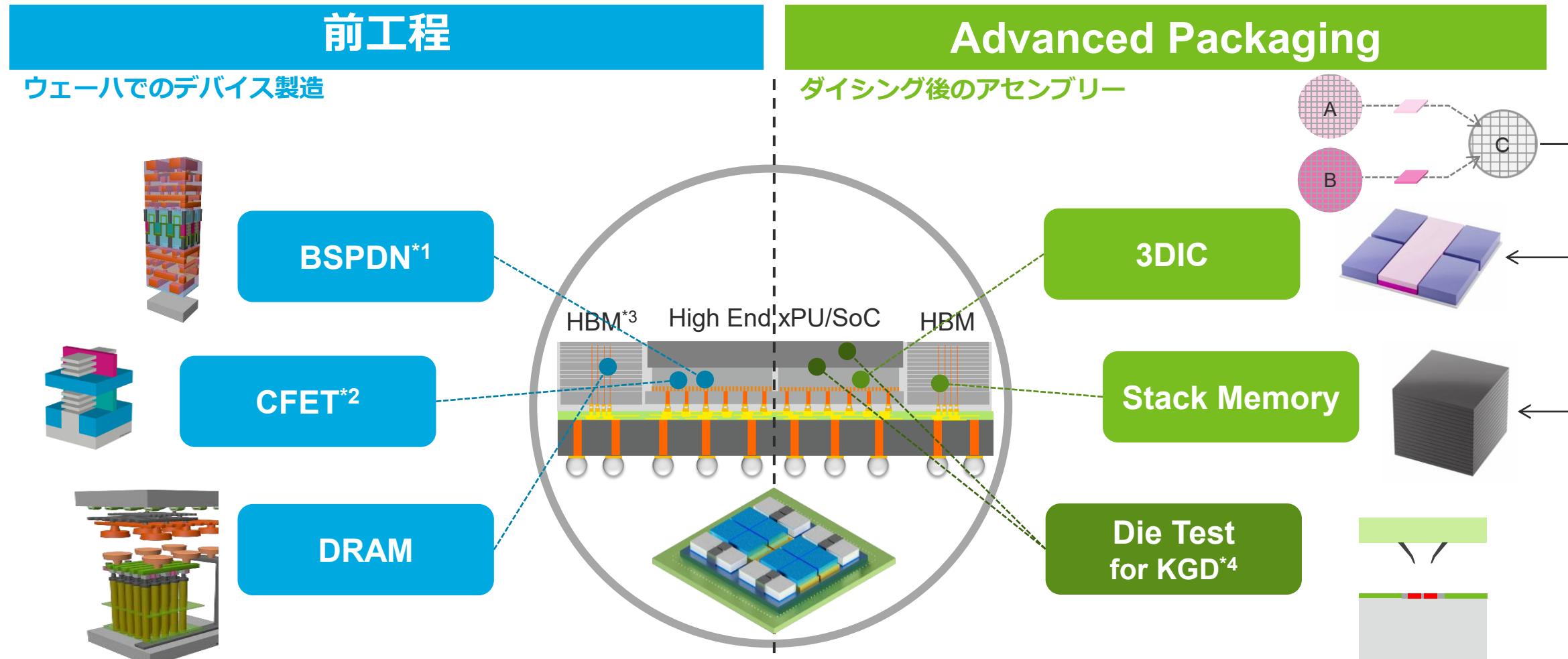

# HPC/AIデバイスにおける3DI/テストの事業機会

\*1 BSPDN: Backside Power Delivery Network

\*2 CFET: Complementary Field Effect Transistor

\*3 HBM: High Bandwidth Memory

\*4 KGD: Known Good Die

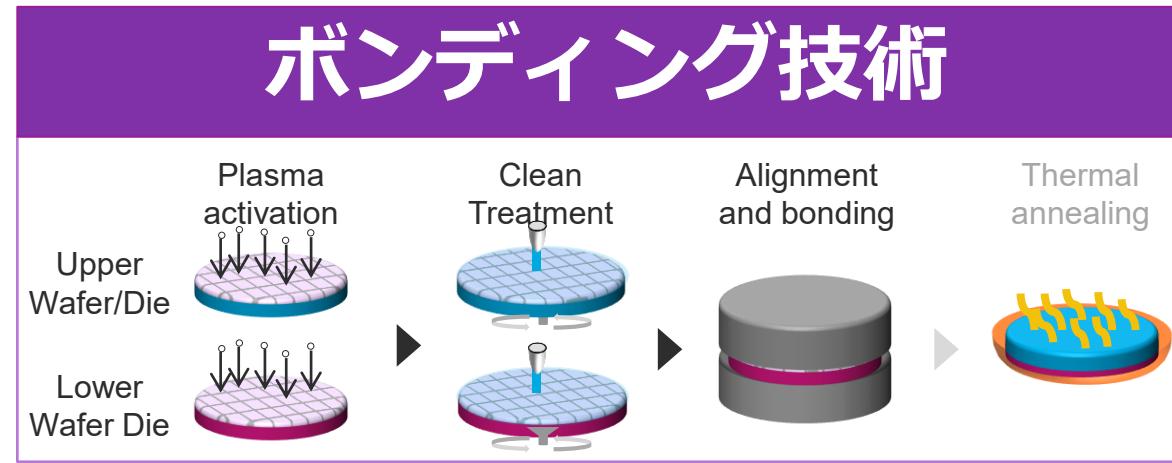

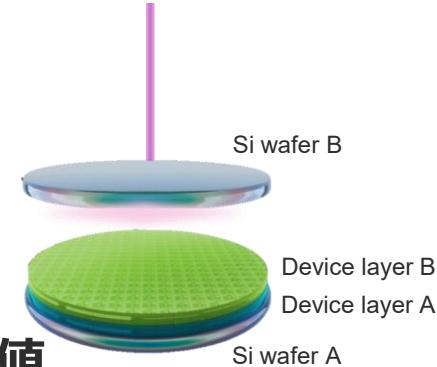

# ボンディング技術における当社の事業機会

Wafer-to-Wafer Bonding

Wafer-to-Wafer Bonding

Die-to-Wafer Bonding

利点：ピッチスケーリング、高速化、低消費電力化

前工程

Advanced

Packaging

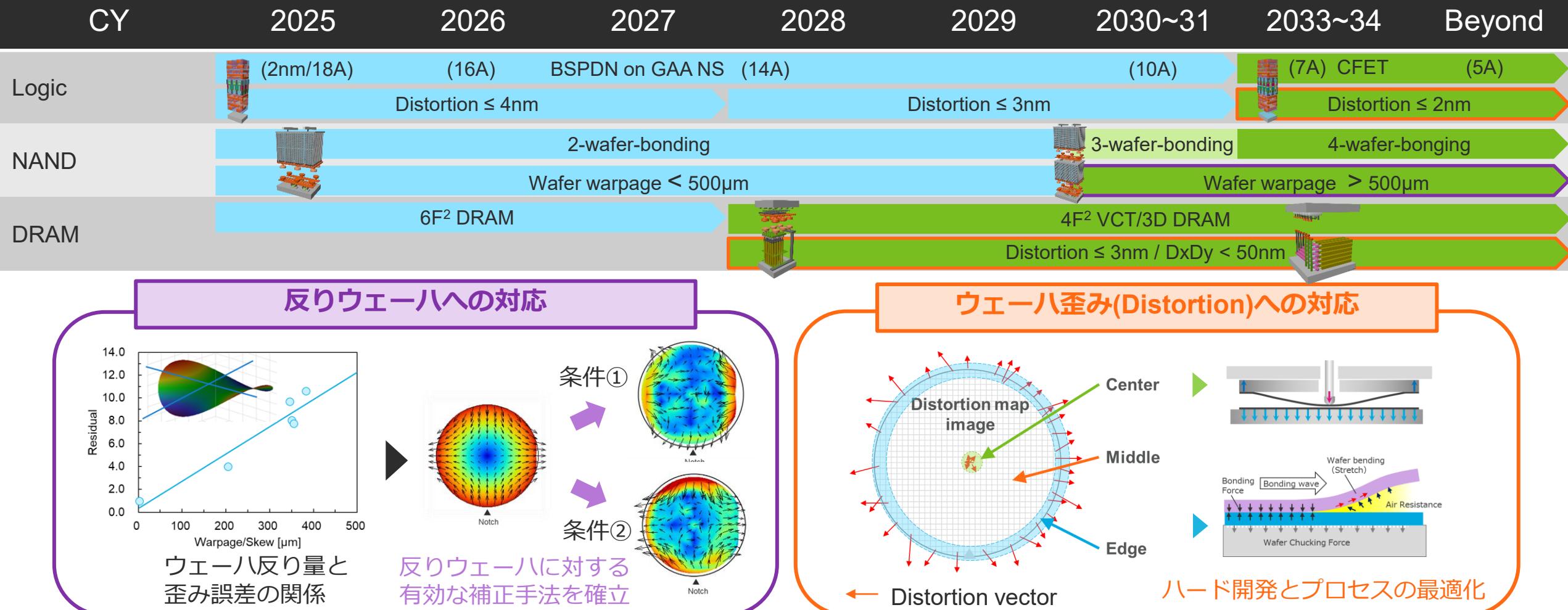

# ウェーハボンダーの技術ロードマップと課題

次世代デバイス対応として必要な様々な技術を先行して開発中

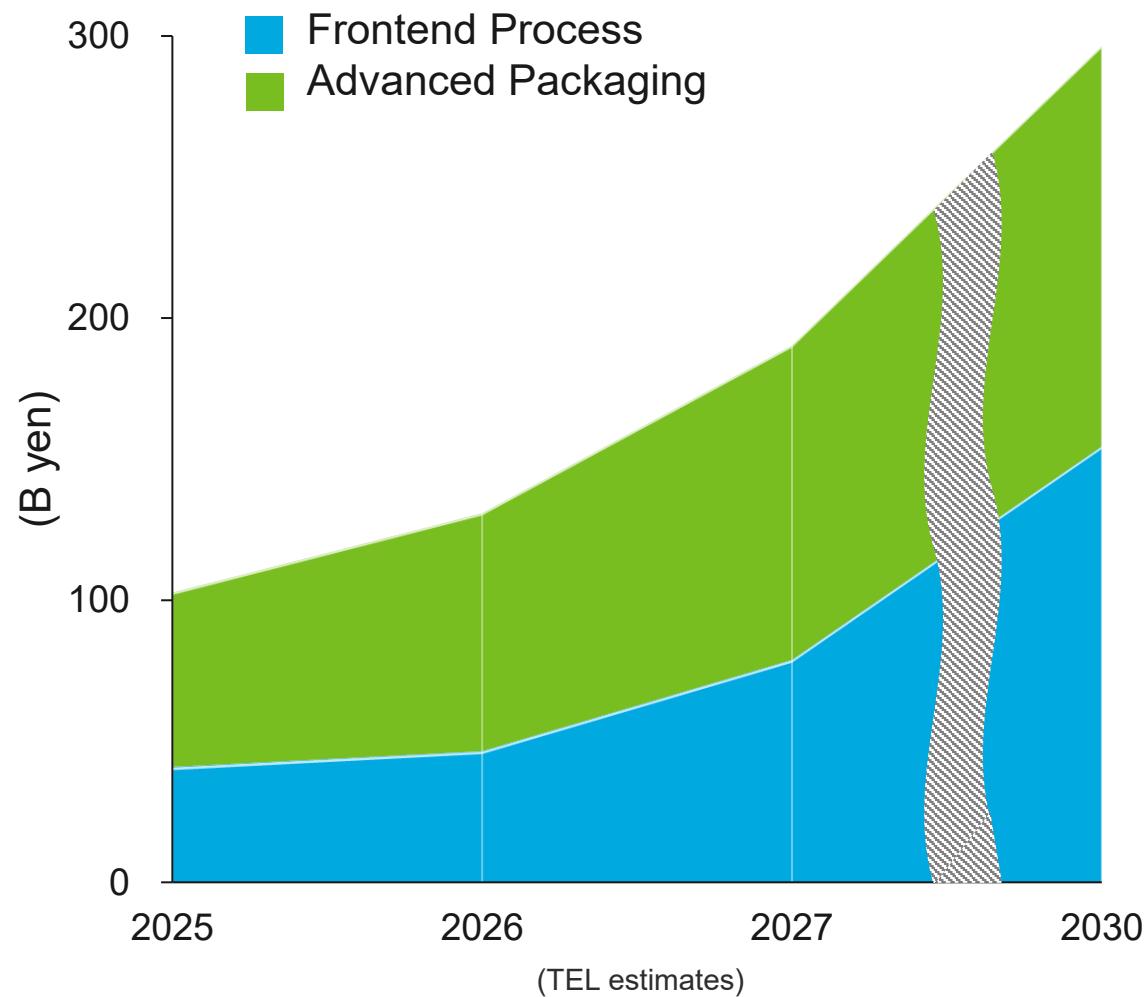

# ボンディング工程に関する製造装置市場規模 (当社見込み/TAM\*)

CY2025からCY2030でのCAGRは

24%と高成長を見込む

- CY2030には3,000億円規模に

- 前工程向けと先端パッケージング向けの両方セグメントで成長

- ボンダー（永久/仮貼合）、デボンダー（剥離）、切削、薄化と技術は各種技術が対象

\* TAM : Total Available Market

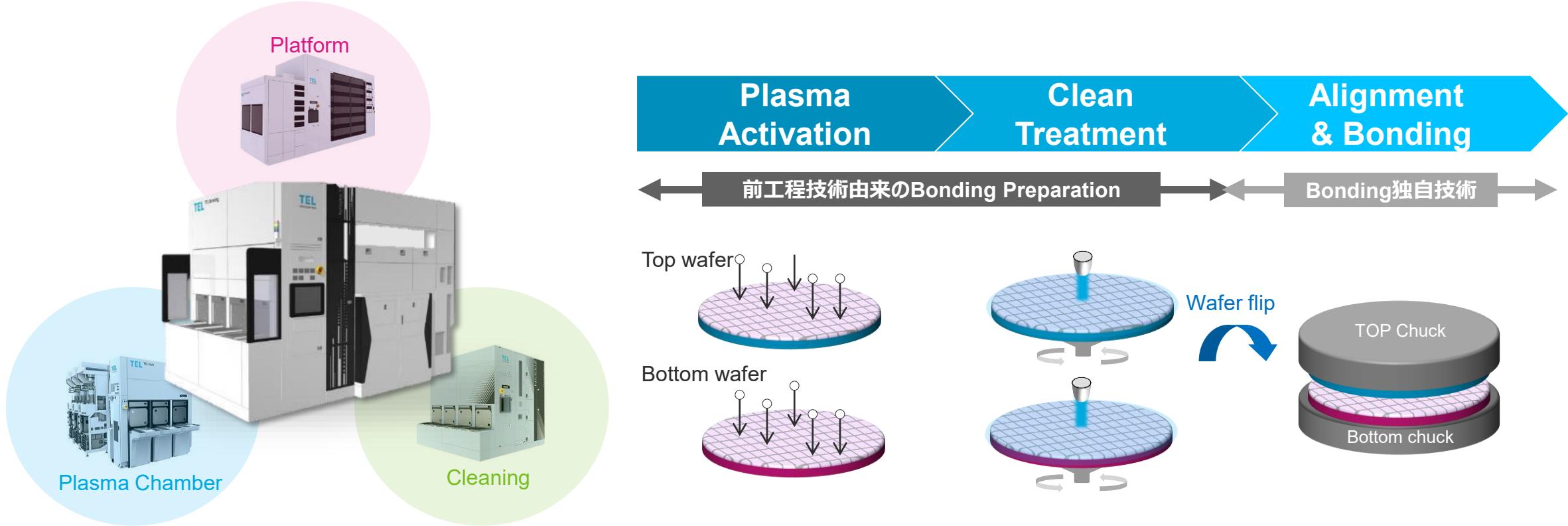

# ウェーハ永久接合ボンダー Synapse™ Si

- 当社の有する広範な技術と様々な事業が、効率的な製品開発と性能改善に大きく寄与

- ボンディングの量産導入へ向けて、主要なメモリ/ロジックのお客様との評価が順調に進展

- 次世代デバイス製造へ、ウェーハでのフュージョン/Cuハイブリッドボンディング技術をリード

# ボンディング技術が適用される様々なアプリケーション

| Application     | 前工程                                                     |                                                                          |                                                                                   |                                                                    |                                                                  |

|-----------------|---------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|

|                 | CIS <sup>*1</sup>                                       | NAND                                                                     | DRAM                                                                              | Logic                                                              |                                                                  |

| Stacking Device | BSI <sup>*2</sup><br><br>( Pixel + Peripheral ) + Logic | 3D NAND<br><br>Cell + Peripheral → Cell + Peripheral + Cell + Peripheral | VCT <sup>*5</sup> DRAM<br><br>( Si Substrate + Peripheral + Cell + Si Substrate ) | 3D DRAM<br><br>( Si Substrate + Peripheral + Cell + Si Substrate ) | BSPDN<br><br>Logic + Si Substrate → Logic + Logic + Si Substrate |

| Bonding         | Wafer to Wafer (CHB <sup>*3</sup> /Fusion)              | Wafer to Wafer (CHB)                                                     | Wafer to Wafer (CHB/Fusion)                                                       | Wafer to Wafer (CHB/Fusion)                                        | Wafer to Wafer (HB <sup>*6</sup> /Fusion)                        |

| Structure       |                                                         |                                                                          |                                                                                   |                                                                    |                                                                  |

| Status          | HVM <sup>*4</sup>                                       | R&D~HVM                                                                  | R&D                                                                               | R&D                                                                | R&D~HVM                                                          |

将来のデバイス構造は単層から複層ボンディングへ

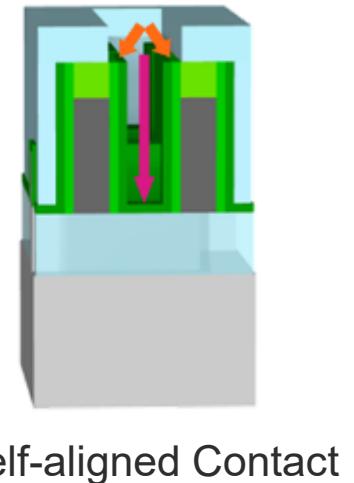

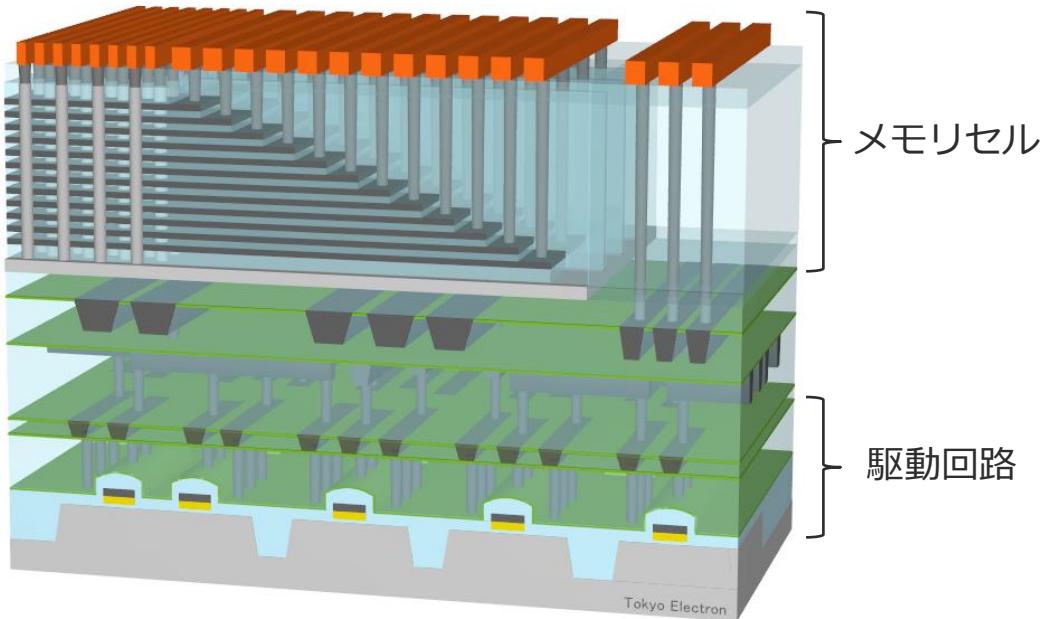

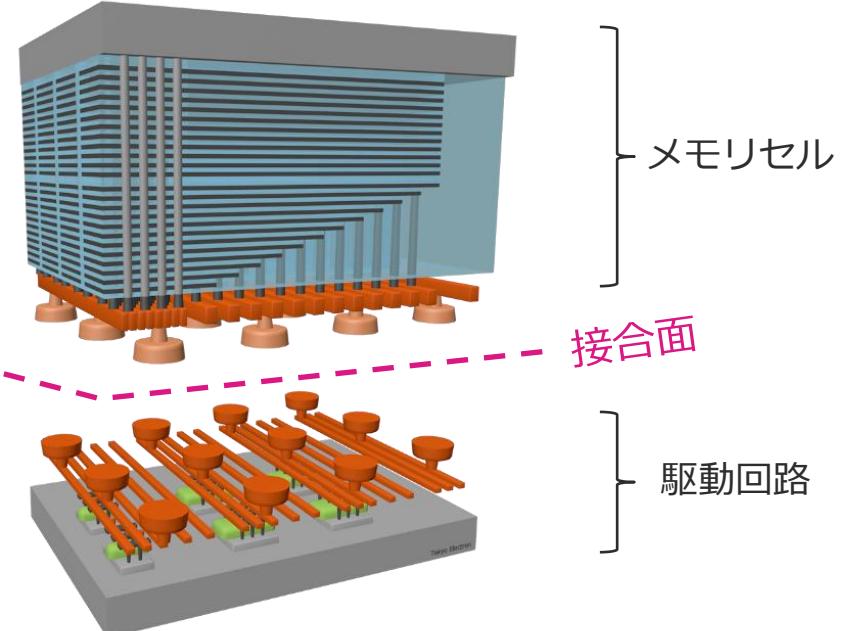

# 貼り合わせ接合導入例：3D NAND

従来構造

接合構造

- ✓ 駆動回路が高熱に晒され劣化

- ✓ 長い配線長

- ✓ 駆動回路を別ウェーハで製造、メモリセルと貼り合わせ

- 回路性能向上

- 短TAT\*プロセス

- ✓ 短い配線長

\* TAT: Turnaround time

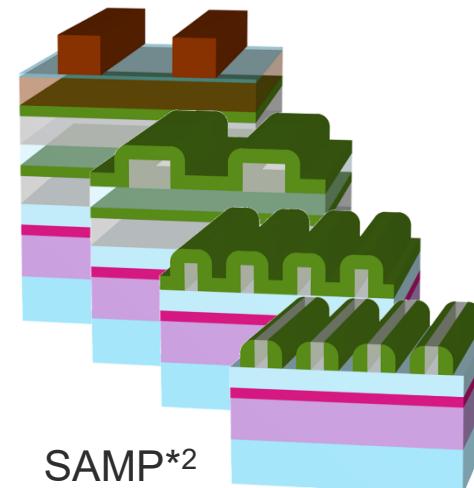

# 貼り合わせ接合導入例：Logic Backside PDN

# ボンディング技術が適用される様々なアプリケーション

| Application     | Advanced Packaging                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |                                                                              |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|                 | Stack Memory / HBM                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                   | 3DIC                                                                                                                              |                                                                              |

| Stacking Device | <p>Stacking Device</p> <p>OR</p> <p>DRAM Wafer<br/>+<br/>DRAM Wafer<br/>+<br/>Logic Wafer</p> <p>DRAM Die<br/>+<br/>DRAM Die<br/>+<br/>Logic Wafer</p>                                        |                                                                                                                                                                                                                                                                                                                                                                                                   | <p>SoC Disaggregation</p> <p>OR</p> <p>Device A Wafer<br/>+<br/>Device A or B Wafer</p> <p>A<br/>B<br/>C</p> <p>Die<br/>Wafer</p> | <p>Heat Spreader</p> <p>Heat Spreader + Device</p>                           |

| Bonding         | Wafer to Wafer / Die to Wafer (CHB/Fusion)                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                   | Wafer to Wafer / Die to Wafer (CHB)                                                                                               | Wafer to Wafer (Fusion)                                                      |

| Structure       | <p><b>Micro Bump</b></p> <p>Change</p> <p>• Thinner die / more stacks<br/>• High density connection<br/>• Better thermal conductance</p> <p><b>Cu hybrid</b></p> <p>More stacks</p> <p>Cu</p> | <p><b>Monolithic SoC</b></p> <p>Change</p> <ul style="list-style-type: none"> <li>Small formfactor (3D stack vs. 2D)</li> <li>Higher speed (shorter wiring, no bump)</li> <li>Lower power (shorter wiring, no bump)</li> <li>Lower cost (higher yields, easy to mix processes)</li> <li>Shorter time to market (matured IP block reuse)</li> </ul> <p><b>3D Stack IC</b></p> <p>Heat Spreader</p> |                                                                                                                                   | <ul style="list-style-type: none"> <li>Better thermal conductance</li> </ul> |

| Status          | R&D                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                   | R&D ~ HVM                                                                                                                         | HVM                                                                          |

フュージョン/Cuハイブリッドボンディング技術は先端パッケージング工程へ拡大

## 前工程ボンディングプロセスと当社の製品群

当社製品群により、高効率で高品質なボンディングプロセスを実現

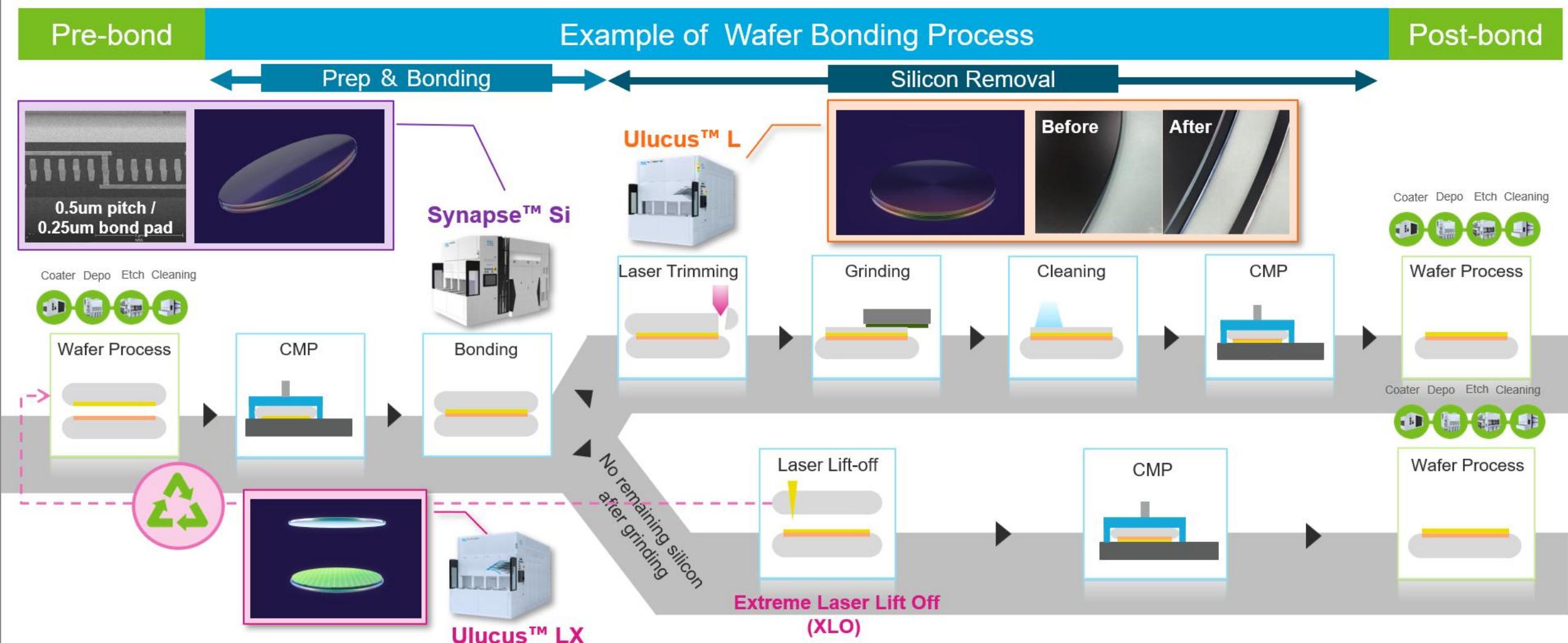

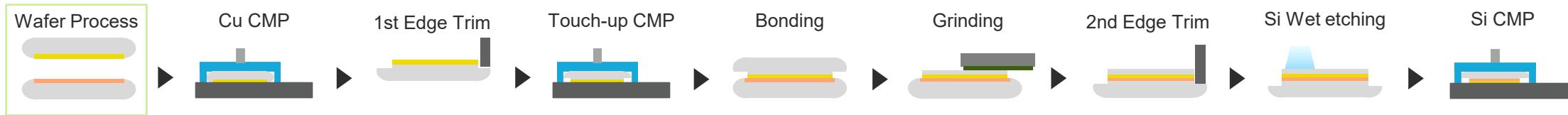

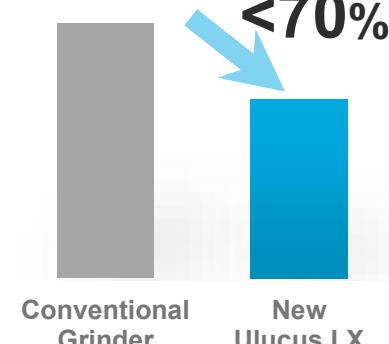

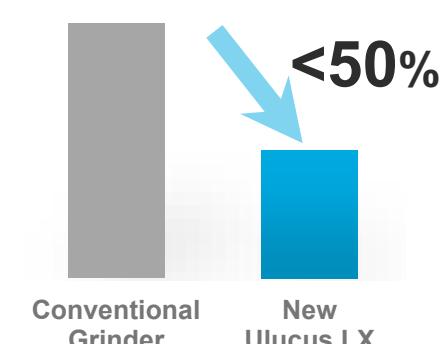

# レーザトリミング装置: Ulucus™ L

## ■ 概要

- ウェーハ接合でのエッジトリミング装置

- 前工程レベルのスーパークリーン技術を適用した最新プラットフォームとレーザ制御技術を融合

レーザ技術による、高精度・高品質なトリミングと純水使用削減によるエコフレンドリーの両立を実現する

# レーザトリミング装置

ウェーハ製造でのウェーハ貼り合わせ工程をレーザ技術により革新

エッジトリミング工程での歩留まり改善と純水使用量の大幅な削減を実現

## Higher Accuracy

Enabling narrower trimming width

## Smooth Sidewall

Less damage, Better yield

## Higher Throughput

High productivity, Reliability

## Save Water

Reducing DIW to 70% or more

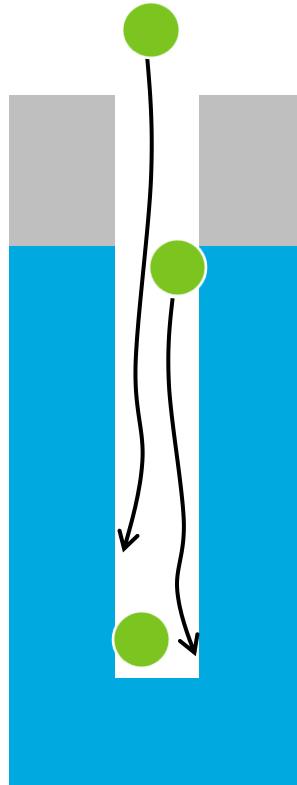

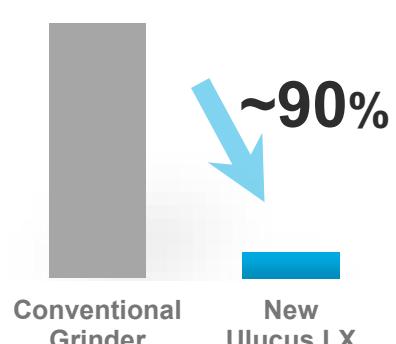

# ポストボンディング工程向け Ulucus™ LX

## ■ エクストリームレーザー リフトオフ(XLO) 技術の搭載

- ポストボンディング工程

(ウェーハ接合後に続く重要工程)

への次世代薄化技術

- シリコン基板とデバイス薄膜層を

レーザにて分離

## ■ プロセス性能と環境性能における価値

- シリコン有効面積の拡大

- 製造工程数の削減

- 純水使用量/CO<sub>2</sub>排出量の削減

- ウェーハ再利用の可能性

## ■ 製品リリース：2024年12月

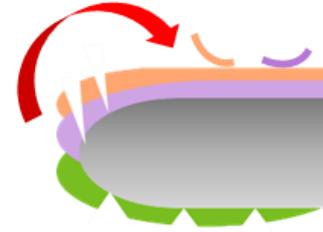

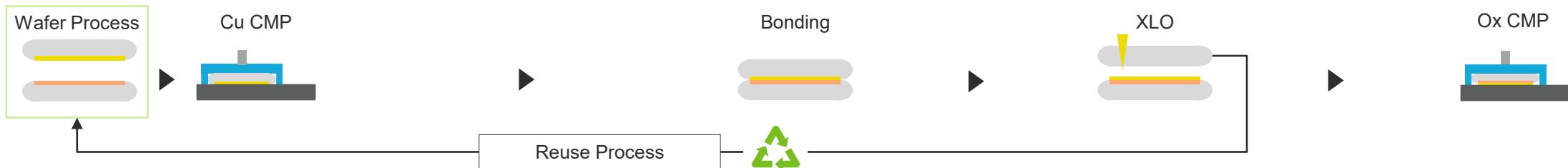

# Ulucus™ LX を採用する価値

## Permanent Bonding Process with Grinding & Blade Edge Trimming (Conventional)

## Permanent Bonding Process with XLO (Extreme Laser Lift Off)

シリコン有効面積

製造工程数

純水使用量

二酸化炭素排出量

(ウェーハ再利用前提)

シリコン汚泥レス

→ グラインダーに対する利点

## 8. MAGIC市場とフィールドソリューションの取り組み

# MAGIC 市場

- 2倍の市場成長を期待

(2023年約\$25B、2030年\$50B想定)

- MAGIC向け装置群を開発、供給

- MAGIC向け200mmのデモラインも用意

- 山梨・熊本・宮城

- マサチューセッツ・ミネソタ・フロリダ

# 成熟世代向け装置

- 200mm ウエーハ対応 リニューアル装置

- 熱処理成膜装置、コーダ/デベロッパ、エッチング等

- 既存顧客の置き換え需要のみならず、新興顧客、新規アプリケーション向けにも販売拡大

- パワー半導体向け装置

- SiCウェーハ対応装置、300mm 対応エッチング装置

- 車載向けから更に用途が広がるパワー半導体需要に対応

SiCエピタキシャル成膜装置

保有する技術資産と最新の技術を融合し、生産性の向上や環境負荷低減を実現

多様なニーズに多様な装置とソリューションを提供

## 先端デバイスの進化

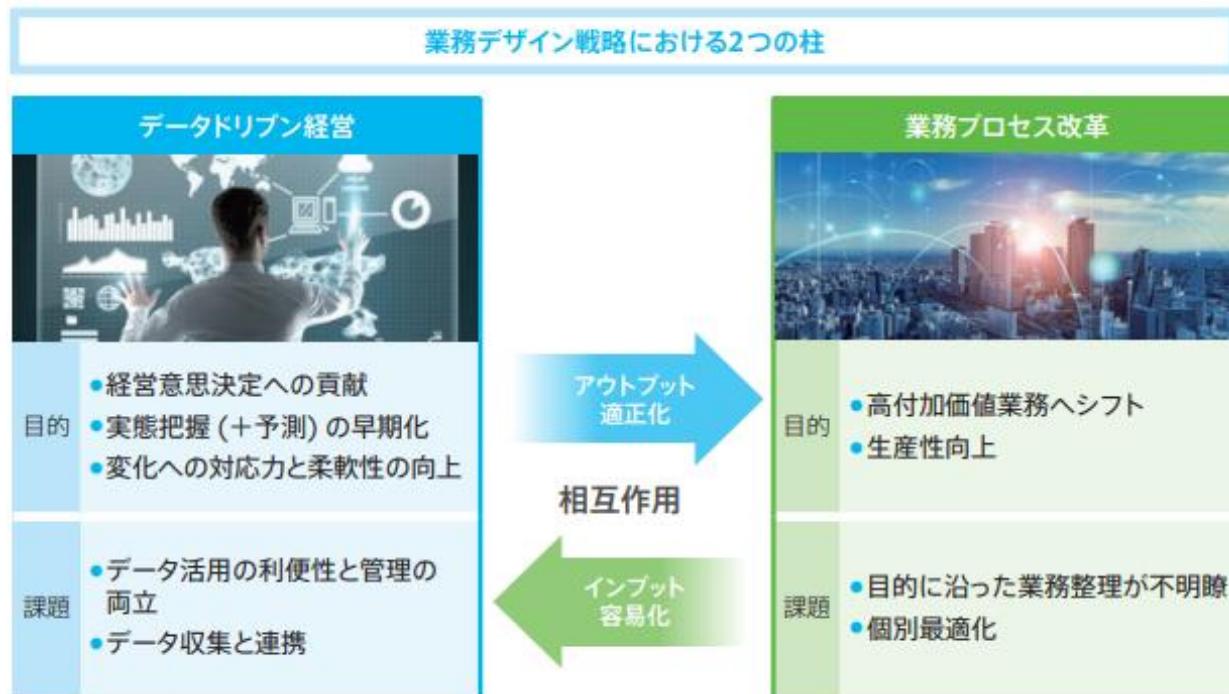

# フィールドソリューション (FS) の基本戦略

- 納入済み装置をベースとしたソリューション・ビジネスの展開

- アドバンスド・フィールドソリューションの開発と推進

- DXなど最新技術を用いた、最先端かつサステナブルなサポート

- 遠隔保守サポートや教育ツールの開発

- フロントライン強化

- フィールドエンジニアの継続的なスキルアップ

付加価値の高いサービスで、お客様のビジネスオペレーションの最大化に貢献

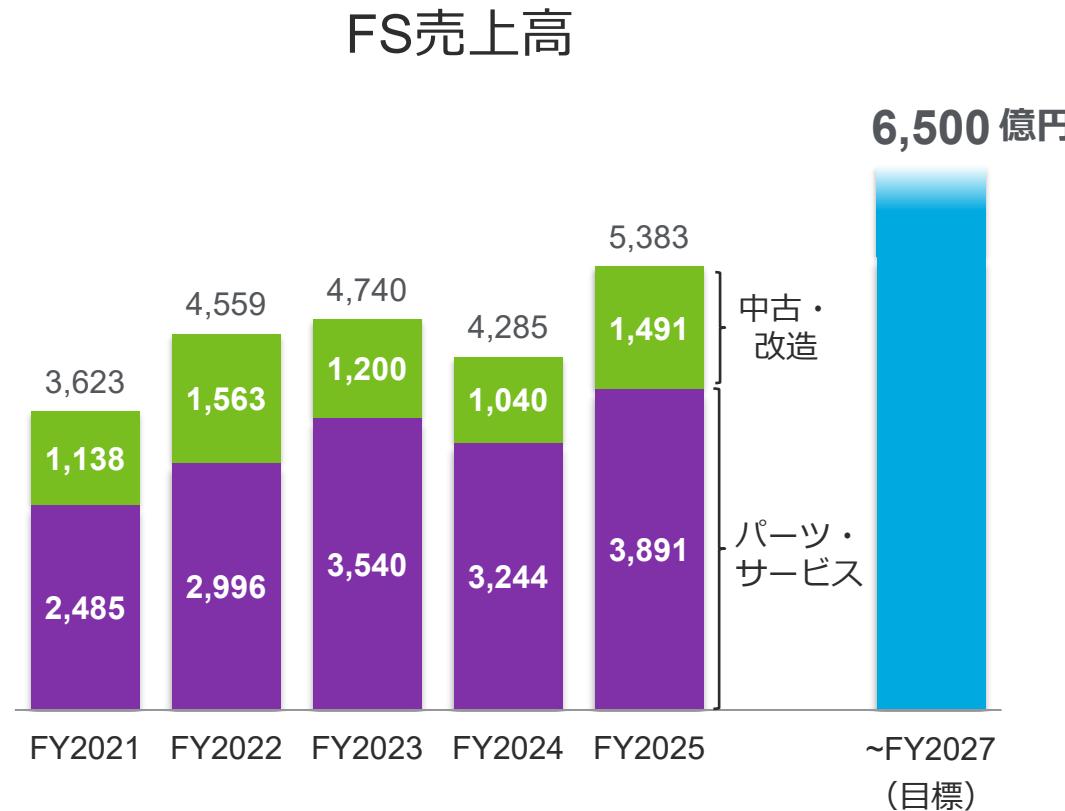

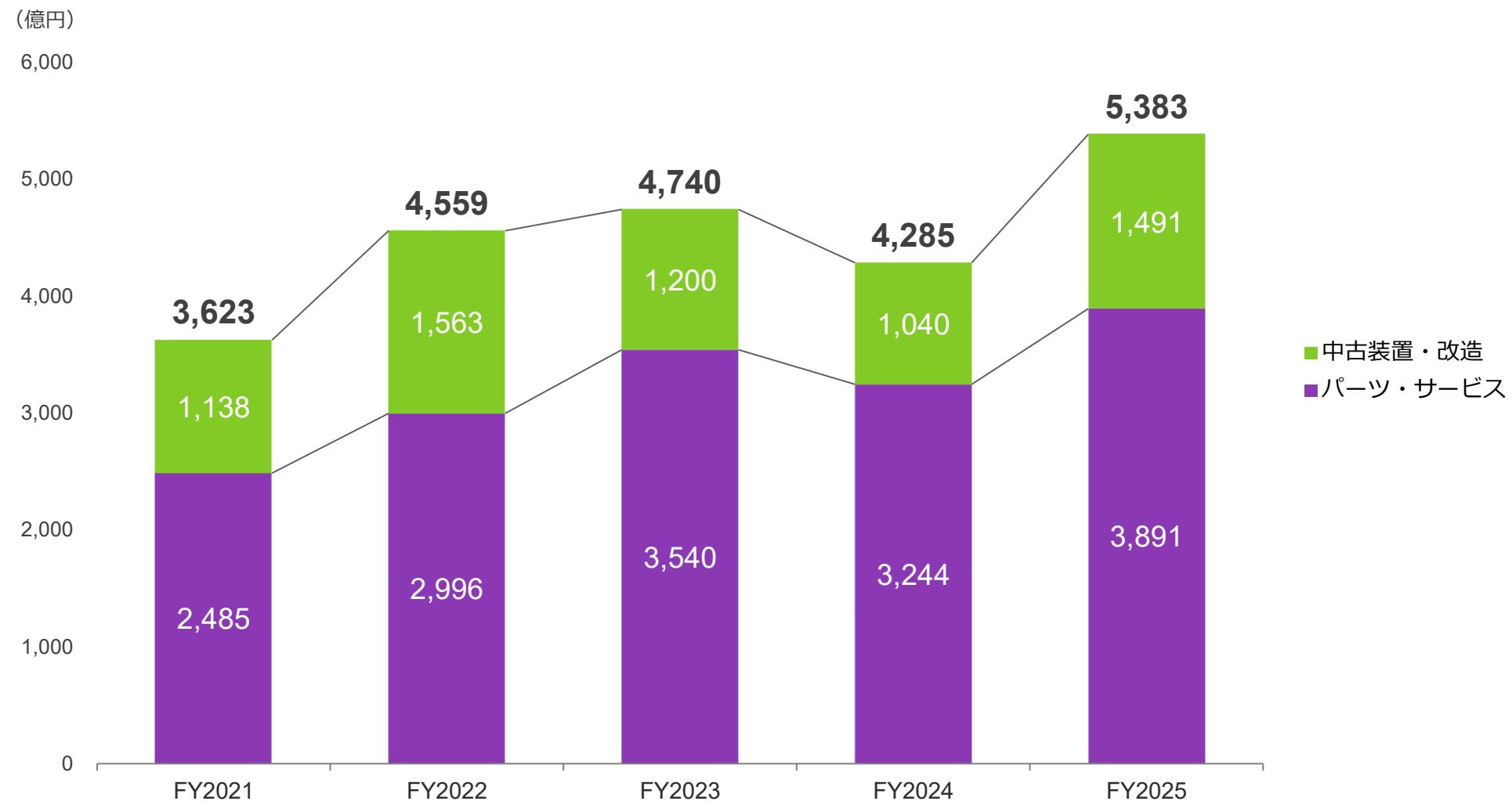

# フィールドソリューション (FS) の売上実績と事業内容

- パーツ・リペア

- パーツ劣化の予知保全

- 適切なパーツ在庫管理と迅速な配送

- サービス

- 装置納入からアフターメンテナンスまで一貫した「包括契約型」サービスの提供

- お客様ごとのご要望に応えながら、装置稼動率を最大限に高めるためのソリューション提案

- 改造

- 生産性向上

- 歩留まり改善

出荷済み装置 99,000台<sup>\*1</sup>。年間約4,000～6,000台の納入台数増加によるSAM<sup>\*2</sup>拡大

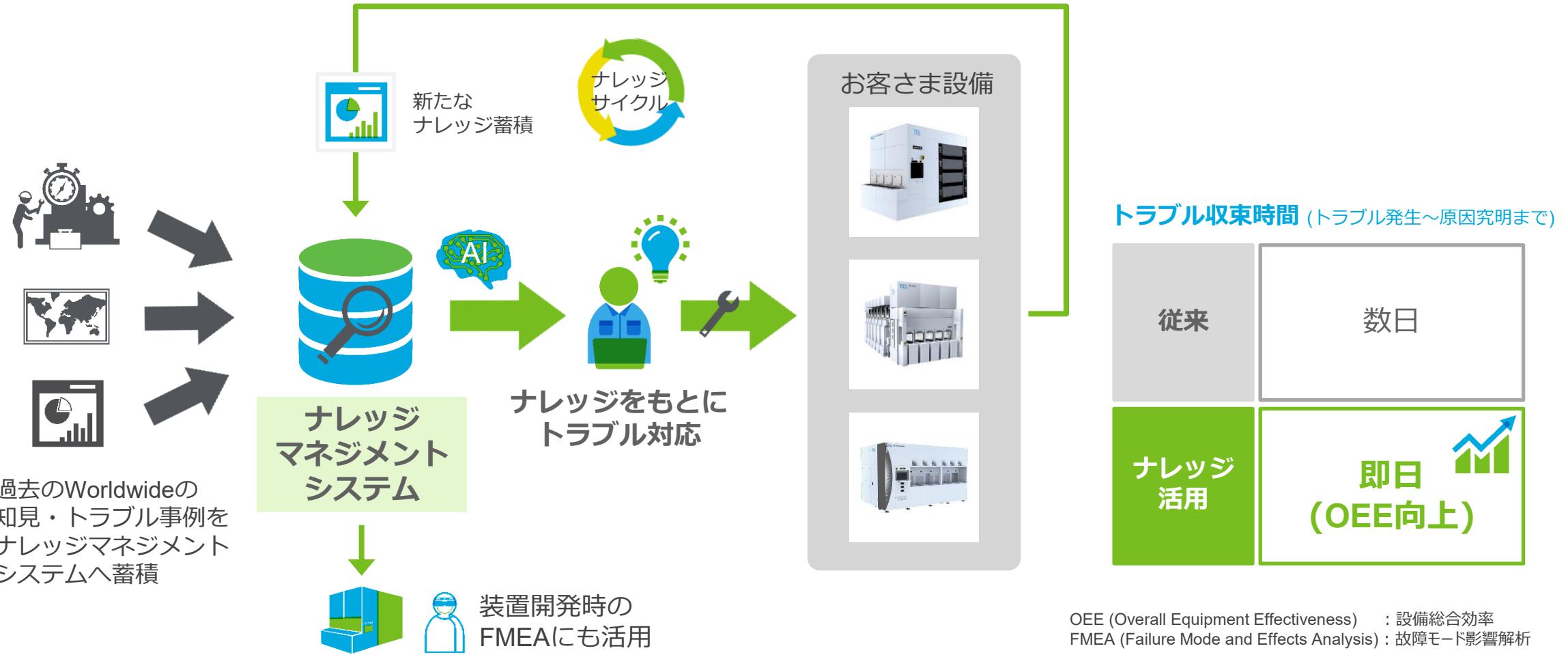

# アドバンスド・フィールドソリューション

## TELeMetrics™

- 個別装置情報の把握

- ナレッジマネジメント、トラブル事例の蓄積

## リモートサポート

- 装置の予知保全によるダウンタイムの最小化

- 渡航制限下でも迅速な対応を可能とする遠隔サポート

DXを推進する「TELeMetrics™」を中心とした付加価値の高いソリューション提案

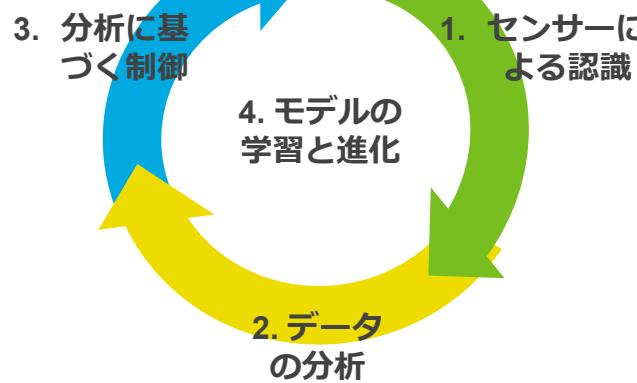

## 9. デジタルトランスフォーメーション (DX) の取り組み

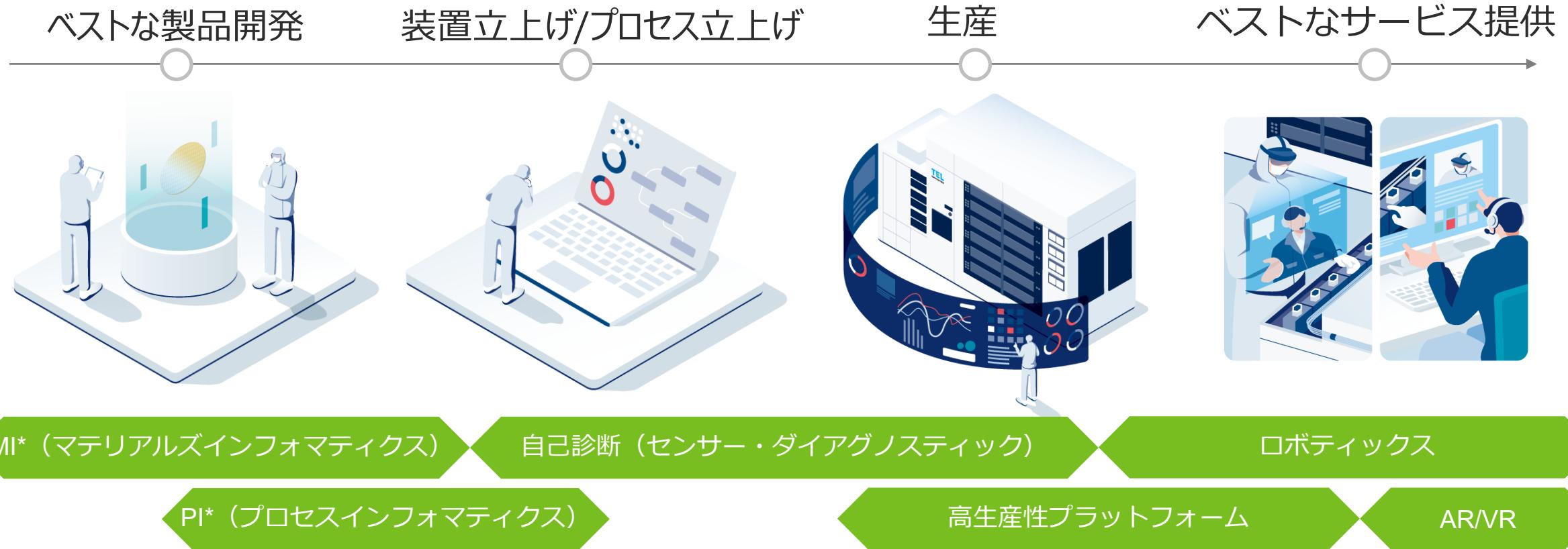

# 製品ライフサイクルにおけるDX

生産性・収益性を高めるべく、製品ライフサイクル (PLC)全体でデジタルライネーブラーを開発

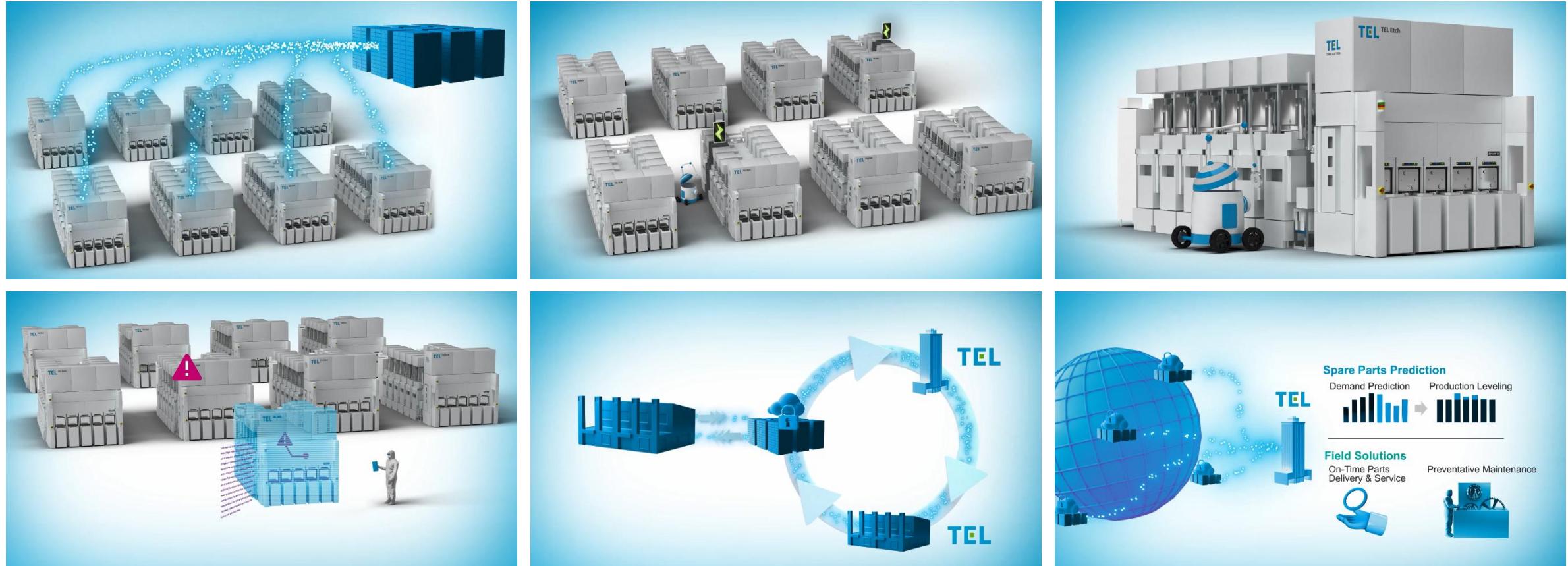

# 業務におけるDX

## ■ 業務デザイン戦略本部

- データドリブン経営 × 業務プロセス改革の相互作用でDXを推進

- 生成AIなどのデジタル技術を活用するための環境整備

- チェンジマネジメントでDX文化を醸成し、継続的な成長を促進

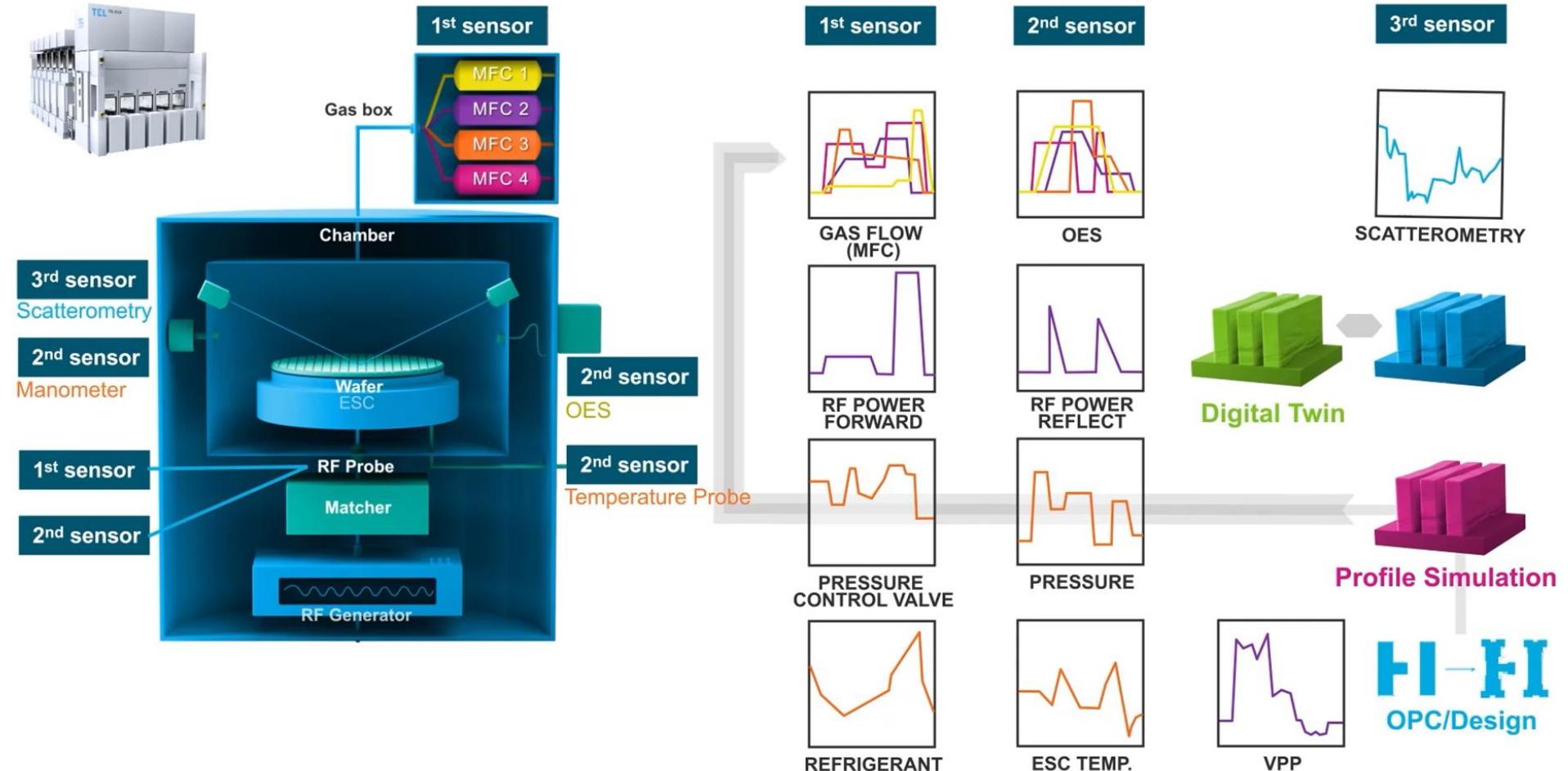

# 事例① エッチング装置におけるデジタル技術活用

あらゆるデジタル技術を用いて、顧客価値の最大化を目指す

## 事例② エッチング装置におけるデジタル技術活用

あらゆるデジタル技術を用いて、顧客価値の最大化を目指す

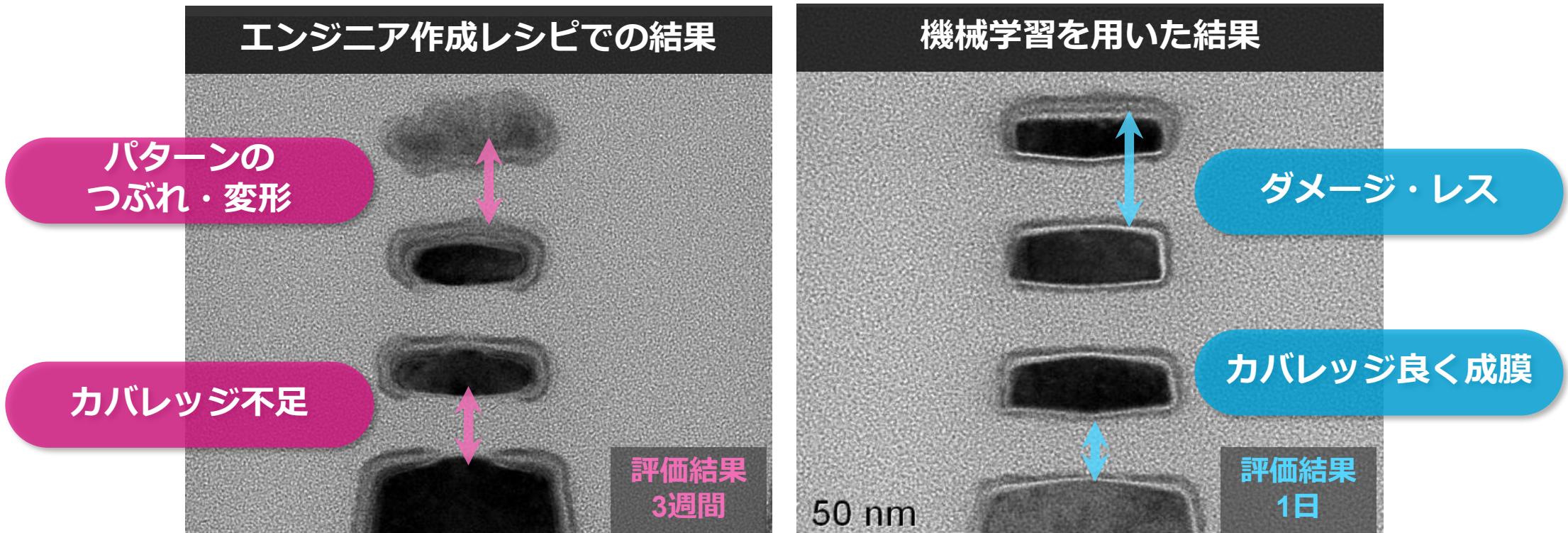

## 事例③ 研究開発の生産性向上：プロセスインフォマティクス

Source: Tokyo Electron Technology Solutions Limited / Tokyo Electron Limited

機械学習により、ALDプロセスにおいて、パターンの変形がない

良好なステップカバレッジを実現

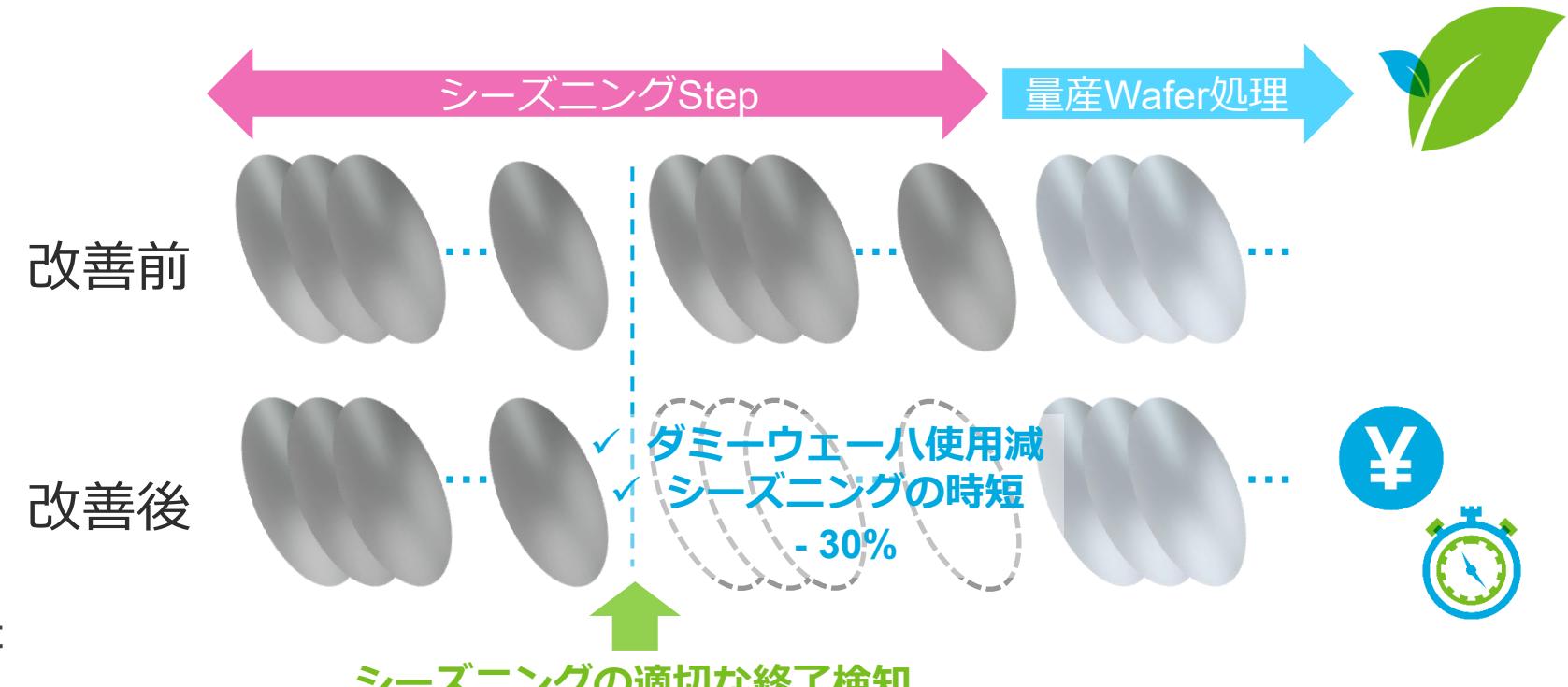

## 事例④ 装置の生産性向上：エッチング装置の稼動率改善

※ISSM 2020 当社発表 "Seasoning Optimization by using Optical Emission Spectroscopy" より

センサーによるチャンバーコンディションの適切な把握と

フィードバックにより、装置稼動率を改善

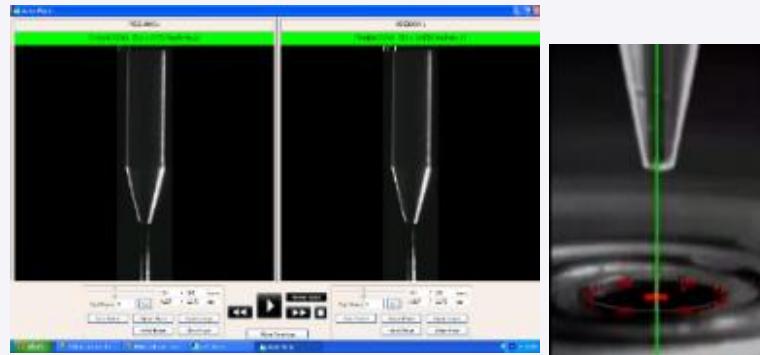

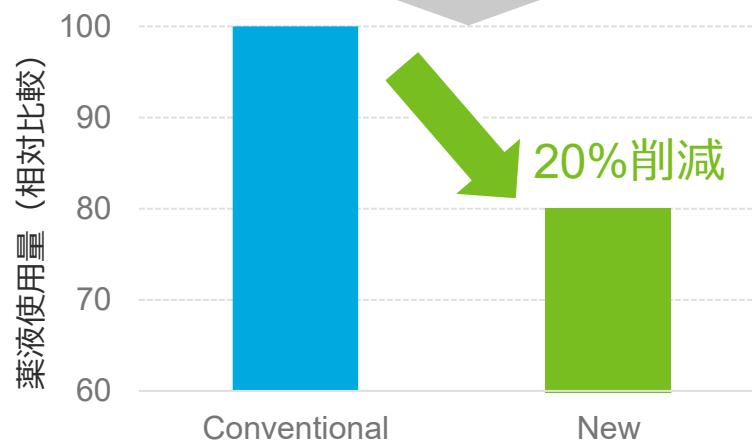

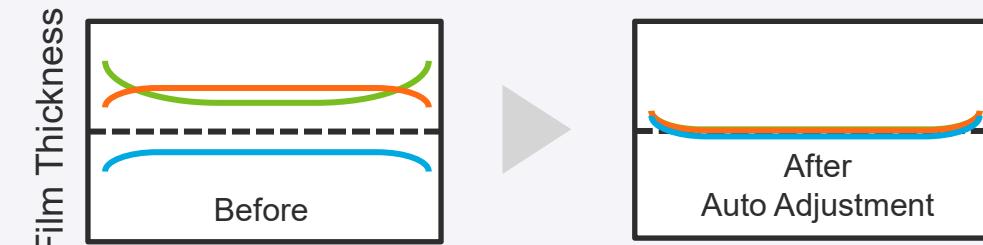

# 事例⑤ 装置のオペレーションコスト効率の向上：コータ/デベロッパの省薬液

画像処理技術を使った薬液吐出状態のモニタリング

画像処理技術を使った薬液面内カバレッジのモニタリング

| Dispense Volume | X ml                                                                                | Y ml                                                                                | Z ml                                                                                | A ml                                                                                 |

|-----------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Judgement       | Passed                                                                              | Passed                                                                              | Failed                                                                              | Failed                                                                               |

| Wafer image     |  |  |  |  |

自動膜厚調整機能

機械学習を使って、顧客オペレーションコストと環境に貢献

## 事例⑥ 装置OEEの向上：

ナレッジマネジメントシステムによりトラブル収束時間を短縮し設備稼動率を向上

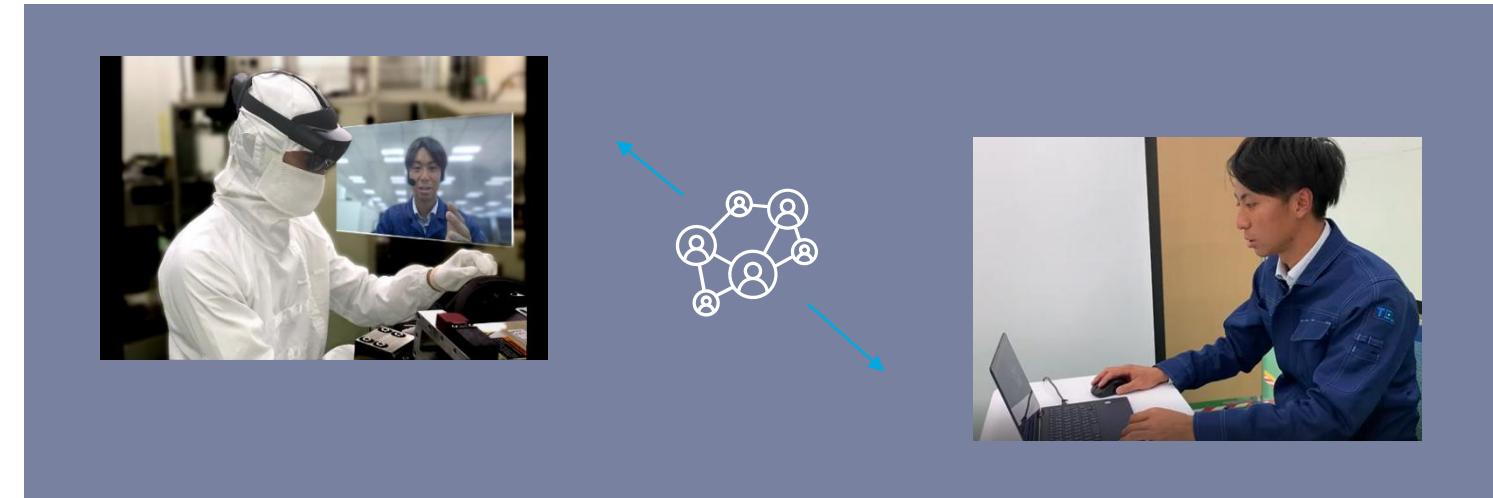

## 事例⑦ フィールドソリューションにおけるDX

スマートグラスや遠隔地からの専門家からのサポートをもとに、クリーンルーム内の立上げとメンテナンスにおける作業効率を最大化。

AR/VRおよびデジタルツイン技術を含むDXを推進する

人を介さないパート交換の実現により、

ダウンタイムの最小化とエンジニアリング作業の品質向上を図る

## 10. 調達・生産戦略

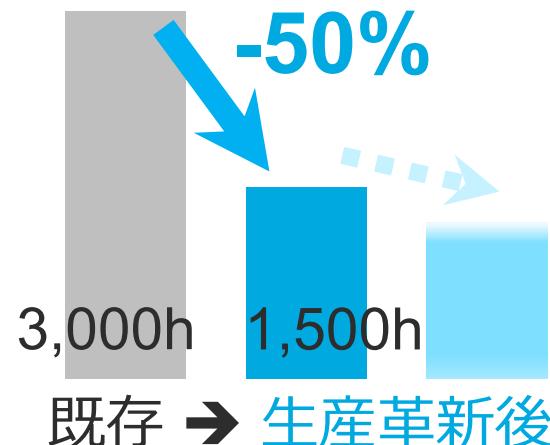

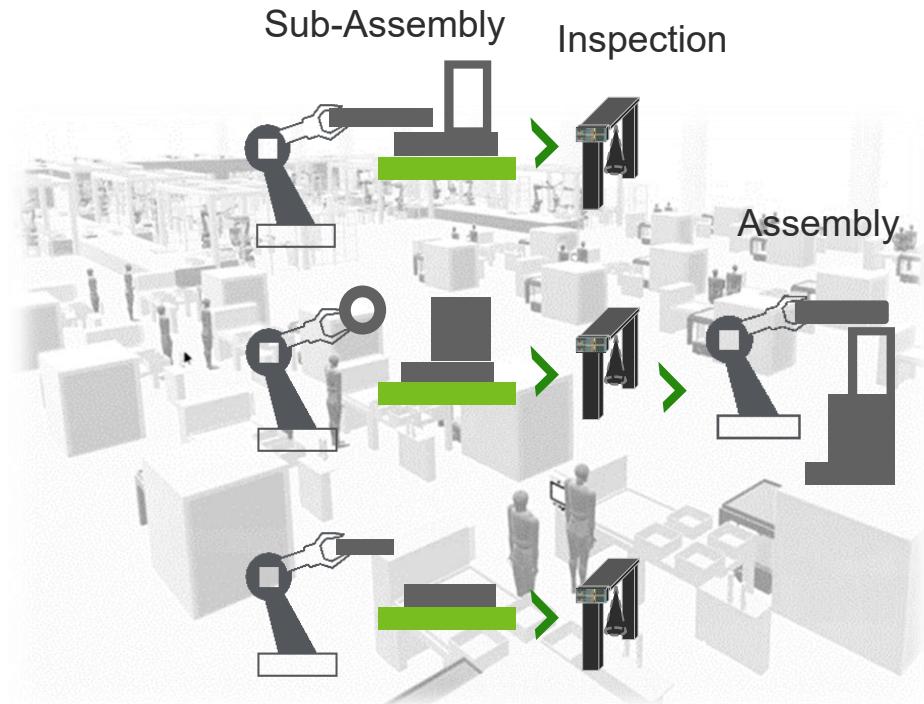

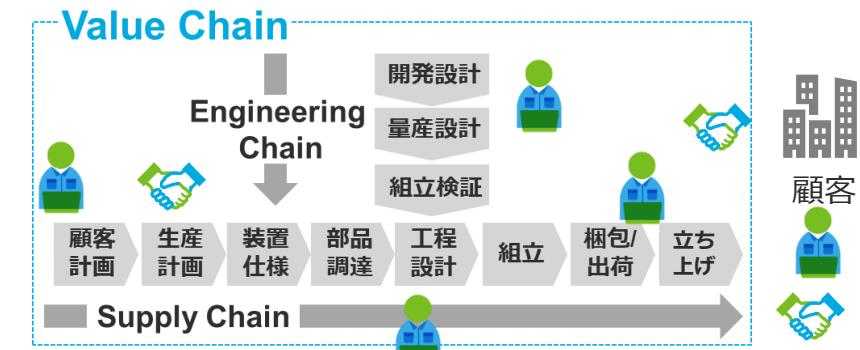

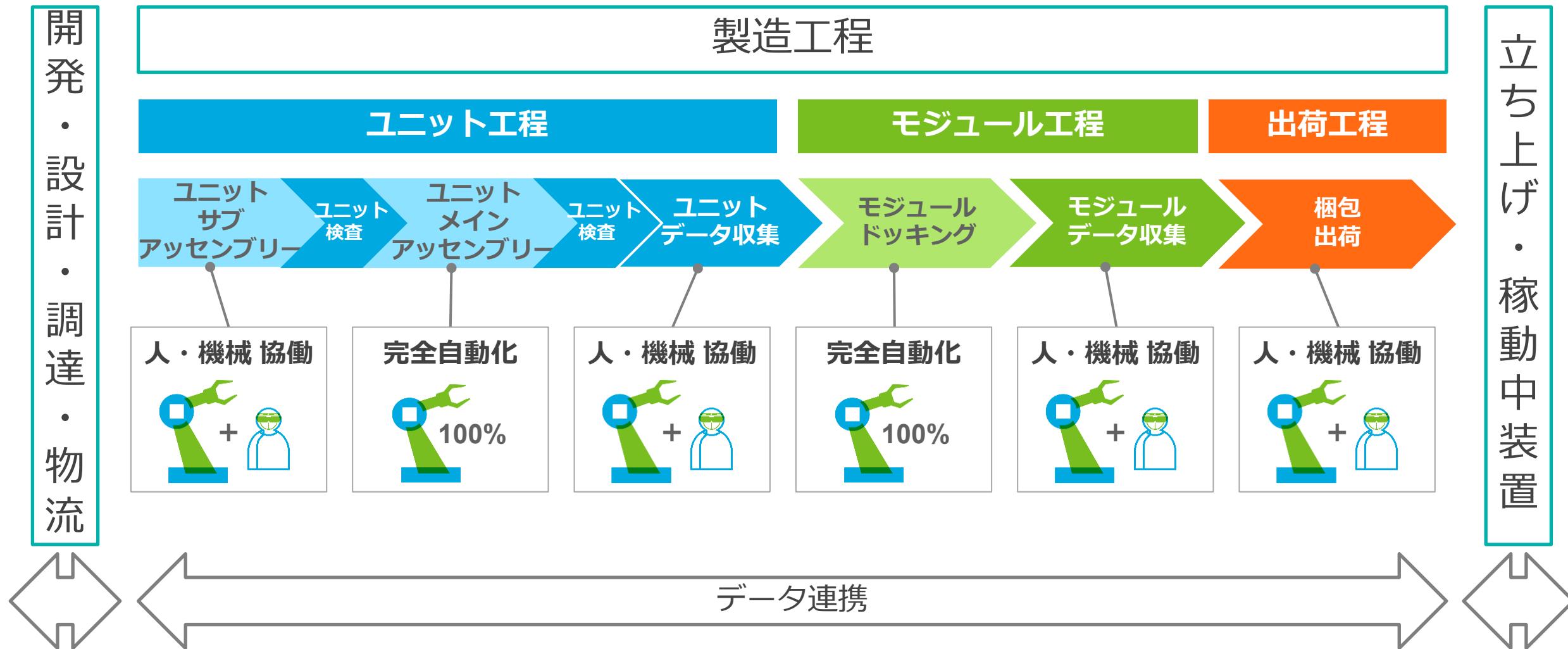

# 安全性・高品質・高信頼性を追求する継続的な生産革新

- 市場変動に迅速に対応できる生産システムの構築

- 新製品の開発から量産化までの移行時間の短縮

- 生産リードタイムの短縮：モジュール出荷100%実施

- 製造ライン DX・自動化、自動倉庫拡張/進化

- **立ち上げ工期の大幅削減（One-Touch立ち上げ）**

- 工期削減▲～75%（1次目標），ワンタッチ（Goal）

## 立ち上げ期間の短縮（例）

## 立ち上げ期間短縮による期待効果

- 生産性・スタートアップ品質向上

- 事故リスク低減

- リソースとワークライフバランスの適正化

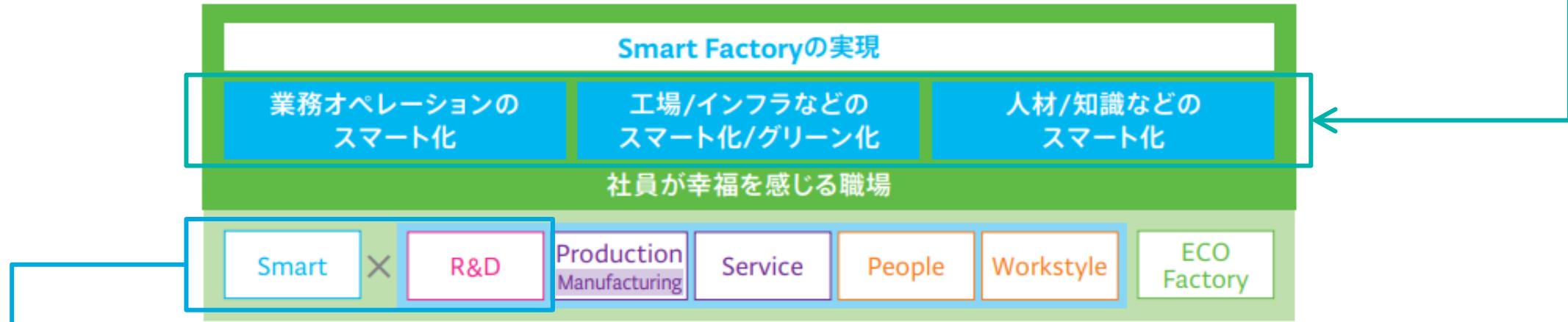

# Shift Left推進の取り組み事例：Smart Factory構想

付加価値の高い技術と製品をお客さまへ提供するために重要度が増している3要素

Smart R&Dの実現に向けてさまざまな施策を展開

## 事例①

DXにより蓄積された社内データを分析・活用することで、経験値の浅いエンジニアでも、熟練エンジニアの知見や経験則をいつでも学べる環境を整備

→新製品の開発へタイムリーにフィードバックする事で、開発期間短縮を実現する

## 事例②

デジタル技術を活用し、これまでエンジニアが繰り返しあこなっていた作業の自動化に取り組む

→社員が付加価値の高い業務に専念できる

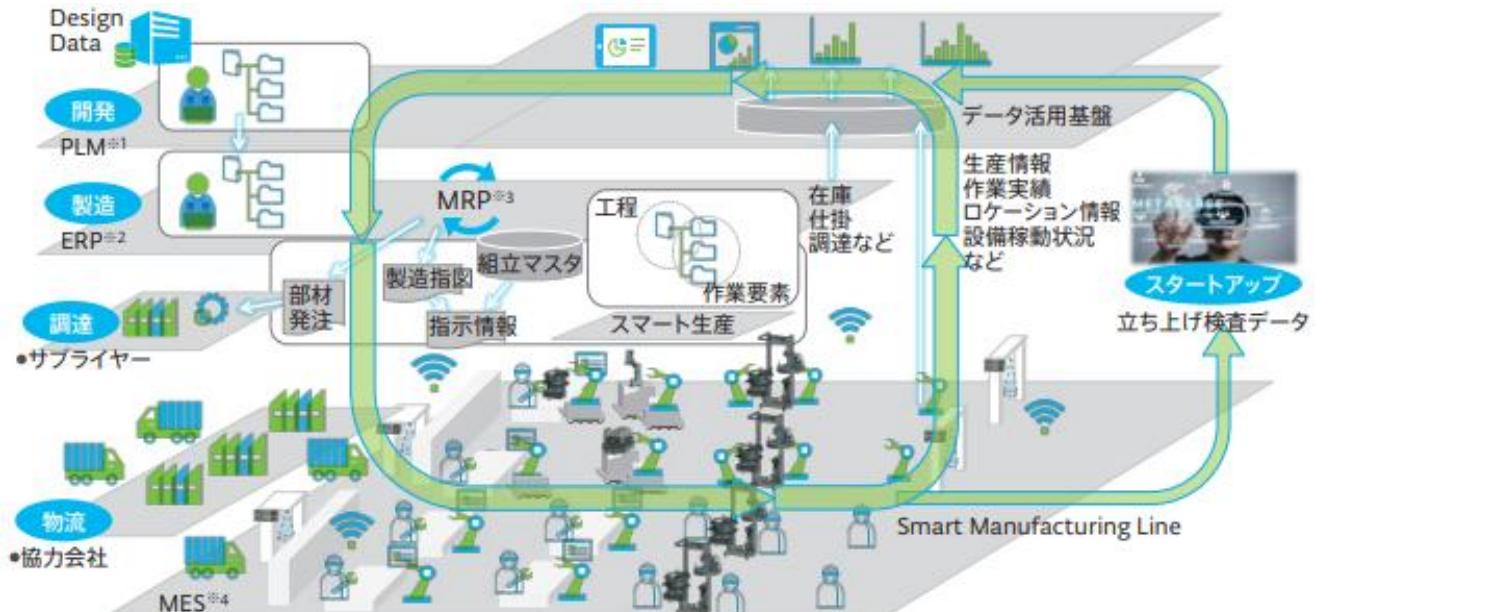

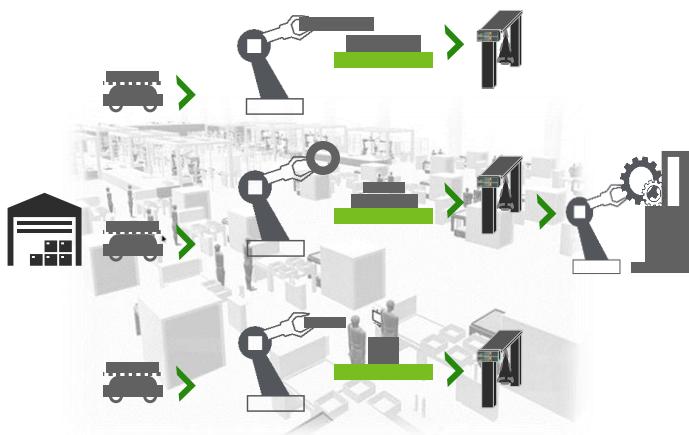

# DXによる革新的な生産体制の構築 : Smart Manufacturing

生産に関するあらゆるデータをリアルタイムで連携・情報化し、最適な意思決定と即時アクションが可能となる生産体制の構築を推進。

- 基幹システムの性能向上

- 生産の平準化

- 調達のMRP処理能力向上

- PLM-DX・BOM<sup>※5</sup>概念導入

- 生産能力強化

- 製造リードタイム最短化

- 設計高効率化

- 新製品開発期間の短縮

※1 PLM: Product Lifecycle Management

※2 ERP: Enterprise Resource Planning

※3 MRP: Material Resource Planning

製品ライフサイクル管理

経営資源計画

資材所要量計画

※4 MES: Manufacturing Execution System

製造実行システム

※5 BOM: Bill of Material 部品表

Smart R&D構想

Smart Manufacturing構想により、

高品質な製品を効率的かつ安定的に生産する最先端の製造ラインを実現

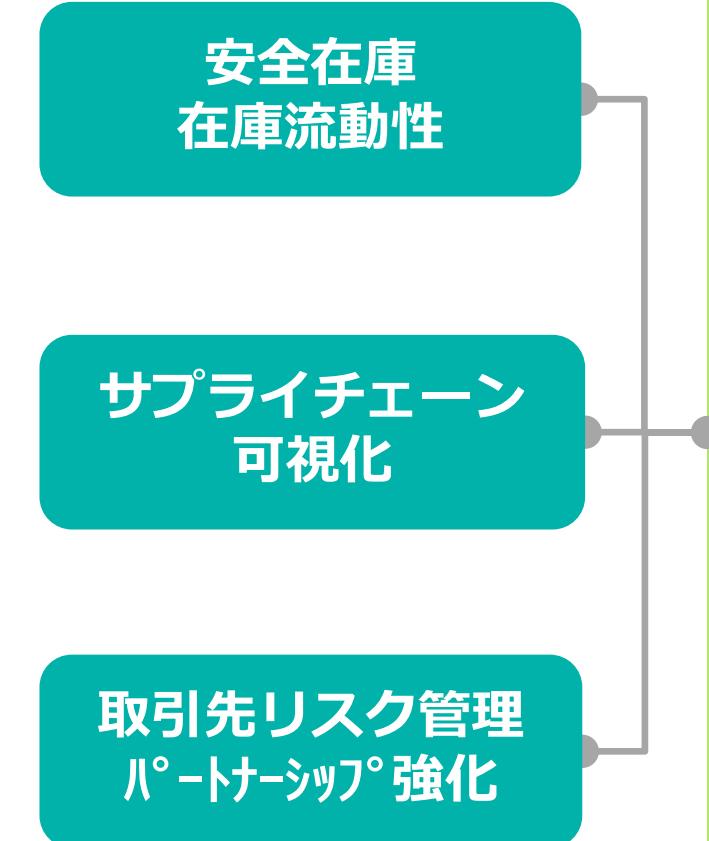

# 持続可能なサプライチェーンの構築

- お取引先さまとの公正かつ透明なお付き合い、確かな信頼関係

- 業界行動規範に基づいたCSR／BCPアセスメントの実施

- 安全や品質、環境やコンプライアンスなどのナレッジ共有

E-COMPASS

アセスメントの調査項目に

環境関連を追加し

環境負荷低減活動を称賛

- ✓ CO<sub>2</sub>排出量・エネルギー使用量削減

- ✓ 再生可能エネルギー導入

- ✓ 省資源の推進

- ✓ 廃棄物削減・リサイクルの推進

- ✓ 物流の環境負荷低減活動の推進

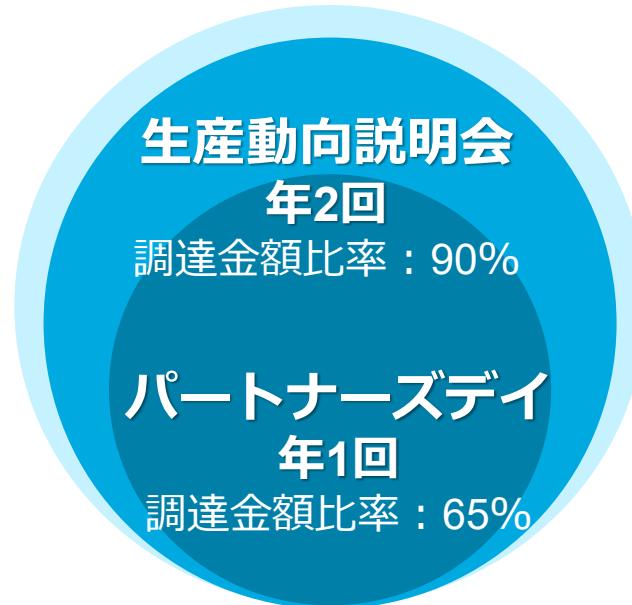

# 調達BCP・プロアクティブな調達活動

## 調達BCP施策

中長期フォーキャスト

Shift Leftの調達戦略展開

**調達難に強いBCP体制構築**

サプライチェーンを上流から

下流まで一気通貫で把握

**リスクの見える化**

あらゆるリスクを想定した

サプライチェーン体制

(原材料・部品・加工・組立)

**強靭で信頼ができる

サプライチェーン**

### 部品の早期確保

- 長期先行手配

- 工場間の在庫融通性の確保

- トータル在庫削減

### 半導体の確保

- 装置用半導体供給の確約

- 商流の可視化・スリム化

- 半導体メーカーと密接な連携

=“TELの顧客はTELも顧客”

### 部品とサプライヤー

- リスク部品の特定と分析

- 生産国のマルチソース化

- 部品標準化・集約化・分散化

- アロケーション対策

# 東京エレクトロン宮城 生産新棟計画

- 延床面積：約88,600m<sup>2</sup>（予定）

\*付帯設備エリア除く

- 構造：鉄骨造/全免震構造

地上5階建て

- 建設費用：約1,040億円

- 用途：エッティング装置の生産

宮城生産革新センター（2027年夏 竣工予定）

物流の自動化や製造工程の機械化を取り入れ、高い生産能力と高品質で

高効率な製造ラインを構築し、次世代生産（Smart-Production）を実現

# 高度な製品品質と高い生産性を両立するSmart Manufacturing

## 開発&設計

## Smart Manufacturing

開発と生産の拠点であるTEL宮城を中心に

絶え間ないコンカレントエンジニアリング、高度な生産技術を実現する。

# Smart Productionで目指す姿

- 将来にわたり持続可能なもののづくりを実現

自動化・標準化による

**圧倒的な効率化**

社内外環境変化にむけた

**対応力の強化**

Value Chain強化による

**製品品質・業務品質向上**

# Smart Productionのイメージ図

# Appendix : データセクション

# 損益状況

(億円)

|                 | FY2024 | FY2025   | 対前期<br>増減 | (ご参考)<br>2025年2月6日発表の<br>FY2025予想 |

|-----------------|--------|----------|-----------|-----------------------------------|

| 売上高             | 18,305 | 24,315   | +32.8%    | 24,000                            |

| 売上総利益           | 8,302  | 11,462   | +38.1%    | 11,290                            |

| 売上総利益率          | 45.4%  | 47.1%    | +1.7pts   | 47.0%                             |

| 販管費             | 3,740  | 4,489    | +20.0%    | 4,490                             |

| 営業利益            | 4,562  | 6,973    | +52.8%    | 6,800                             |

| 営業利益率           | 24.9%  | 28.7%    | +3.8pts   | 28.3%                             |

| 税金等調整前当期純利益     | 4,734  | 7,061    | +49.1%    | 6,910                             |

| 親会社株主に帰属する当期純利益 | 3,639  | 5,441    | +49.5%    | 5,260                             |

| 1株当たり当期純利益 (円)  | 783.75 | 1,182.40 | +50.9%    | 1,142.47                          |

| 研究開発費           | 2,028  | 2,500    | +23.2%    | 2,540                             |

| 設備投資額           | 1,218  | 1,621    | +33.1%    | 1,700                             |

| 減価償却費           | 523    | 621      | +18.7%    | 630                               |

1. 当社製品の輸出売上は、原則円建てでおこなわれます。一部に外貨建売上および費用計上もありますが、極端な為替レートの変動がない限りにおいては、利益への影響は軽微です。

2. 利益率および増減率は、1円単位の金額をもとに計算しています。

# 損益状況の推移 (FY2021～FY2025)

売上高・売上総利益・営業利益・当期純利益すべてにおいて、

過去最高の業績を達成

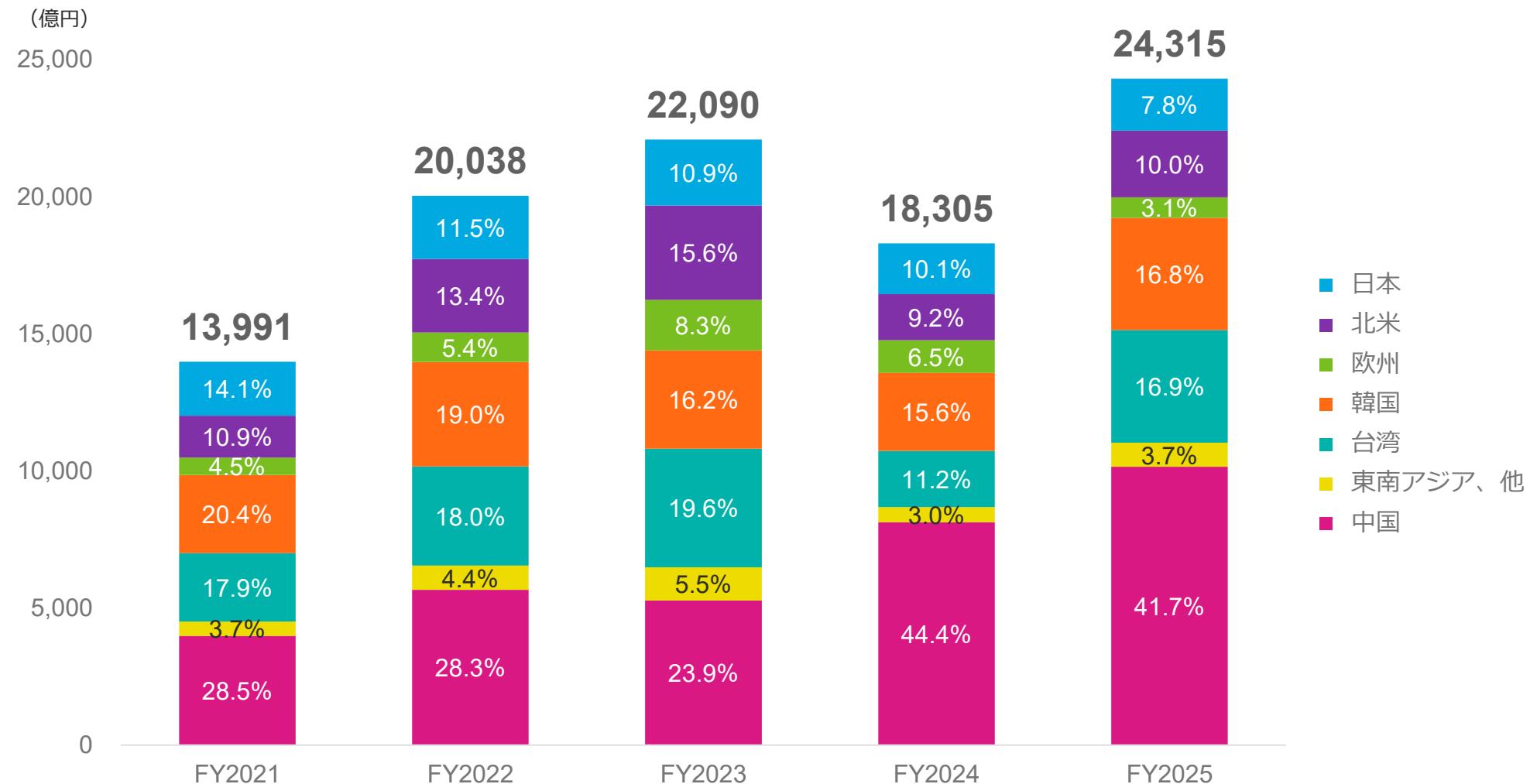

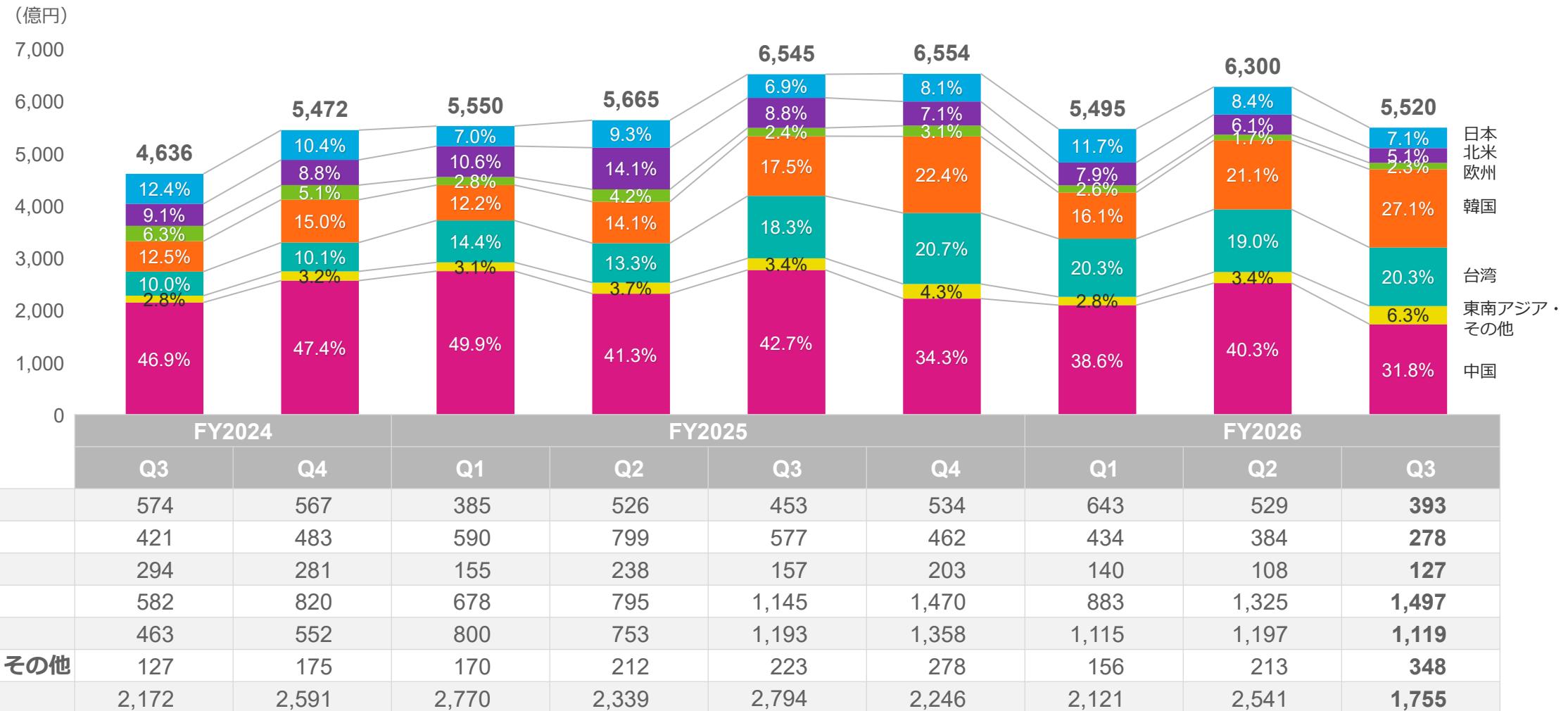

# 地域別売上高構成比

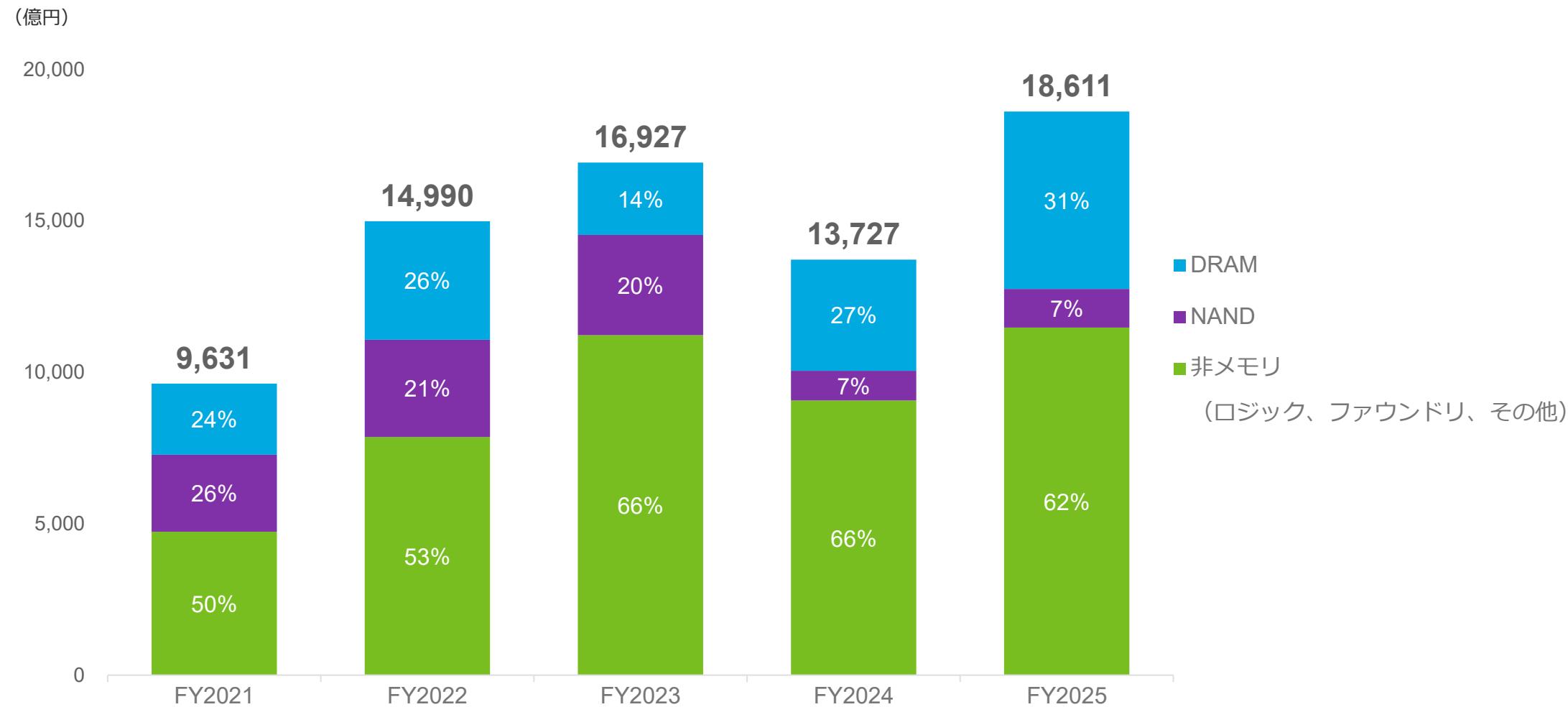

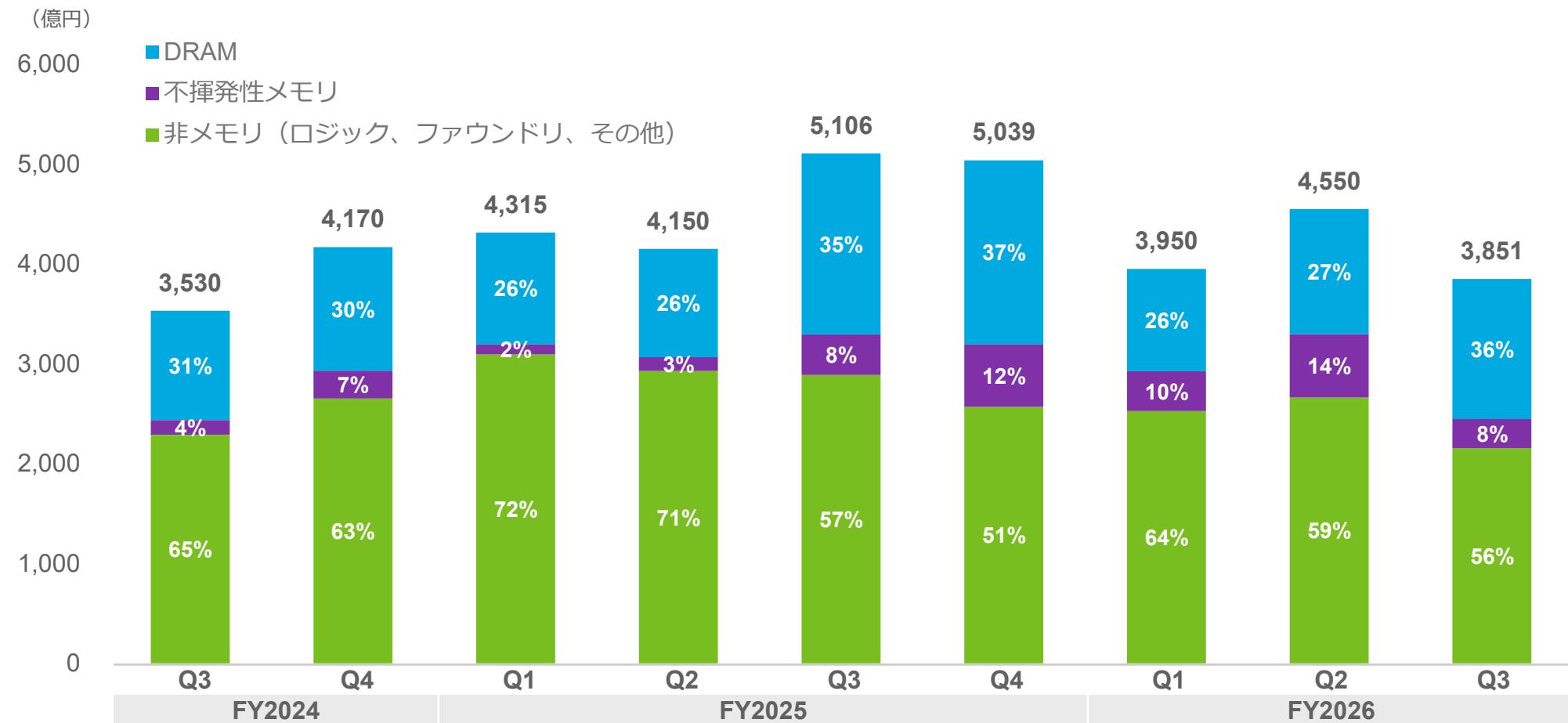

# SPE新規装置 アプリケーション別売上構成比

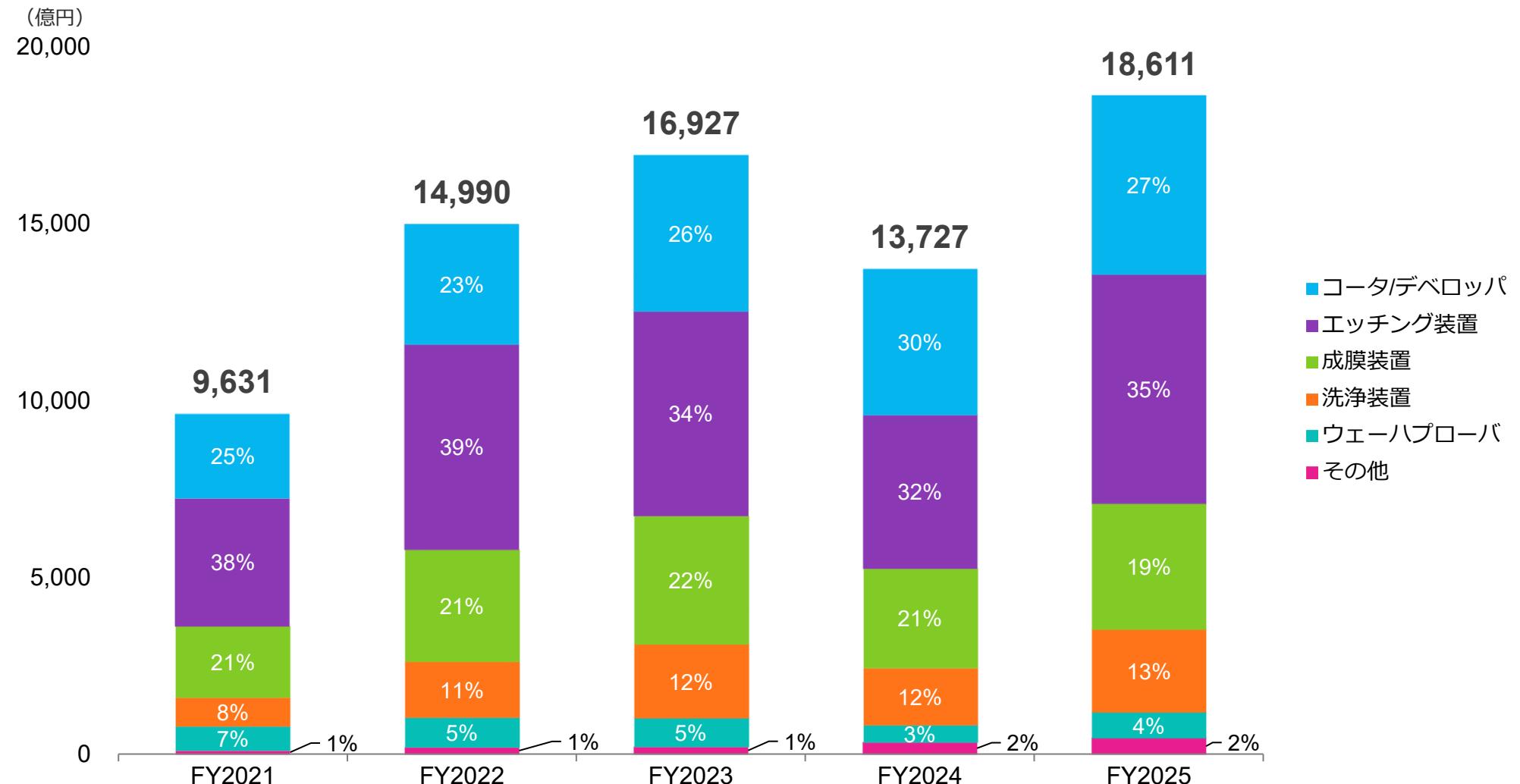

# SPE新規装置 製品別売上構成比

グラフは新規装置の売上高における構成比を示しています。フィールドソリューションの売上高は含まれておりません

# フィールドソリューション売上

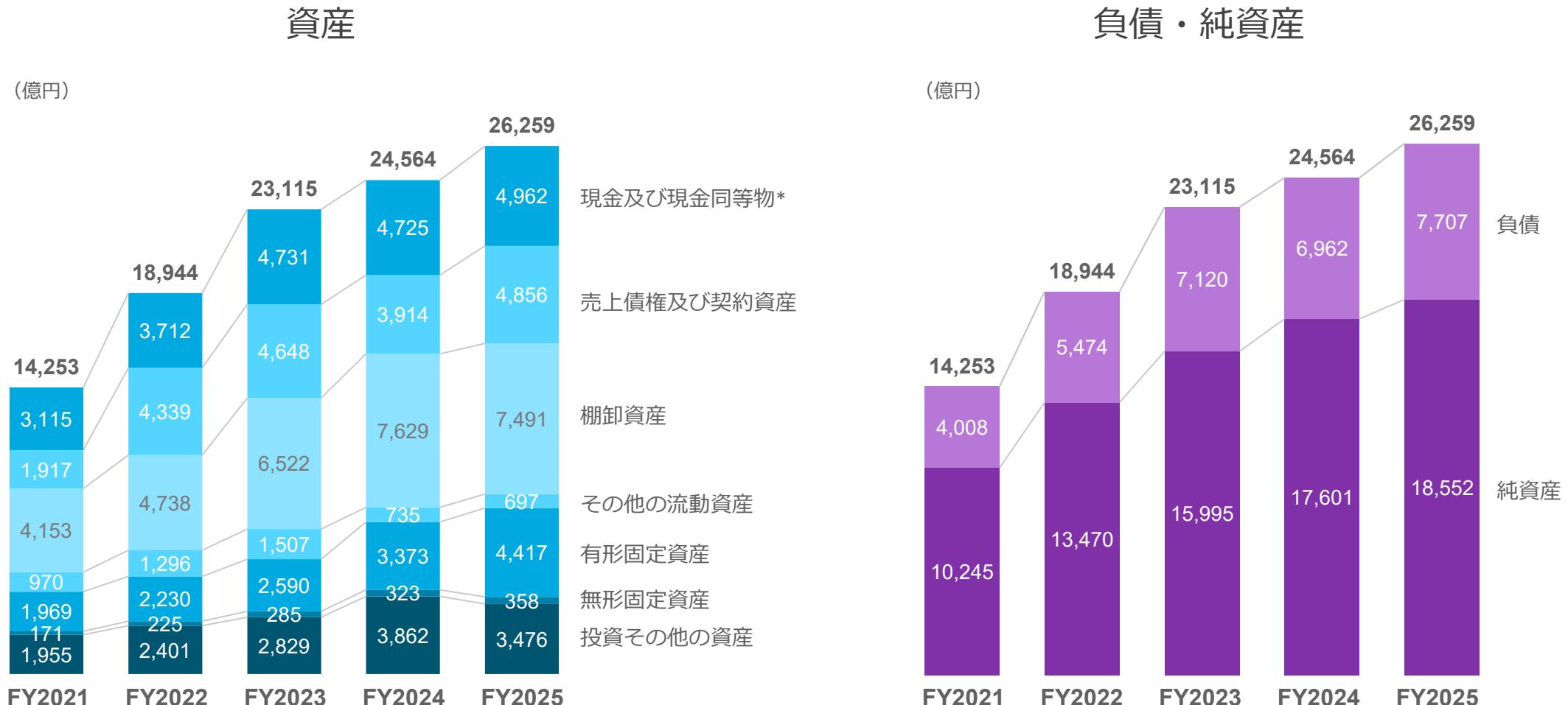

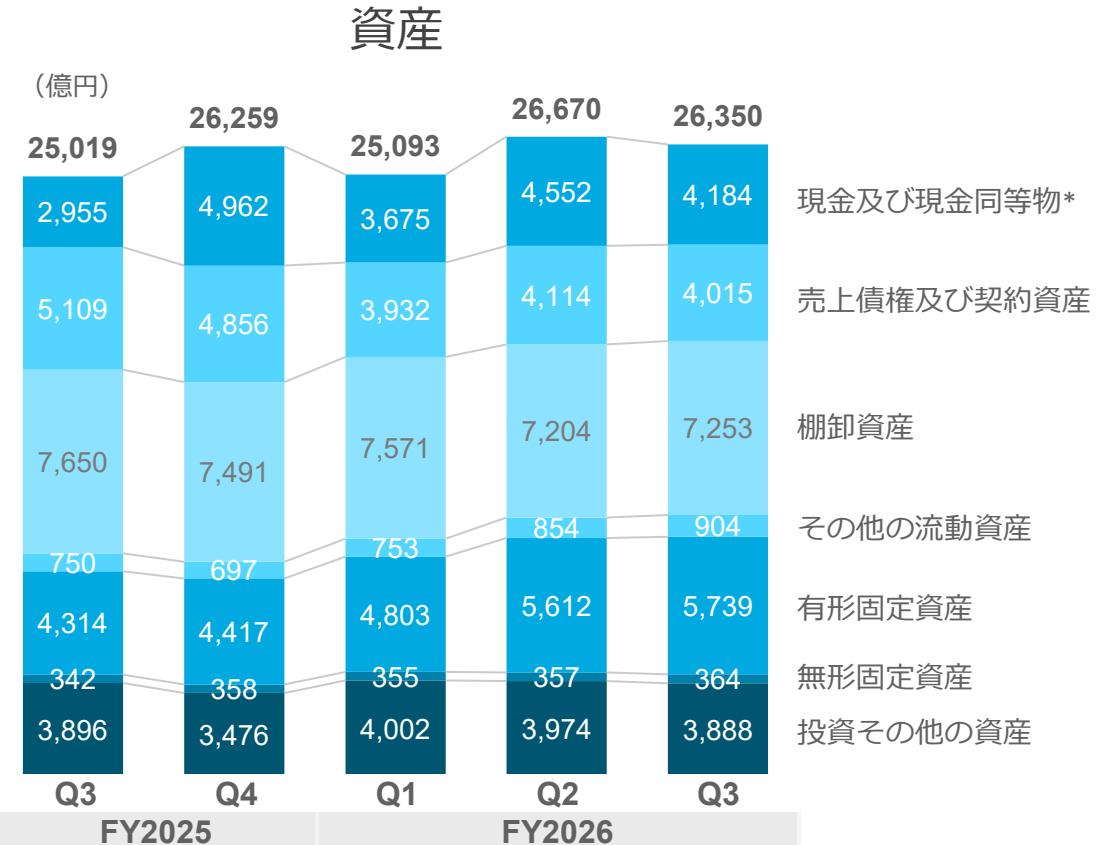

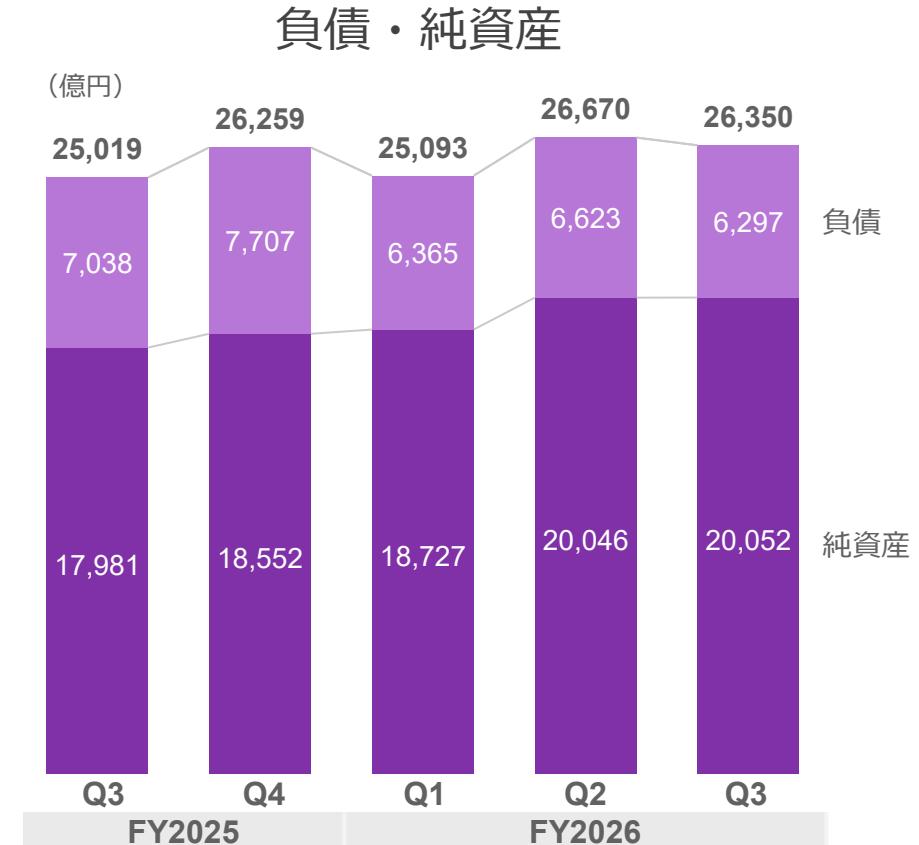

# 貸借対照表

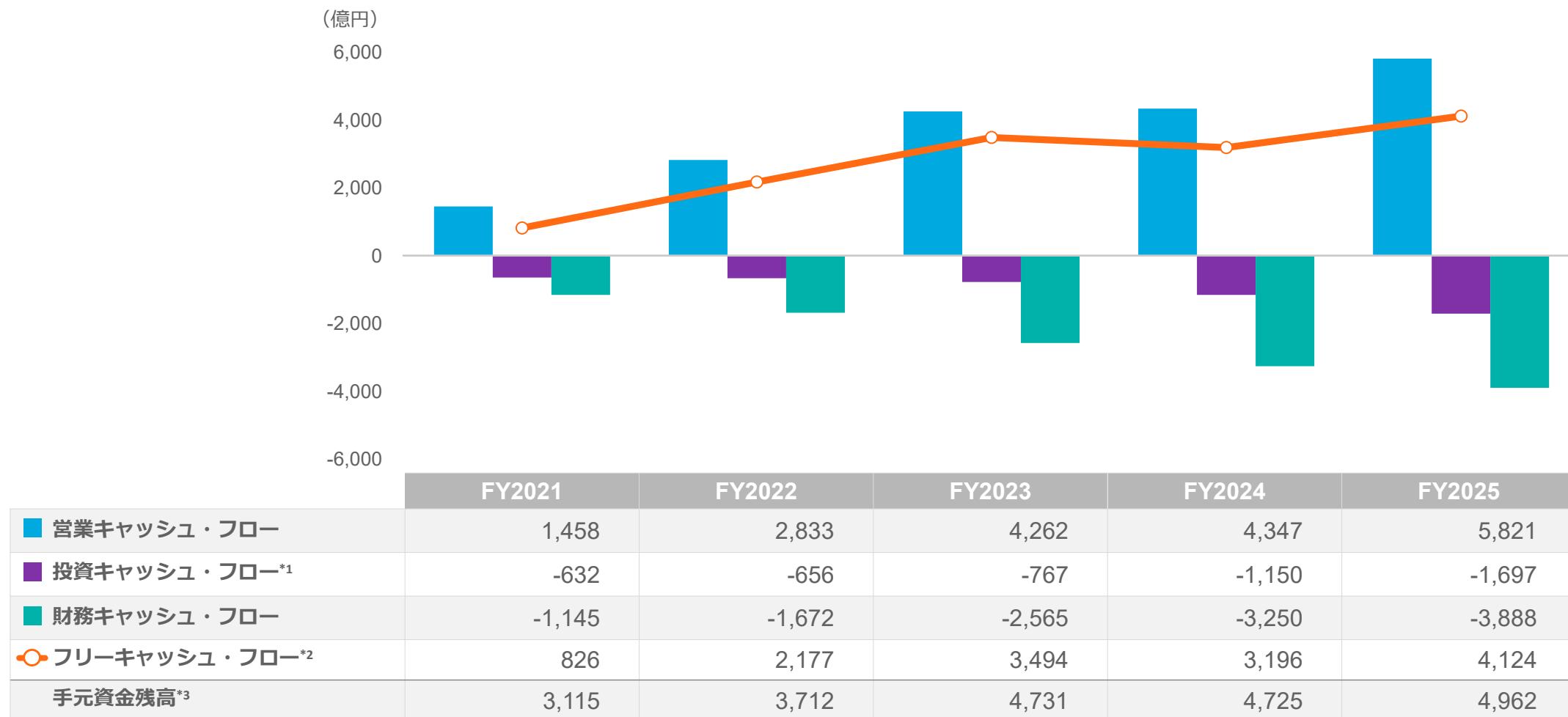

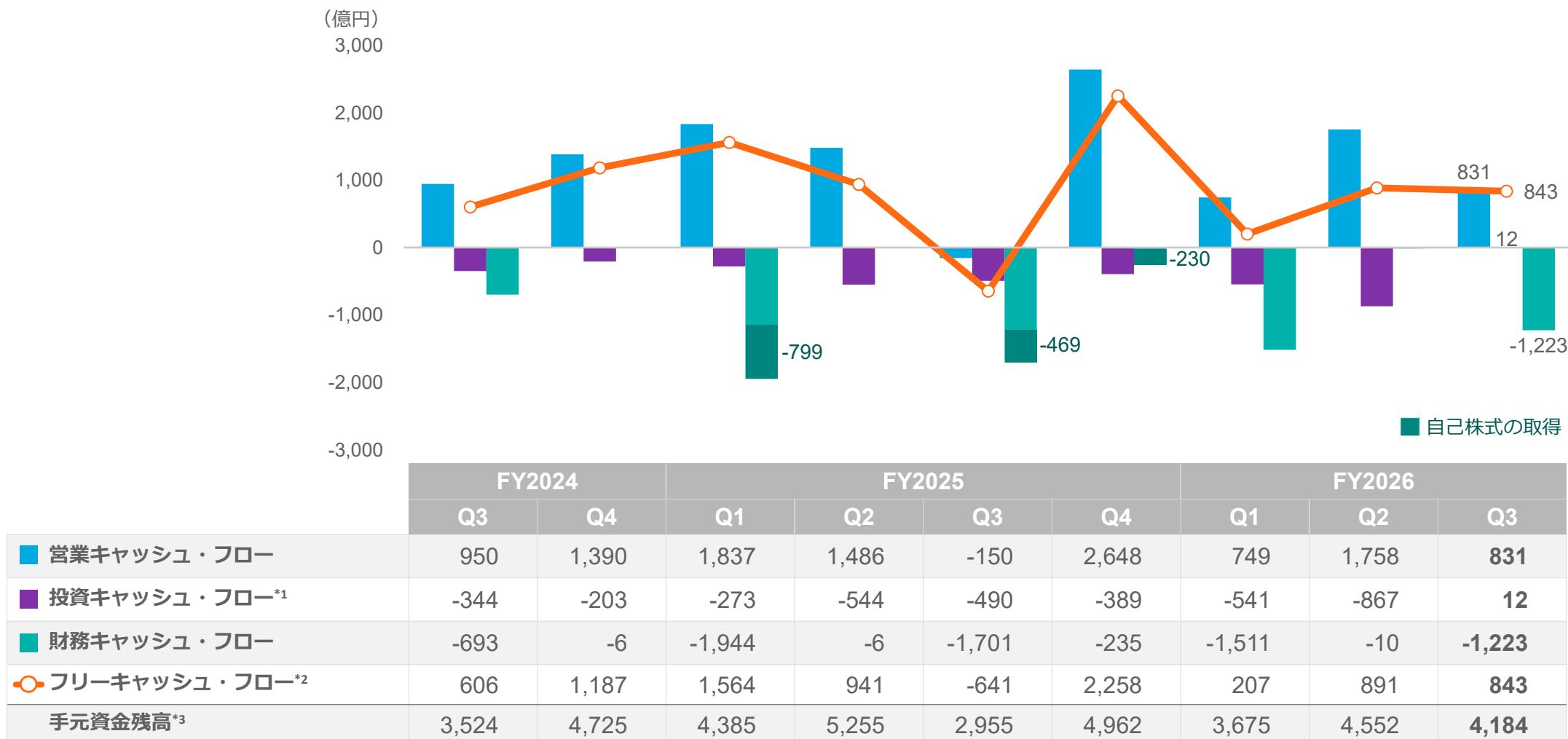

# キャッシュ・フロー

\*1 投資キャッシュ・フローは、定期預金および短期投資の増減を除いた金額です。

\*2 フリーキャッシュ・フロー = 営業キャッシュ・フロー + 投資キャッシュ・フロー（定期預金および短期投資の増減を除く）

\*3 手元資金は、現金及び現金同等物と満期日または償還日までの期間が3ヶ月を超える定期預金および短期投資の合計額です。

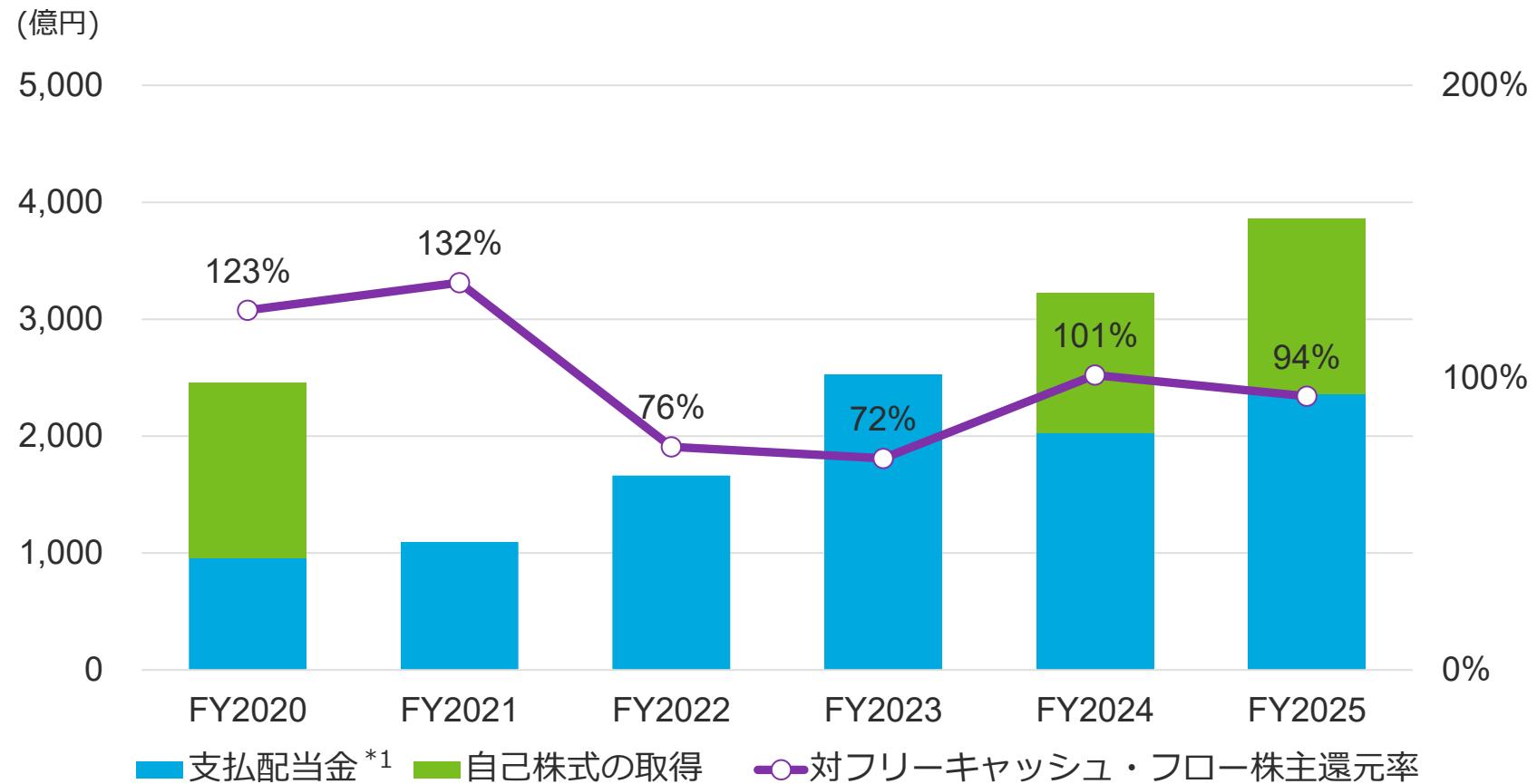

# 株主還元の動向

継続的に高水準のキャッシュ創出と株主還元を目指す

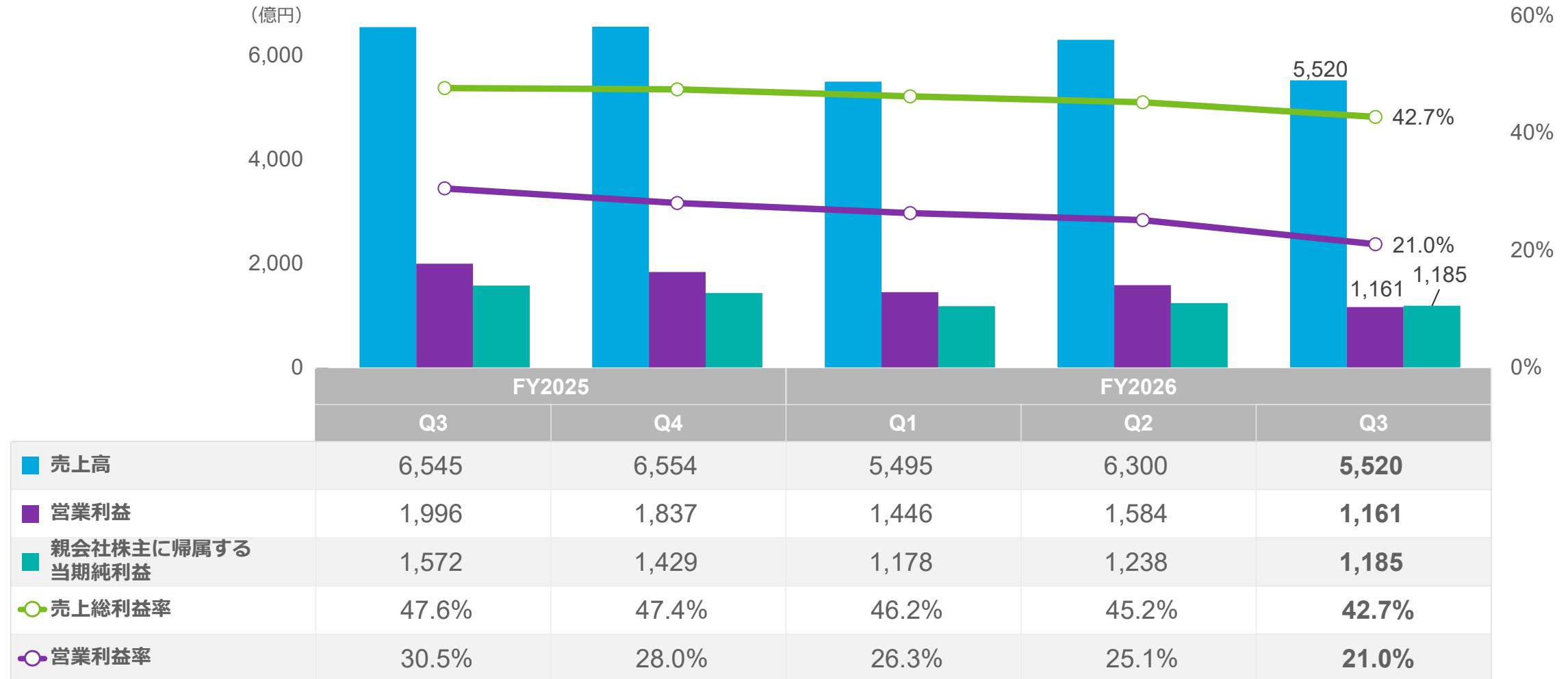

# 損益状況（四半期）

(億円)

|                 | FY2025 |       | FY2026 |       | Q3    | vs.<br>FY2026 Q2 | vs.<br>FY2025 Q3 |

|-----------------|--------|-------|--------|-------|-------|------------------|------------------|

|                 | Q3     | Q4    | Q1     | Q2    |       |                  |                  |

| 売上高             | 6,545  | 6,554 | 5,495  | 6,300 | 5,520 | -12.4%           | -15.7%           |

| 売上総利益           | 3,117  | 3,105 | 2,539  | 2,848 | 2,358 | -17.2%           | -24.4%           |

| 売上総利益率          | 47.6%  | 47.4% | 46.2%  | 45.2% | 42.7% | -2.5pts          | -4.9pts          |

| 販管費             | 1,121  | 1,267 | 1,092  | 1,264 | 1,196 | -5.3%            | +6.7%            |

| 営業利益            | 1,996  | 1,837 | 1,446  | 1,584 | 1,161 | -26.7%           | -41.8%           |

| 営業利益率           | 30.5%  | 28.0% | 26.3%  | 25.1% | 21.0% | -4.1pts          | -9.5pts          |

| 税金等調整前当期純利益     | 2,001  | 1,851 | 1,519  | 1,610 | 1,533 | -4.8%            | -23.4%           |

| 親会社株主に帰属する当期純利益 | 1,572  | 1,429 | 1,178  | 1,238 | 1,185 | -4.3%            | -24.6%           |

| 研究開発費           | 618    | 727   | 621    | 726   | 662   | -8.9%            | +7.2%            |

| 設備投資額           | 502    | 346   | 528    | 912   | 303   | -66.7%           | -39.6%           |

| 減価償却費           | 160    | 183   | 171    | 191   | 211   | +10.6%           | +31.7%           |

1. 当社製品の輸出売上は、原則円建てでおこなわれます。一部に外貨建売上および費用計上もありますが、極端な為替レートの変動がない限りにおいては、利益への影響は軽微です。

2. 利益率および増減率は、1円単位の金額をもとに計算しています。

3. FY2025は2024年4月～2025年3月の会計年度を指しています。FY2026は2025年4月～2026年3月の会計年度を指しています。

# 損益状況（四半期）

# 地域別売上高構成比（四半期）

# SPE新規装置 アプリケーション別売上構成比（四半期）

1. SPE (Semiconductor Production Equipment) : 半導体製造装置

2. グラフは新規装置の売上高における構成比を示しています。フィールドソリューションの売上高は含まれていません。

# フィールドソリューション売上高 (四半期)

(億円)

2,000

1,500

1,000

500

0

Q3

Q4

Q1

Q2

Q3

Q4

Q1

Q2

Q3

FY2024

FY2025

FY2026

1,044

1,193

1,181

1,395

1,415

1,389

1,412

1,603

1,616

# 貸借対照表（四半期）

\*現金及び現金同等物：現預金 + 短期投資等（貸借対照表上の表示は有価証券）

# キャッシュ・フロー（四半期）

\*1 投資キャッシュ・フローは、定期預金および短期投資の増減を除いた金額です。

\*2 フリーキャッシュ・フロー = 営業キャッシュ・フロー + 投資キャッシュ・フロー（定期預金および短期投資の増減を除く）

\*3 手元資金は、現金及び現金同等物と満期日または償還日までの期間が3ヶ月を超える定期預金および短期投資の合計額です。

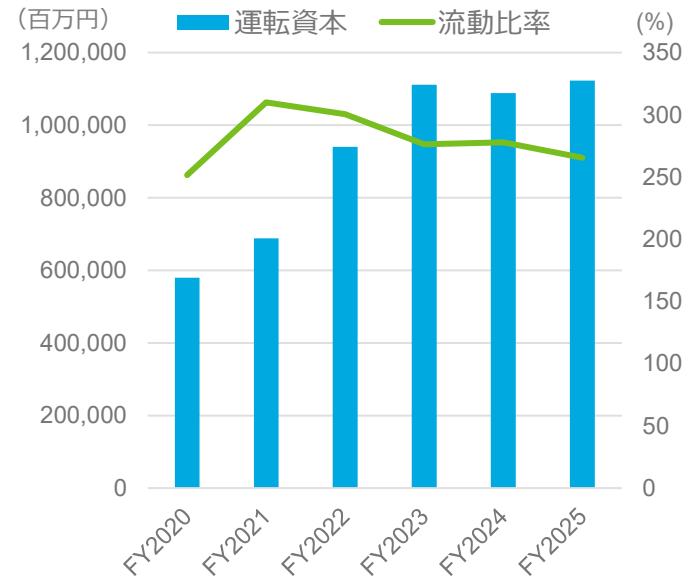

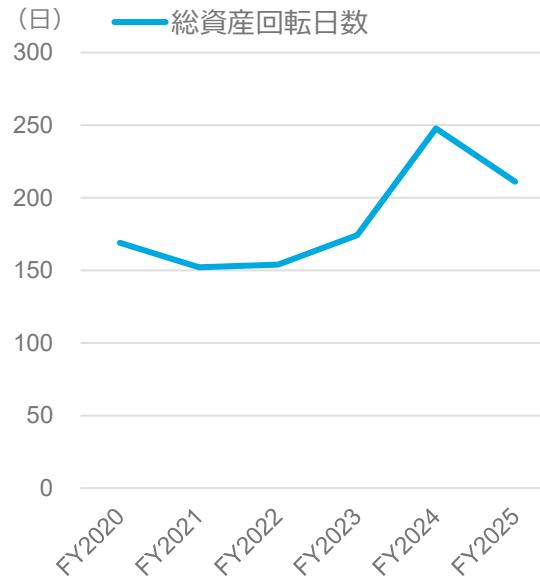

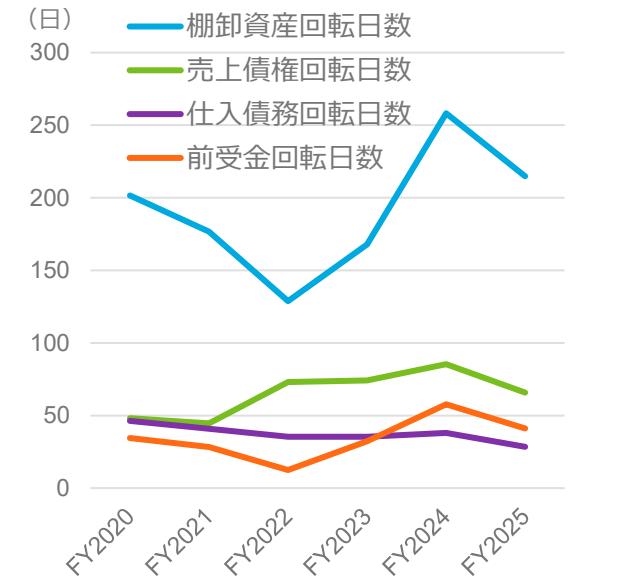

# 資産関連指標

## 運転資本および流動比率

※運転資本 = 流動資産 - 流動負債

※流動比率 = 流動資産 ÷ 流動負債 × 100

## キャッシュ・コンバージョン・サイクル (CCC)

※キャッシュ・コンバージョン・サイクル

= 棚卸資産回転日数 + 売上債権回転日数

- 前受金回転日数 - 仕入債務回転日数

## 棚卸資産・売上債権・ 仕入債務・前受金回収日数

※棚卸資産回転日数 = 期首・期末平均棚卸資産 ÷ 売上原価 × 365

※売上債権回転日数 = 期首・期末平均売上債権 ÷ 売上高 × 365

\*売上債権には契約資産を含む

※仕入債務回転日数 = 期首・期末平均買掛金 ÷ 売上原価 × 365

※前受金回転日数 = 期首・期末平均前受金 ÷ 売上高 × 365

# 過去10年間の主要財務データ

(百万円)

|                 | 2016年<br>3月期 | 2017年<br>3月期 | 2018年<br>3月期 | 2019年<br>3月期 | 2020年<br>3月期 | 2021年<br>3月期 | 2022年<br>3月期 | 2023年<br>3月期 | 2024年<br>3月期 | 2025年<br>3月期 |

|-----------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| 売上高             | 663,949      | 799,719      | 1,130,728    | 1,278,240    | 1,127,286    | 1,399,102    | 2,003,805    | 2,209,025    | 1,830,527    | 2,431,568    |

| 売上総利益           | 267,209      | 322,291      | 475,032      | 526,183      | 451,941      | 564,945      | 911,822      | 984,408      | 830,269      | 1,146,287    |

| 売上総利益率          | 40.2%        | 40.3%        | 42.0%        | 41.2%        | 40.1%        | 40.4%        | 45.5%        | 44.6%        | 45.4%        | 47.1%        |

| 販売費及び一般管理費      | 150,420      | 166,594      | 193,860      | 215,612      | 214,649      | 244,259      | 312,551      | 366,684      | 374,006      | 448,967      |

| 営業利益            | 116,789      | 155,697      | 281,172      | 310,571      | 237,292      | 320,685      | 599,271      | 617,723      | 456,263      | 697,319      |

| 営業利益率           | 17.6%        | 19.5%        | 24.9%        | 24.3%        | 21.0%        | 22.9%        | 29.9%        | 28.0%        | 24.9%        | 28.7%        |

| 経常利益            | 119,399      | 157,549      | 280,737      | 321,662      | 244,979      | 322,103      | 601,724      | 625,185      | 463,185      | 707,727      |

| 税金等調整前当期純利益     | 106,467      | 149,116      | 275,242      | 321,508      | 244,626      | 317,038      | 596,698      | 624,856      | 473,439      | 706,114      |

| 親会社株主に帰属する当期純利益 | 77,892       | 115,208      | 204,371      | 248,228      | 185,206      | 242,941      | 437,076      | 471,584      | 363,963      | 544,133      |

| 研究開発費           | 76,287       | 83,800       | 97,103       | 113,980      | 120,268      | 136,648      | 158,256      | 191,196      | 202,873      | 250,017      |

| 設備投資額           | 13,341       | 20,697       | 45,603       | 49,754       | 54,666       | 53,868       | 57,288       | 74,432       | 121,841      | 162,171      |

| 減価償却費           | 19,257       | 17,872       | 20,619       | 24,323       | 29,107       | 33,843       | 36,727       | 42,927       | 52,339       | 62,148       |

| 有利子負債           | -            | -            | -            | -            | -            | -            | -            | -            | -            | -            |

| 自己資本            | 562,369      | 643,094      | 767,146      | 880,748      | 819,301      | 1,012,977    | 1,335,152    | 1,587,595    | 1,746,835    | 1,839,929    |

| 総資産             | 793,367      | 957,447      | 1,202,796    | 1,257,627    | 1,278,495    | 1,425,364    | 1,894,457    | 2,311,594    | 2,456,462    | 2,625,981    |

| デット・エクイティ・レシオ   | -            | -            | -            | -            | -            | -            | -            | -            | -            | -            |

| 自己資本比率          | 70.9%        | 67.2%        | 63.8%        | 70.0%        | 64.1%        | 71.1%        | 70.5%        | 68.7%        | 71.1%        | 70.1%        |

| ROE             | 13.0%        | 19.1%        | 29.0%        | 30.1%        | 21.8%        | 26.5%        | 37.2%        | 32.3%        | 21.8%        | 30.3%        |

| 営業キャッシュ・フロー     | 69,398       | 136,948      | 186,582      | 189,572      | 253,117      | 145,888      | 283,387      | 426,270      | 434,720      | 582,174      |

| 投資キャッシュ・フロー     | -150,013     | -28,893      | -11,833      | -84,033      | 15,951       | -18,274      | -55,632      | -41,756      | -125,148     | -169,609     |

| 財務キャッシュ・フロー     | -138,600     | -39,380      | -82,549      | -129,761     | -250,374     | -114,525     | -167,256     | -256,534     | -325,012     | -388,836     |

| 1株当たり当期純利益      | 153.70       | 234.09       | 415.16       | 504.53       | 390.19       | 520.73       | 935.95       | 1,007.82     | 783.75       | 1,182.40     |

| 1株当たり配当金(円)     | 79.00        | 117.00       | 208.00       | 253.00       | 196.00       | 260.00       | 468.00       | 570.00       | 393.00       | 592.00       |

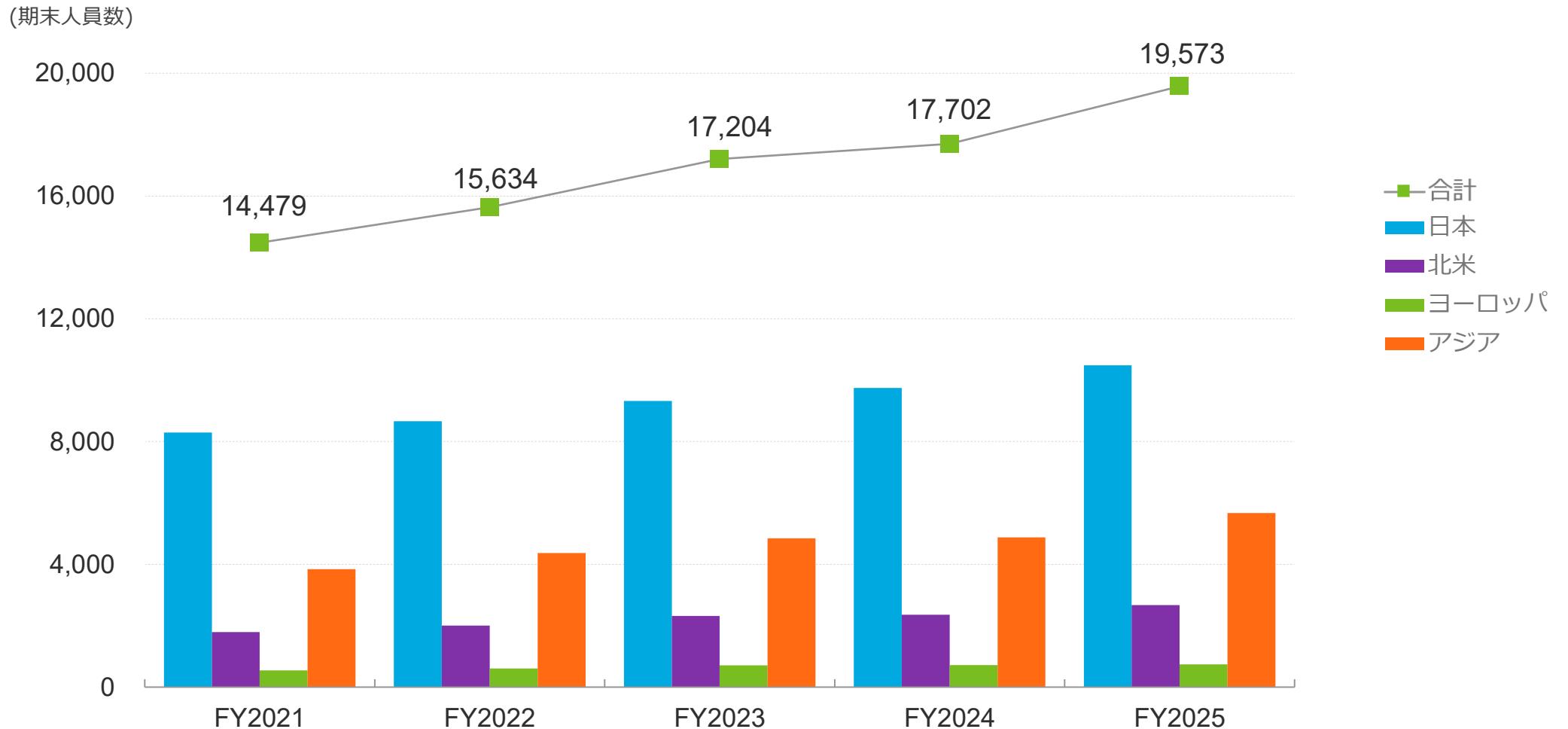

| 従業員数(人)         | 10,629       | 11,241       | 11,946       | 12,742       | 13,837       | 14,479       | 15,634       | 17,204       | 17,702       | 19,573       |

1. 2019年3月期より「『税効果会計に係る会計基準』の一部改正」(企業会計基準第28号 2018年2月16日)を適用しており、2018年3月期の「総資産」および「自己資本比率」は、当該会計基準を遡って適用した後の数値を記載しています。

2. 2022年3月期の期首より「収益認識に関する会計基準」(企業会計基準第29号)等を適用しています。

3. 2023年4月1日付で普通株式1株を3株に株式分割しております。1株当たり当期純利益、1株当たり配当金(円)は当該株式分割後の数値を記載しています。

本インベスターズガイドに掲載しているデータの一部は、当社ホームページに掲載している「データブック」からエクセル形式でダウンロードいただけます。是非ご利用ください。

<https://www.tel.co.jp/ir/library/fb/index.html>

# 従業員推移

- 将来見通しについて

本資料に記述されている当社の事業計画、将来予測などは、当社が作成時点で入手可能な情報に基づいて判断したものであり、政治経済情勢、半導体市況、販売競争の激化、急速な技術革新への当社の対応力、安全・品質管理、知的財産権、感染症の影響など、さまざまな外部要因・内部要因の変化により、実際の業績、成果はこれら見通しと大きく異なる結果となる可能性があります。

- 数字の処理について

記載された金額は単位未満を切り捨て処理、比率は1円単位の金額で計算した結果を四捨五入処理しているため、内訳の計が合計と一致しない場合があります。

- 為替リスクについて

当社製品の輸出売上は、原則円建てでおこなわれます。一部に外貨建売上および費用計上もありますが、極端な為替レートの変動がない限りにおいては、利益への影響は軽微です。

- Gartnerのデータについて（6、11ページ）

本プレゼンテーションにおいてガートナーに帰属するすべての記述は、ガートナーの顧客向けに発行された配信購読サービスの一部として発行されたデータ、リサーチ・オピニオン、または見解に関する東京エレクトロンによる解釈であり、ガートナーによる本プレゼンテーションのレビューは行われておりません。ガートナーの発行物は、その発行時点における見解であり、本プレゼンテーション発行時点のものではありません。ガートナーの発行物で述べられた意見は、事実を表現したものではなく、事前の予告なしに変更されることがあります。

## 本資料の取扱上の注意

当社の書面による承諾なしに複写、または

第三者への開示はできません。

東京エレクトロン

**TEL** および “TEL” は、東京エレクトロン株式会社の商標です。

TOKYO ELECTRON