JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

- Science Report

ムーアの法則50周年〜平面での微細化が行き詰まったら縦方向に積層へ〜

- 文/服部 毅

- 2015.03.27

連載第1回では、半導体の微細化の単位と、現在最小とされる14nm(ナノメーター)の意味について解説した。しかし、今後半導体の微細化はどこまで進むのであろうか。実は、半導体業界の関係者が拠り所としている集積化・微細化に関する指標がある。それが、今年提唱50周年を迎えた「ムーアの法則」である。今回は、この法則を拠り所にして微細化の将来を探ってみよう。

半導体はムーアの法則に従い発展してきた

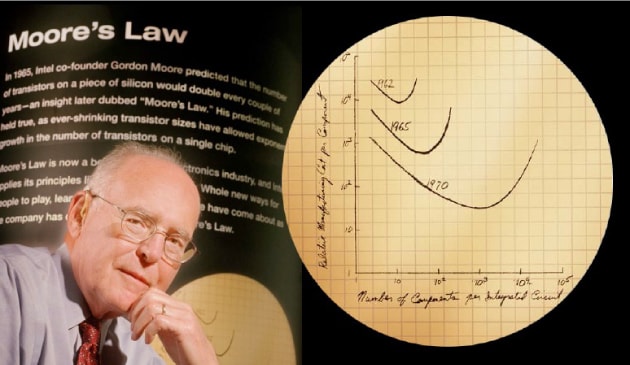

米インテル社の創業者の一人で名誉会長として知られるゴードン・ムーア氏(図1)は、米フェアチャイルド・セミコンダクタ社で集積回路の研究開発担当ディレクターだった1965年に、電子技術専門週刊誌 "Electronics"の「10年後の電子産業予測」特集に、集積回路の集積度に関する予測論文を寄稿した。その要旨は次のようなものであった。

「部品(トランジスタ)あたりのコストが最小になるような複雑さ(集積度)は、今まで毎年およそ2倍の割合で増大してきた。短期的には、この増加率は上昇しないまでも現状を維持することは確実である。長期的には、やや不確実であるとはいえ、少なくとも今後10年間ほぼ一定の率を保てるだろう」*1

|

ムーア氏は、この論文執筆10年後の1975年に、集積回路の集積密度の推移を調べ直して「半導体の集積密度は2年で倍増する」と修正した。その後、この予測は「ムーアの法則」として知られるようになり、半導体のみならず電子産業界の関係者にとっての絶対的な拠り所となった。この経験則は、一般には「半導体の集積度は、18~24カ月で倍増する」という表現で知れ渡っているが、ムーア氏自身は18カ月と言った覚えはないと言っている。米インテルのMPUの性能が18カ月で倍増してきたために、それと混同されたのではないかと言われている。また、1970 年以来4半世紀にわたり「3年で4倍」の割合で増加してきたDRAM(Dynamic Random Access Memory)の記憶容量の成長率が「1.5年(18ヶ月)で2倍」に相当するところから、メモリービジネス従事者は好んで「18カ月で2倍」と言う表現を使ってきた経緯もある。

そんなムーアの法則は今年4月に「提唱50周年」を迎えた。この50年間、半導体はムーアの法則に沿う微細化・高集積化・低コスト化によって目覚しい発展を遂げ、それを利用した電子機器のおかげで快適な生活や効率的なビジネスが現実のものになった。

ムーアの法則はまだまだ終焉しない

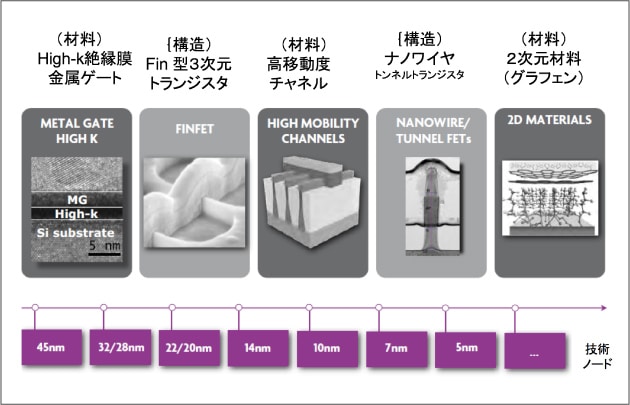

この50年間、回路線幅を主に微細化することで集積度を上げてきた。微細化が困難になるたびに、「ムーアの法則は破たんした」、「ムーアの法則は終焉した」と何度も言われながらも、この法則はいまだ健在である。微細化・集積化の困難さは増す一方だが、インテルは率先して新材料・新構造を大胆に導入して乗り越えてきた。いずれ、基板のチャネル領域に、従来のシリコンに替わってゲルマニウム(Ge)やガリウム・インジウム・ヒ素(GaInAs)のような2種類以上の元素を組み合わせた化合物半導体(III-V族半導体)が採用されることが想定され、伝統的なMOSトランジスタの構成材料や構造は、今後一変することになるだろう。

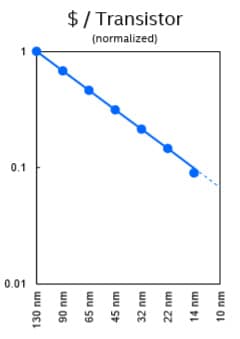

今年2月にサンフランシスコで開催された半導体集積回路に関する最高峰の国際会議International Solid-State Circuits Conference (ISSCC)2015で、インテルでプロセス開発を主導しているシニアフェローのマーク・ボーア氏は、「14nmプロセスでは、密度を大幅に高められたため、トランジスタ当たりのコストが下がった(図2)。こうした傾向は、次の10nmや7nmの世代までは確実に続き、ムーアの法則は今後も継続できる」と述べた。同じ会議で、韓国サムスン電子のキナム・キム社長も「5nmまでは根本的な技術的困難なく微細化を進められる」と述べた。インテルやサムスンとも研究協業を進め、微細化で世界をリードするベルギーのコンソーシアムIMECも、今後、材料やデバイス構造を交互に更新することにより5nmまで微細化を進める目処が立っている(図3)」(プロセス開発担当SVP のアン・スティーガン氏)としている。

|

|

たしかに、"Atoms cannot scale"(原子は縮小できない)と言われるように、いずれ物理的限界は来るだろう。でも、そんな先のことは現段階では誰にもわからない。もっとも、物理的限界の前に経済的な(コスト上の)限界が先に来る可能性が高いだろう。

ムーアの法則は,もともと微細化に関する法則ではなく集積化に関する法則であるから、平面的な微細化が無理になったら、縦方向に3次元的に積み上げてチップ間をSi貫通ビア(TSV;Through Silicon Via)*2で串刺しにすれば、ムーアの法則は終焉せず、更に延命するだろう。このため、3次元化、とりわけTSVプロセスのコストダウンは必須である。 3次元実装は, ロジックよりもメモリの方が先に実用化段階に入っているので、次にその動向を見てみよう。

微細化に見切りをつけて3次元化するフラッシュメモリ

微細化が最初に行き詰まる半導体デバイスは、いままで最も速いペースで世代交代が行われてきたNANDフラッシュメモリ*3であろう。フラッシュメモリ市場において、トップを走るサムスンに肉薄する東芝は現在15nm フラッシュメモリ(ワード線の配線ピッチの1/2(=ハーフピッチ)の長さが15nmの製品)の生産を同社四日市工場(三重県)で始めており、今後、さらにはその先へむけて微細化を検討している。

しかし、微細化によって記憶素子に蓄積できる電子数が極端に少なくなり、さらにはメモリセル間の干渉の増大などで大容量メモリの信頼性(書き換え寿命や読み出し誤り率)が急激に悪化してきており、デバイス特性としての物理的限界を迎えようとしている。

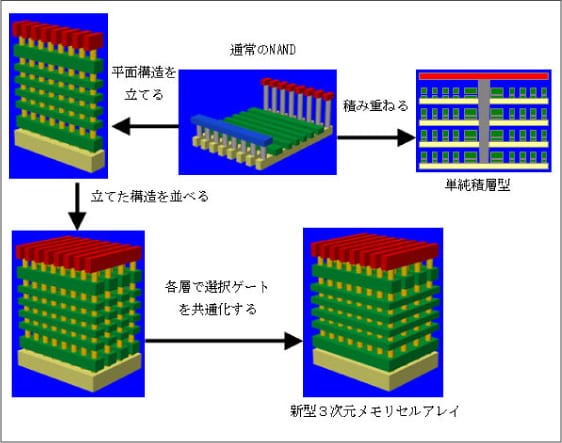

微細化をすることなく大容量化とビットコストの低減を図る方法として新たに登場してきたのが、セルアレイ(セルの配列)を上に積み上げていくメモリの3次元化である。当初、平面メモリセルアレイをそのまま積み上げていく方式が考案されたが、メモリ層を一層追加するたびに最小線幅のパターンを焼き付けるリソグラフィ工程(製造工程の中で最もコストが高い露光の工程)を経ねばならず、コスト低減が出来なかった(図4右上)。

そこで、東芝は積層数によらず露光及び加工工数を一定に保てる手法を開発し、すでに2007年にそのコンセプトを公表している(図4左および下)。後にBiCS (Bit Cost Scalable) 技術と名付けられた本構造の加工プロセスでは、まず、ゲート電極と層間絶縁膜を互い違いに積み重ねた積層構造に、最上層から最下層まで貫通する孔を一度に開け、その孔に柱状のシリコンを埋め込む。これにより、ゲート電極層が一定間隔ごとにシリコンの柱を覆う構造となり、各交点にあらかじめデータ保持用の窒化シリコン膜などを形成しておけば、NANDセルとして機能する。東芝は、最初の発表以来、7年以上に渡り改良を重ね、実用化めざして研究を続けている。

|

一方、サムスンは、20nmで微細化をさっさとあきらめて、メモリセルを垂直に積層した3次元セル構造のNAND型フラッシュメモリ(128Gビット"Vertical NAND")の量産を2013年に開始した。同社の特許である「3Dチャージ・トラップ・フラッシュ(CTF)技術」と垂直に積み重ねたセル間を接続する垂直配線プロセス技術によって、特殊エッチングを可能にし、24層のセル層を重ねている。これらの技術により、20nm製造プロセスを利用した従来のプレーナ(平面)型NANDメモリに比べ2倍以上の記録密度を実現したという。

東芝はとりあえず従来の平面構造でフラッシュメモリの微細化の極限を極め、それから3Dへ移行し、いずれ48層から参入することとし、技術を完璧に仕上げてから製品化しようとしているのに対して、サムスンは、微細化に見切りをつけて、さっさと3次元化に移行し、24層積層技術が一応出来あがった時点で製品化し、市場の反応を見ながら改良を重ね、最近は32層製品を実用化した。両者企業文化の違い、そして平面から3Dへの切り替え時期に関する戦略の違いが今後の両社のビジネスにどのように影響するか注目される。

DRAMも3次元化で高性能化

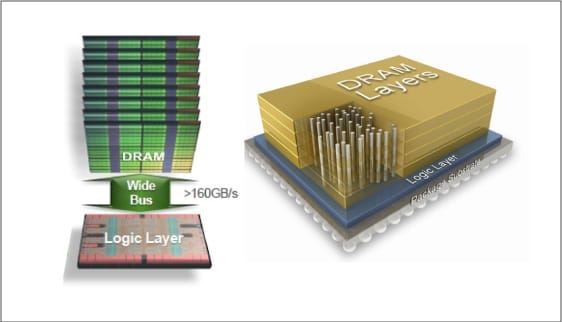

フラッシュメモリだけではなく、DRAMの微細化もワード線が20nmをきるあたりで物理的限界に直面するだろう。メモリ機能に必要なキャパシタ(蓄電池)の容量を維持できなくなるからである。フラッシュと同様のデバイス動作原理上の限界である。デバイスとしての物理的限界に達した後は、Si貫通ビア(TSV)を用いた3次元実装が採用される方向である。すでに、米マイクロン・テクノロジーは、複数のDRAMチップと一個のコントローラ・チップを積層し、多数のTSVで接続した"Hybrid Memory Cube (HMC)"をハイエンドのネットワーク機器やスーパーコンピュータ向けに実用化している。このチップは、DRAMのビット不良や、TSVに起因する不良を修復するとともに、マイクロプロセッサと高速通信するインターフェースの役割も果たす。

|

HMCのバンド幅(マイクロプロセッサとの間で1秒間にやり取りできるデータ量)は160Gバイト/秒と、積層DRAMを外側からワイヤボンディングで接続する従来方式の15倍に改善され、ビット当たりのエネルギー消費量も70%削減できたとしている。

ハイエンド向け3次元DRAMが普及してTSVのコストダウンが図れれば、3次元LSIがいずれはスマートフォンなどの民生電子機器にも普及することが期待される。

半導体デバイスの高集積化は、2次元平面での微細化と3次元積層の両面で今後も極限まで進化し続けるだろう。次回は、半導体製造コスト低減のもう一つの手段であるシリコンウェーハの大口径化について解説する。

[第3回へ続く][ 脚注 ]

- *1出所はGordon Moore

- "Cramming more components onto integrated circuits", Electronics Magazine , McGraw-Hill, New York, 1965.4.19. カッコ内は本稿著者加筆。当時は、まだディスクリート(個別)トランジスタ全盛の時代で、コスト高の集積回路はいらないという風潮が蔓延していたため、集積回路を宣伝するためにこの論文を書いたのであって、予測にそれほど自信はなかったとムーア氏は後年回顧している。

- *2Si貫通ビア(Through Silicon Via:TSV)

- 複数枚の半導体チップを垂直に重ねて、そのシリコン基板内部を垂直に貫通する孔のこと。この穴に棒状の電極をいわば串刺しにしてチップ相互を電機的に接続する。半導体チップの3次元実装に必須の技術だが、プロセスが複雑なためコスト高で、放熱や信頼性の問題もあり、普及にはもうしばらく時間を要す。

- *3NANDフラッシュメモリ

- 電源が切れてもデータを保持できる不揮発性記憶素子で、情報を一括して瞬時に消去できることを特徴としている。USBメモリやメモリカード、携帯音楽プレーヤー、スマートフォンなどに広く普及している。NANDは否定論理積とよばれる論理回路の形式を指す。DRAMやロジック回路の配線にはコンタクトホール(半導体と金属をつなぐ穴)があるが、フラッシュメモリの配線であるワード線にはコンタクトホールがないので、配線の微細化が最も進んでいる。

- Writer

-

服部 毅(はっとり たけし)

-

ソニー(株)に30年余り勤務し、中央研究所で半導体基礎研究、半導体事業本部でデバイス・プロセス開発から量産ラインの歩留まり向上まで広範な業務を担当。この間、本社経営/研究企画業務、米国スタンフォード大学大学院留学、同集積回路研究所客員研究員等も経験。2007年に技術・経営コンサルタント、国際技術ジャーナリストとして独立し現在に至る。工学博士。The Electrochemical Society (ECS)フェロー・理事。韓国漢陽大学工学部客員教授。主な著書に『シリコンウェーハ表面のクリーン化技術(リアライズ社)』、同英語版(Springer社)、『半導体MEMSのための超臨界流体(コロナ社)』『メガトレンド半導体2014ー2023(日経BP社)』がある(共に共著)。