JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

- Science Report

- サイエンス リポート

半導体業界構造を一変させる技術!?「チップレット」とは?

- 文/伊藤 元昭

- 2023.04.26

これまで半導体チップは、素子や回路の配線幅を微細化することで、高性能化・多機能化・低消費電力化・低コスト化を図ってきた。微細化というたった1つの技術開発アプローチで、トレードオフを抱えることなくチップの価値を向上できた。ところが近年、半導体の微細加工技術が高度化するにつれて、製造時の歩留まりを高めることが困難になってきた。たとえ微細加工できても、半導体ビジネスとして成立しないほどわずかな良品しか作れない例も出てきている。微細加工技術の進歩だけでは、半導体技術の明るい未来を描けないようになってきたのである。ただし、こうした窮地を救う新たな技術が出てきている。それが「チップレット」である。チップレットを適用することで、微細化の効果を継続できるだけでなく、チップに新たな価値をもたらすメリットも得られるようになる。さらに、半導体産業の業界構造や勢力図を一変させる可能性すら出てきている。

スマートフォンや自動車、そして安全保障上の装備・設備まで――。半導体は、現代の生活やビジネス、社会活動に欠かせない最重要物資のひとつとなった。もはや半導体を応用したエレクトロニクス機器の利用なくして、持続可能で豊かな未来は描けないような状況だ。

これまでの半導体チップは、チップ上に集積する素子や回路を描く配線の線幅を継続的に微細化させることで進化してきた。素子や配線が微細になれば、小さなチップ内により大規模な回路を集積可能になり、しかも1つひとつの素子の高性能化・低消費電力化も実現できる。そして、より大規模な回路を、より小さなチップに集積できるため、電子回路の製造コストも低減できる。つまり、微細加工技術の進歩は、半導体チップを進化させるうえで、いいことづくめの“魔法”のような手法だったのだ。

ところが近年、この“魔法”が徐々に解けつつある。微細加工技術の進歩によってチップ上に集積可能な素子の数が1.5年または2年ごとに倍増するという経験則「ムーアの法則」は、先行きに不安を抱えているとはいえ依然として継続できている。しかし、最先端の微細加工技術が高度すぎて、製造中に生じる不良が高頻度で発生(歩留まりが低下)するようになった。その結果、同じ大きさのチップを作る際の製造コストが、半導体メーカーのビジネスとして成立しないほど増大する例が出てきた。たとえ、チップの製造が可能だとしても、価格が高すぎては、広く応用することはできない。こうした傾向は、微細化の度合いが進むほど顕著になってきている。

小さなチップを1パッケージに収める技術「チップレット」とは

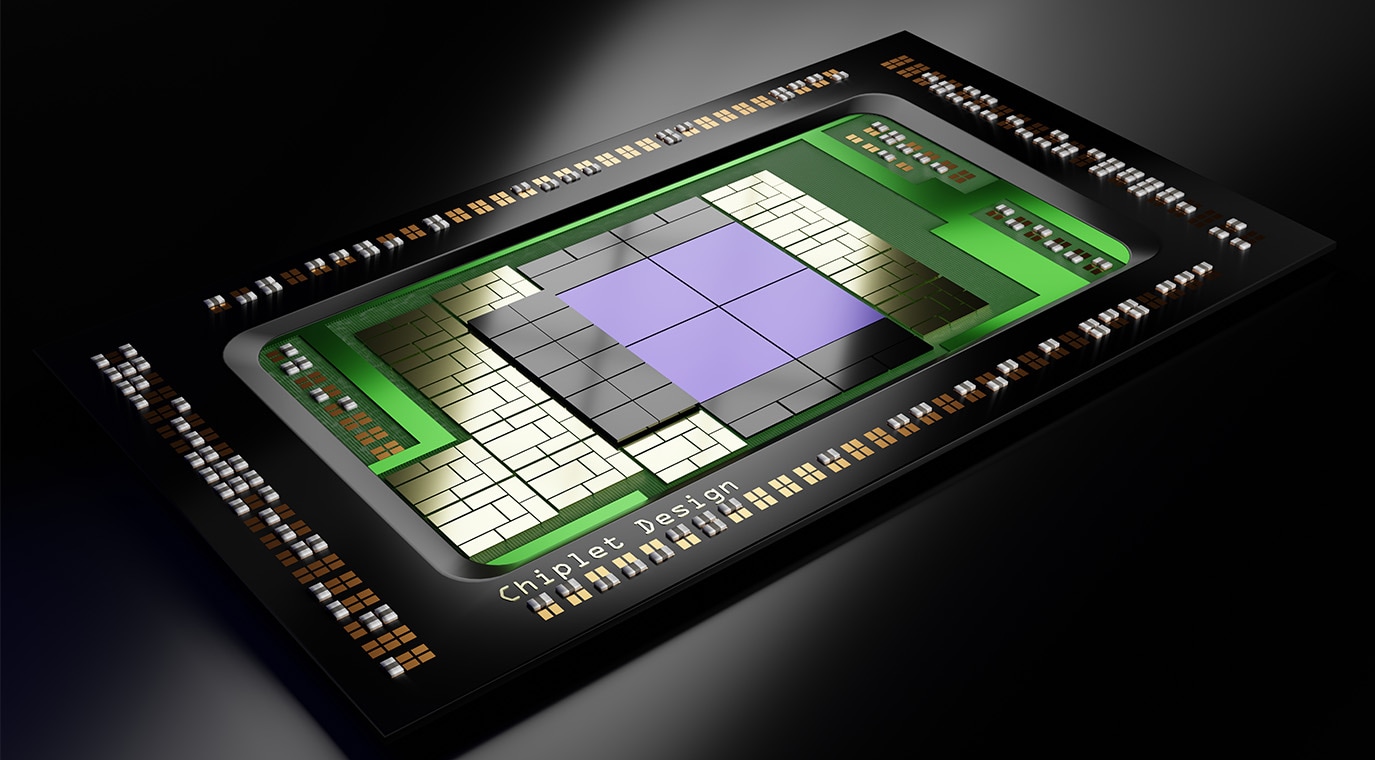

半導体チップの進化を支える微細加工技術の進歩の効果を維持していくため、注目され、適用事例が増えている新たな技術がある。「チップレット」である(図1)。チップレットとは、これまで1チップに集積した大規模な回路をあえて複数の小さなチップに個片化し、「インターポーザ」と呼ぶチップレット間をつなぐ基板上に乗せて大規模化して1パッケージに収める技術である。豚の子どもは英語でピッグレットと呼ばれるが、同様に小さなチップという意味を込めてチップレットと呼ばれている。

- [図1] チップレットのコンセプト

- 出典:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1

チップレットなくして、最先端半導体チップなし

大規模回路を個片化するチップレットを導入することで、なぜ低下傾向だった半導体チップの歩留まりを改善できるのか。その理由を、少し詳細に説明したい。

同じ微細加工技術で作れば、製造中に、ほぼ一定の確率でチップ上の任意の場所で不良が発生する。製造条件のバラつきや、不良の原因となる不純物やゴミの混入は変わらないからだ。そして、チップ面積(チップレット)が大きいほど、不良チップが生まれる頻度は高くなり、歩留りが下がる。ここで重要な点は、たとえチップの一部に不良が発生しただけでも、チップ全体が不良となってしまうことだ。

無理をしてチップ面積が大きな大規模回路を一括形成するよりも、回路を個片化して面積を小さくしたチップレットを寄せ集めた方が大規模回路全体の歩留まりは高まる。チップレット1つひとつの歩留まりが高まるだけでなく、良品のチップレットだけを選別して大規模回路を形成できるからだ。

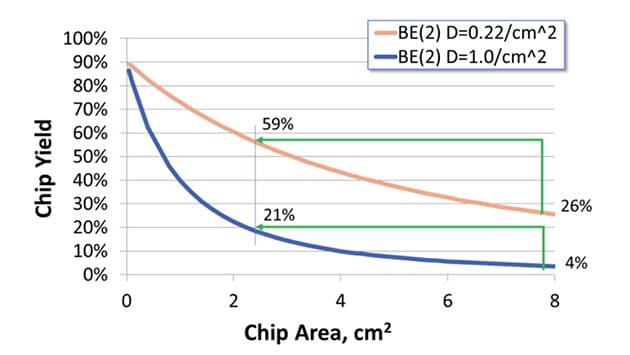

実際に、歩留まり向上効果があることは、半導体の学会などの場において定量的に示されている(図2)。あるサーバー用チップに搭載する回路全体を仮に1チップで形成すると、777㎟という巨大なチップになる。これを4個のチップレットに個片化すると、各チップレットの面積は213㎟になる。すると、量産初期の歩留りは、1チップ化した場合にはたった4%だったものが、チップレット化すると21%にまで向上する。

- [図2] チップ面積と製造時の歩留りの関係

- 青色の曲線が量産初期のデータ、オレンジ色の曲線が量産成熟期のデータ。

出典:Greg Yeric, arm community,“Three Dimensions in 3DIC - Part I”, April 2, 2018

さらに量産成熟期には、1チップ化の歩留まり26%が、チップレット化により59%にまで高まる。そして、1枚のウェーハから切り出せる1チップ化のチップ数が69個であるのに対し、チップレット化すると273個に増える。これらのデータから計算できる成熟期に1枚のウェーハから得られる良品の数は、1チップ化の場合69×26%=17個であり、チップレット化すると同等の回路構成を実現するのに4個分必要になるので、273×59%÷4個=40個となる。商品化できるチップ数の数には2倍以上の開きがあり、量産時の収益率の差は歴然である。

異種回路や他社チップの混載や3次元積層が可能に

チップレットの利用には、歩留まり向上効果以外にも、多様なメリットがある。

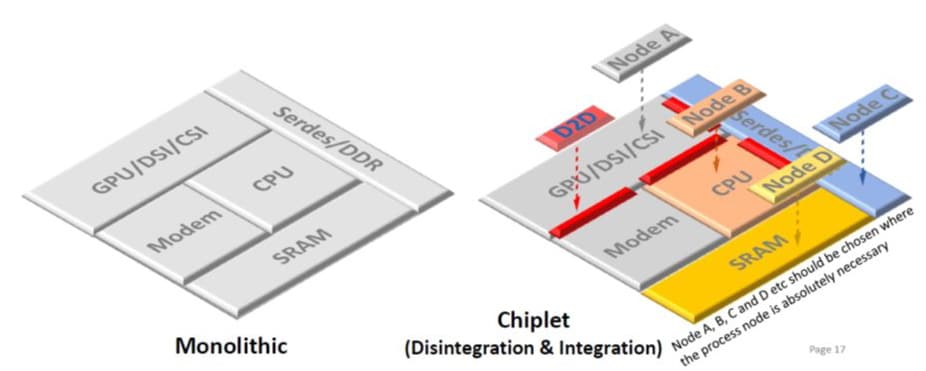

まず、異なるプロセスノード(微細加工技術の世代)、異なるプロセス技術(ロジック、メモリー、アナログIC、RF回路、パワー半導体など)のチップレットを組み合わせた大規模回路を、1つのパッケージに収めることが可能になる。こうした技術は、「ヘテロインテグレーション(HI)」と呼ばれている(図3)。

1チップ化した最先端半導体チップでは、チップ上に集積する回路をすべて、最先端技術で作っていた。ところが、CPUやSoC(System on Chip)上に搭載する回路の中には、必ずしも最先端技術で作らなくても、求める性能を実現できるものも多い。そうした回路を最先端技術で作ると、高コスト化と歩留り低下を招く可能性がある。また、DRAMやフラッシュメモリーやRF回路など、ロジック回路とは製造技術が根本的に異なり、そもそも1チップ化が困難な回路もあった。チップ上の全回路を回路特性に応じて分別し、チップレット化すれば、最も適した製造技術で作ることができ、さらなる高性能化、多機能化、低コスト化が実現する可能性が出てくる。

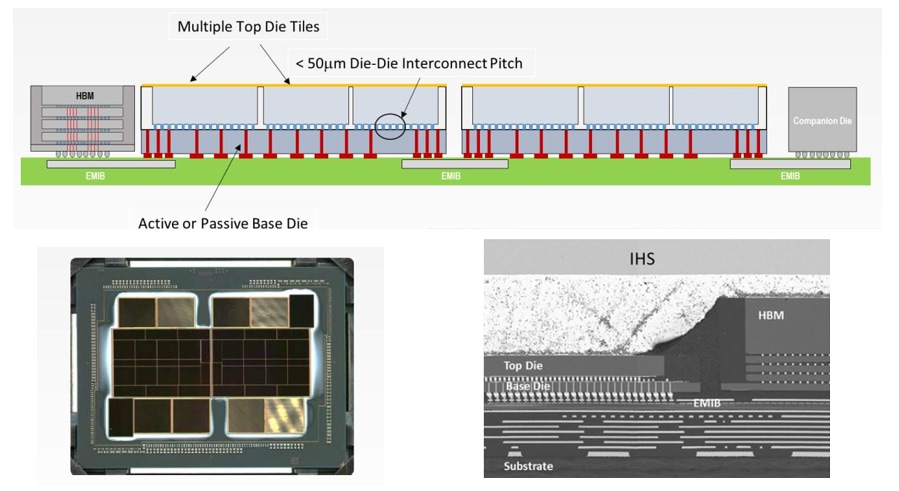

- [図3] チップレットを活用したヘテロインテグレーションの実践例

- Intel(アメリカ)のGPU「Ponte Vecchio」の実装技術の構成(上)、チップ全体でのチップレットの配置写真(左下) 、実装後のチップレットとインターポーザの断面写真(右下)

出典:Intel

さらに、別の会社が設計・製造したチップレットを集めて、大規模なチップを製造できるようにもなる。こうしたメリットを生かしやすくするため、チップレット間インタフェースの通信方式を標準化し、オープンなチップレットエコシステムの構築を狙うコンソーシアム「UCIe(Universal Chiplet Interconnect Express)」が設立され、最初の仕様である「UCIe 1.0」が公開された。

チップレットで半導体の業界構造や勢力図が一変する可能性も

チップレットの利用が広がることで、半導体産業の業界構造や勢力図が一変する可能性が出てきている。

これまでの最先端半導体チップの開発では、大規模回路の1チップ化を前提にしていたため、得意分野の回路だけでなく不得意分野の回路も含めて、チップ上に集積するすべての回路を1社が用意する必要があった。これが、チップレットを利用することで、異なるメーカー製のチップレットを組み合わせたSoP(System on a Package)を短期間かつ容易に開発できるようになる。

これによって、大規模なチップを設計する力はないが、特徴あるチップレットを開発できる半導体メーカーの存在感が大きくなる可能性がある。機器メーカーが、特定のチップレットだけを開発して、競合他社と差異化できる応用製品を作るような動きも出てくることだろう。さらに、特徴あるチップレットを集めて、ユーザー企業の要求に合わせて大規模なチップを開発・製造する「半導体ゼネコン」と呼べるような新たな業態が台頭する可能性もある。今後の半導体産業の行方を見通すうえで、チップレットに関連した動きは、見逃せない要素となることだろう。

- Writer

-

伊藤 元昭(いとう もとあき)

-

株式会社エンライト 代表

富士通の技術者として3年間の半導体開発、日経マイクロデバイスや日経エレクトロニクス、日経BP半導体リサーチなどの記者・デスク・編集長として12年間のジャーナリスト活動、日経BP社と三菱商事の合弁シンクタンクであるテクノアソシエーツのコンサルタントとして6年間のメーカー事業支援活動、日経BP社 技術情報グループの広告部門の広告プロデューサとして4年間のマーケティング支援活動を経験。

2014年に独立して株式会社エンライトを設立した。同社では、技術の価値を、狙った相手に、的確に伝えるための方法を考え、実践する技術マーケティングに特化した支援サービスを、技術系企業を中心に提供している。

- URL: http://www.enlight-inc.co.jp/