JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

- Science Report

- サイエンス リポート

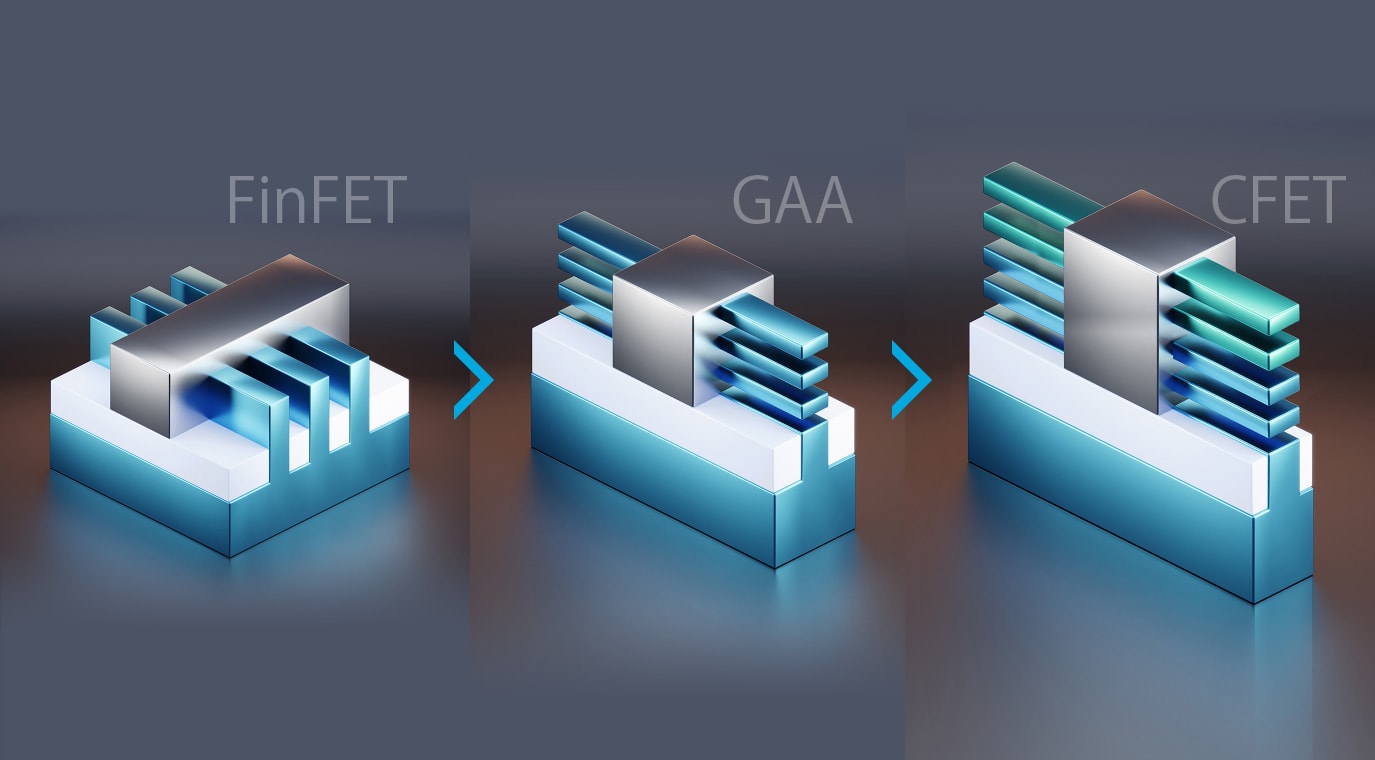

FinFETからGAAそしてCFETへ、

最先端半導体のトランジスタ技術の進化

- 文/伊藤 元昭

- 2024.07.03

半導体の進化とは、すなわちトランジスタを微細化する技術の進歩のことである。国際競争力の高い半導体ビジネスを営むためには、より微細なトランジスタを作り、利用する技術が必要だ。驚愕するような能力を持つAIも、世界中の人を密につなぐ高度なネットワーク技術も、生活や社会での移動をより便利で安全なものに変える自動運転車もトランジスタ技術の進化なくして実現できない。

- [図1]最先端の半導体チップの開発・生産は、あらゆる産業の競争力強化の源泉

- 写真は、アメリカのIBMが開発した2nm技術で製造したトランジスタの断面

- 出典:IBM

半導体チップの中でトランジスタは、微細なスイッチとして機能している。オン/オフを切り替えて“1”と“0”の信号を表現・制御することによって、2進法で動くコンピュータの機能を実現している。そして、このトランジスタをより微細に作ることで、チップの製造コストと消費電力を維持・削減しながら、高性能化と複雑・多様な機能の搭載が可能になる。

日本の半導体メーカーが20年ぶりに最先端半導体に注力

21世紀に入って以降、コンピュータの中で演算処理を実行するロジックチップの領域において、日本の半導体メーカーの最先端トランジスタを設計・製造する技術の開発力は急速に力を失ってしまった。ただし、ここに来て、最先端のロジックチップを作る技術とビジネスの自国保有が、産業競争力の強化や経済安全保障上の優位性に直結すると広く認識されるようになった。そして、国家戦略として、20年ぶりの最先端半導体技術の開発と、それを活用した先進的半導体ビジネスの立ち上げに注力するようになった。

最先端半導体技術を手中にするために取り組むべき技術開発のテーマとして、極端紫外線(EUV)露光を活用して微細な回路パターンを描く製造技術の確立が挙げられることが多い。確かに製造技術の確立は必要不可欠だ。しかし、それだけでは足りない。なぜならば、日本企業がトランジスタ開発の最前線から去った後の20年余りの間に、最先端トランジスタの技術開発のトレンドが大きく変化しているからだ。単にサイズを微細化しただけでは、求めている特性のトランジスタを実現できなくなっている。

高性能、低消費電力、高信頼で安定動作させるためには、より微細な製造技術を開発するだけではなく、トランジスタの構造も同時に刷新していく必要がある。日本での半導体産業の再興は、最先端トランジスタの開発最前線に追いつき追い越すことができるかに掛かっている。

半導体の構造は立体化し、世代を追うごとに複雑化

半導体の主流はMOSFETとCMOS

60年以上の間、コンピュータなどデジタル機器の中核に置く半導体チップには、「金属酸化膜半導体電界効果トランジスタ(MOSFET)」と呼ばれる構造のトランジスタが用いられてきた。MOSFETの動作原理は、電流の入力端子(ソース)と出力端子(ドレイン)の間に、電気的状態(電界)次第で導電体にも絶縁体にもなる性質を持つ「チャネル」領域を作り、制御端子(ゲート)に電圧を印加することで、そこを制御するというものだ。ロジックチップでは、オン/オフの挙動が電気的に真逆の2種類のトランジスタ(p型とn型)を同一チップ上に用意し、適宜組み合わせて実現したい機能の回路を構成している。こうした回路方式は、「相補型金属酸化膜半導体(CMOS)」と呼ばれており、高性能化と低消費電力化の両立が可能な技術として長年にわたって使い続けられてきた。

現在の最先端トランジスタも、MOSFETとそれを応用したCMOSを利用してチップを構成している点では変わらない。ただし、日本企業が力を失っていた約20年間の間に、MOSFETやCMOSの構造に関しては大きく様変わりしている。

2000年代末の20nm世代辺りまでは、MOSFETには、2次元構造のチャネルを採用した「プレーナー型」が利用されていた(図2)。ところが2010年代に入ると、「FinFET」と呼ぶ、3次元構造のトランジスタの採用が広がった。

微細化の進展によって登場した3次元構造のFinFETとは

FinFETとはチャネル領域を魚の背びれ(fin)のように3次元的に立たせて3方向を電極で囲み、チャネルを包み込むように制御する構造である。2011年にアメリカのIntelが世界に先駆けて22 nm世代のマイクロプロセッサーに導入すると、台湾のTSMCや韓国のSamsung Electronicsなど、ロジックチップのビジネスをリードする他社も次々と採用していった。

- [図2]FETの構造は、微細化の進展によって3次元化したFinFETへ

- 出典:Samsung Electronics

プレーナー型に比べて、FinFETの構造は複雑である。その導入には、製造工程の増加と、それに伴う歩留まり低下を招くリスクがある。それでも各社が導入に踏み切った理由は、チャネル領域の微細化が進展したことで、オン状態とオフ状態を明確に切り変えられなくなったからだ。こうした問題は、FinFET導入以前から顕在化していたが、ゲートを構成する材料を変える(酸化膜をSi酸化膜から比誘電率の高い材料に変更する)ことで、プレーナー型の延命を図っていた。ところがいよいよ延命策が尽きて、トランジスタ構造の立体化に踏み切ったのである。現在に至るまで、日本の半導体メーカーは、量産レベルでのこうしたトランジスタ構造の革新を経験していない。これから技術とノウハウを積み上げていくことになる。

FinFETは、トップメーカー各社が導入して以来、10年以上にわたって使い続けられてきた。しかし、5nm世代のチップが量産されるようになった2022年になると、FinFETでもチャネルを正常に制御し切れなくなってきた。次の新しいトランジスタ構造の投入が求められるようになってきたのである。そして、各社が2nm世代以降に導入を予定している構造が、「Gate All Around(GAA)」である(図3)。

日本企業が注力する最先端半導体技術のGAAとは

- [図3]GAA構造と最新のFinFET構造の模式図

- 図中、図中のRIBONFETとは、IntelのGAAの呼称。4枚積み重なった青色の部分がナノシートで作られる3次元積層したチャネル領域

- 出典:Intel

GAA(Gate All Around)」とは、チャネルを極めて薄いナノシートで作り、その四方を取り囲むようにゲート電極を形成することで、精密かつ確実にオン状態とオフ状態の切り替えを制御する技術である。FinFETでも、制御性を高めるチャネル領域を薄く作っていた。そして、それを2次元方向に複数並べることで、応用回路の仕様に応じた電流量を確保していた。GAAでは、チャネルを3次元的に縦積みすることで、さらなる小型化を可能にしている。GAAは、Samsungが2022年に3nm世代で量産導入したのを端緒として、TSMCも2nm世代での導入を計画している。また、日本での最先端半導体ビジネスの再興を担うラピダスが、ビジネス開始時のターゲットとしている2nm世代で利用する構造もGAAである。現在、同社はGAAの技術を保有するアメリカのIBMと共に技術開発を進め、2027年の量産開始を目指している。

微細化はCFETの世代へ

- [図4]imecが示す微細トランジスタのロードマップ

- 出典:imec

GAAを投入した後にも、微細化の世代が進んだ先で比較的頻繁にトランジスタ構造の刷新が行われる予定である。トランジスタ構造の進化の方向性に関しては、半導体技術の開発で世界をリードする研究機関であるベルギーのimecが微細化のロードマップの中で明確に示している(図4)。

まず、16Å(1Å(オングストローム)は0.1nm)世代の量産が想定される2028年頃には、GAAの発展版「フォークシート」構造の投入が予定されている。フォークシート構造とは、それまでナノシートで個別形成していたP型FETとN型FETそれぞれのチャネル領域を、一体形成した構造である。MOSFETの小型化ではなく、基本回路であるCMOSのより小型化を目指す技術だと言える。

さらに、2030年代に入って5Å世代が投入されるようになると、「相補型FET(Complementary FET:CFET)」と呼ぶNMOSとPMOSを3次元的に積層して一体化させた構造の導入が想定されている(図5)。2次元配置していたN型FETとP型FETを3次元積層し、それぞれをつないでいた配線などの付加構造を最小限に抑えることで、CMOS単位での高性能化、低消費電力化、小型化を推し進めることを狙った構造だ。そしてimecは、2036年頃の量産を想定する2Å世代には、ナノシートの厚さを原子数個分まで薄くする「原子CFET(Atomic CFET)」の導入が必要になるとみている。

- [図5]imecが開発したCFETの構造例

- 出典:imec

トランジスタと共に配線にも大きな技術革新

微細化を推し進め、進化したトランジスタの潜在能力を引き出し、高度なロジックチップを作り上げるためには、チップ上に搭載する莫大な数のトランジスタの間をつなぐ配線にも技術革新が必要になる。

トランジスタを安定動作させるためには、適切な電圧の電力を安定供給する必要がある。電圧が許容値よりも低くなってしまうと、回路の動作周波数の低減などによって、チップ動作に不具合が起きる可能性がある。また、逆に高すぎると消費電力の増大や素子破壊が起きるリスクが生じる。近年の高度なロジックチップには、さまざまな回路が搭載されているが、高速化や低消費電力化を狙って、それぞれの回路で多様な電圧要件が設定されるようになった。しかも、処理内容によって負荷が変動する。こうした電源供給にまつわる技術要求を満たすため、チップ内には複雑な電力供給ネットワークが導入されるようになった。

これまでのチップでは、トランジスタや回路で処理する対象となるデジタルデータ信号を送るための配線と、電力を供給するための配線は、共にトランジスタの上層に形成されていた。ところが、双方の配線の間で干渉が発生したり、寄生的な容量・抵抗の効果が顕在化したりすることによって、信号へのノイズ混入や電力の損失、電圧低下などの不具合が引き起こされていた。そのまま対策せずに放置したのでは、たとえトランジスタが進化したとしても、チップを進化させることが困難になりつつあった。

こうした問題を解決するため、「裏面電源供給網(Backside Power Delivery: BPD、BSP、またはBackside Power Delivery Network: BSPDN)」と呼ぶ技術の開発と量産適用が進められている(図6)。信号用の配線はトランジスタの上層に、電力供給用は下層に分別配置する技術である。BSPDNの導入によって、チップの性能、消費電力が劇的に削減され、チップ面積も小さくする効果が得られる見通しである。

- [図6]信号用配線を表面に電力供給用を裏面に分別配置するBSPDN

- 左側が従来構造、右側がBSPDNを適用したチップ構造の模式図

- 出典:Intel

Intelは20Å世代に、BSPDNを導入することを想定している。また、TSMCも2026年に予定する2nm世代の発展版技術である「N2P」への投入を計画している。これまでのロジックチップ製造では、トランジスタなど素子はウェーハの片面のみに形成されてきた。これが、BSPDNの導入によって両面に素子を形成する時代が始まる。同様の技術は、既に裏面照射型という方式のCMOSイメージセンサーで使われているが、ロジックチップ向けでは、ウェーハの表裏両面により微細なパターンを描くことが求められる。

まとめ

今後の最先端半導体チップに搭載するトランジスタの構造は、より複雑な3次元構造へと進化していく。これに伴って、半導体製造で歩留まりを高めることが以前にも増して難しくなっていくことが予想される。そして、製造技術の改善による歩留まり向上だけでなく、設計面からも歩留まり向上の後押しが求められることになりそうだ。同時に、製造技術と設計技術の間で手法と条件を擦り合わせ、総合的なアプローチで歩留まり向上を目指す、開発・量産体制も必要になってくることだろう。

トランジスタ構造の開発最前線を俯瞰すると、現在日本企業が挑んでいる半導体産業の再興が、いかに野心的な試みであるかが理解できる。日本企業がかつて見知った技術開発の景色とは全く異なる環境の中で進められており、“再興”と言う言葉よりも、“再創業”と呼んだ方が似つかわしいチャレンジであると言えよう。

- Writer

-

伊藤 元昭(いとう もとあき)

-

株式会社エンライト 代表

富士通の技術者として3年間の半導体開発、日経マイクロデバイスや日経エレクトロニクス、日経BP半導体リサーチなどの記者・デスク・編集長として12年間のジャーナリスト活動、日経BP社と三菱商事の合弁シンクタンクであるテクノアソシエーツのコンサルタントとして6年間のメーカー事業支援活動、日経BP社 技術情報グループの広告部門の広告プロデューサとして4年間のマーケティング支援活動を経験。

2014年に独立して株式会社エンライトを設立した。同社では、技術の価値を、狙った相手に、的確に伝えるための方法を考え、実践する技術マーケティングに特化した支援サービスを、技術系企業を中心に提供している。

- URL: http://www.enlight-inc.co.jp/