JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

- Science Report

- サイエンス リポート

注目が集まる「ガラス基板」の最新動向

― 半導体の進化には後工程の技術革新が不可欠に

- 文/伊藤 元昭

- 2024.09.04

半導体をさらに進化させていくために、チップをパッケージ内に実装する後工程に関わる技術の重要性が急激に高まっている。最先端半導体の製造歩留まり向上や世代・製造元・製造技術の異なる回路の集積に向けて、1チップ化すべき大規模回路をあえて個片化して後工程で集積する技術「チップレット」の活用が広がってきた。これに伴って、複数のチップレットをより高性能かつ低コストでつなぐための新たなパッケージ技術が求められている。こうしたニーズの変化に対応すべく、パッケージを構成する材料において、従来技術の枠に囚われない技術革新が起き始めている。中でも、半導体メーカーや材料・装置メーカー各社から注目が集まっている動きがある。チップやチップレットを載せるパッケージの土台となるコア基板への「ガラス基板」の採用である(図1)。

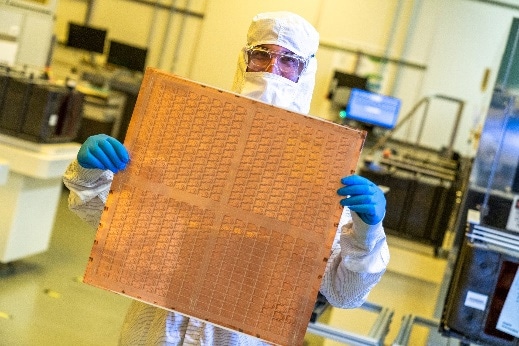

- [図1]半導体のパッケージ用コア基板としてガラス基板を適用する動きに注目が集まっている。

- 出典:Intel

現在、半導体チップのパッケージで使用されている基板材料は何か

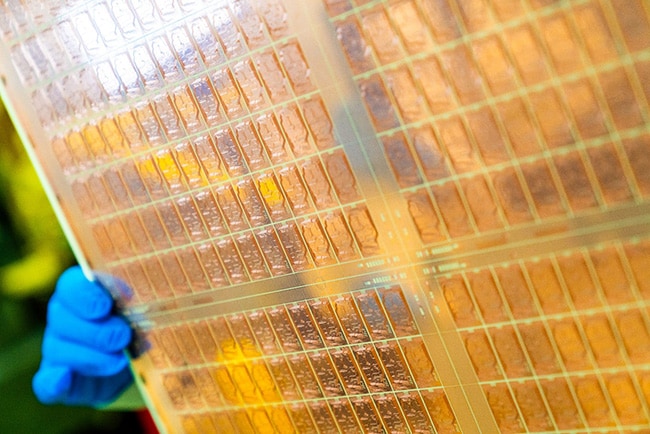

現在の半導体チップのパッケージでは、コア基板として、ガラスエポキシ基板などの樹脂ベースの基板が主に利用されている(図2)。ガラスエポキシ基板とは、ガラス繊維製の布にエポキシ樹脂を含浸させて作る基板材料のことである。

- [図2]パッケージ用のガラスエポキシ基板とガラス基板それぞれの典型的な構造

- 出典:iNEMI(国際エレクトロニクス製造者協会)でのIntelの発表資料

現在の基板では高まる社会の期待に応えられない

樹脂ベースの基板は、極めて強靭な機械的特性と優れた化学的耐久性を備え、なおかつ低コストであることから、半導体のパッケージ用コア基板の材料として利用され続けてきた。この材料は、パソコンのマザーボードなどに使われているプリント基板に使われているものと基本的には同じものだ。もちろん、半導体パッケージ向けでは、配線パターンや電極を取り出す貫通穴(ビアやスルーホール)がより微細であるといった相違点もある。それでも、材料技術や加工技術の開発トレンドに関しては、両者の間に連続性や共通性がある。長年にわたる利用実績を持つ成熟した使い勝手に優れた技術だったと言える。

しかし、樹脂ベースの基板には、有機材料である樹脂ゆえの欠点もあった。表面平坦性や剛性、熱に対する耐性の向上に限界があることだ。生成AIなど高性能コンピューティング(HPC)のアプリケーションへの適用を想定するプロセッサなどを実現するためのチップレット集積においては、プロセッサコア間やメモリー間で帯域幅を極限まで高めたデータ転送が求められる。その実現には基板上の配線やビアにさらなる微細化や高密度化、高速信号の伝送が可能な良好な電気特性の実現が不可欠なため、樹脂ベースの基板の欠点がいよいよ顕在化してきたのである。

新しい基板材料としてガラスが適性である3つの理由

ガラスという素材には、樹脂材料ベースの基板に比べて、パッケージ用コア基板として好都合な数々の特性が備わっている。

①素材の熱膨張率

まず、熱膨張率(Coefficient of Thermal Expansion: CTE)がシリコンに近く大型パッケージ上に高歩留まりでチップレットなどを実装できる。パッケージ用のコア基板の上には、シリコン製のチップやチップレット、インタポーザなどが搭載されることになる。これらが動作する際には発熱し、シリコンと基板材料のCTEの違いが原因となって大きな歪みが発生するため信頼性を損なう可能性がある。ガラス基板ならば、生じる歪みの量を半減できるため、信頼性を高めることが容易だ。さらに剛性が高い点も、歪みの低減や変形の抑制に貢献する。これらの特性があることで、より大型の基板上に、チップレットなどを高歩留まり、高信頼性で実装可能になる。ガラス基板の技術開発と実用化で業界をリードしているIntel(アメリカ)によると、最大240mm×240mmの基板まで対応できるとしている。AI関連処理向けやデータセンター用サーバー向けなどを中心に、同一パッケージ内により多くのコアやメモリーを搭載して高帯域幅でのデータ転送を実現したい、言い換えればより大型のパッケージ基板を利用したいと考える半導体メーカーは多い。

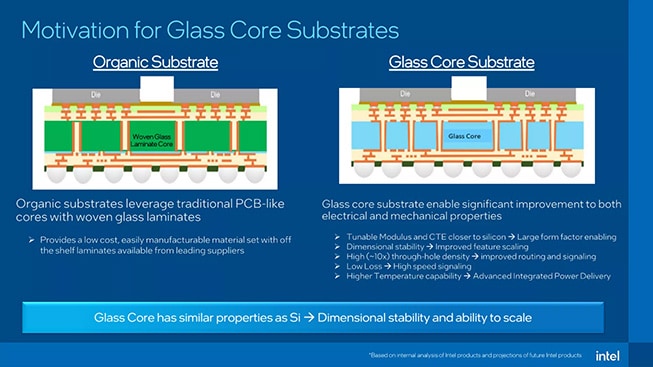

②基板の平坦性

さらに、平坦性も高い。このため、配線やビアのさらなる微細化や高密度化が実現する。Intelの見通しでは、配線幅/配線間隔(L/S)と貫通ビアの径を微細化し、配線密度を約10倍に向上できるとしている。これによって、コア基板上に形成する再配線層(Re-Distribution Layer:RDL)の層数の削減やパッケージサイズの小型化や、パッケージ内に搭載するチップレットの数を増やすことが可能になる。さらに、バンプのピッチも高密度化し、ダイの面積の縮小や配線密度の向上も可能になる。加えて、ガラスは、樹脂よりも物性面で誘電率など電気的特性に優れる。このため、より高速な信号の伝送が可能になる。同一パッケージ内に高密度配線が可能であり、なおかつ高速動作する回路をより多く搭載できるようになることから、チップレットを活用したチップのさらなる高性能化が期待できる(図3)。

|

|

③高温環境の物性

また、高温下でも物性が安定している点もガラス基板に備わっている見逃せないメリットだ。今後のチップ間配線の高速・大容量化に不可欠な光配線のシームレスな統合や、高温処理を伴うインダクタとコンデンサの埋め込などに有利に働くからだ。給電および信号配線の設計を容易化し、さらなる高速・低消費電力化に貢献できる。

より微細で高密度の配線やビアを形成するため、半導体チップ製造の前工程(シリコンウエーハ上への微細パターンを形成する工程)技術を応用して作るシリコンインタポーザを適用する方法もある。実際、多くの半導体メーカーが、シリコンインタポーザを利用して、チップレットを集積する技術を実用化している。ただし、最大300mm径の円形のシリコンウエーハ上に配線パターンなどを形成する必要がある。そこから、なるべく大きな四角形のコア基板を切り出そうとしても、切り出し枚数は少なく、ムダな部分も多く生じる。必然的に製造コストは高くなる。

Intelと同様に最先端チップ用パッケージへのガラス基板の適用を想定しているラピダスによると、同社が検討している6640mm2のコア基板は、300mmウエーハからは4個しか切り出せないという。これを600mm角のガラス基板から切り出せば、10倍の40個を切り出せるという。またガラス基板は、既に確立されている液晶パネルの製造エコシステムを通じて、大型の高品質ガラス基板の調達が可能である。大型基板に配線パターンを描く装置やハンドリング・搬送の装置などのベースも既にあり、実用化のハードルを下げている。

ガラス基板の採用で後工程の技術革新をリードするのは

①実用化に向けて海外企業での研究開発が活発に

実は、パッケージ用コア基板にガラス基板を適用するための技術開発は、意外と早い時期から行われていた。例えば、2009年には、既にジョージア工科大学(アメリカ)で研究開発が始められており、2010年代半ばには試作品も完成していた。ただし、利用できた際の効果は広く知られていたものの、長らく普及には至らなかった。ガラスへの孔開け工程で割れ(マイクロクラック)が発生する課題の解決が難航し、周辺技術も揃わなかったからだ。つまり、量産技術にするのが難しかったのである。それでも、多くの材料メーカーや装置メーカー、研究機関の地道な研究開発の成果が実り、実用化レベルで課題が解決していった。

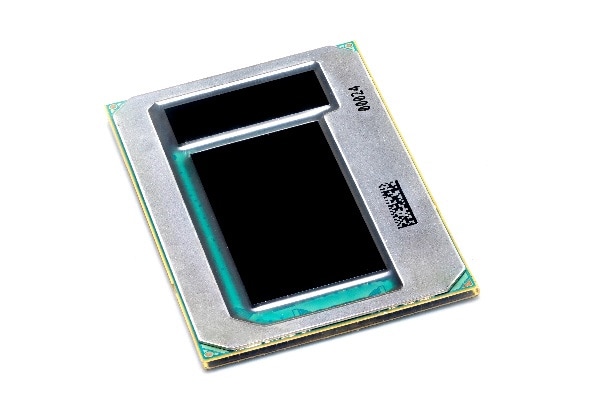

パッケージ用コア基板としてのガラス基板が脚光を浴びるキッカケを作ったのが、Intelの2020年代後半に実用化を目指すという発表だった。同社は、10億ドルを投資して、ガラス基板を用いた半導体パッケージの研究開発ラインをアリゾナ州にある同社チャンドラー工場内に構築(図4)。2030年には、1個の半導体パッケージ内に、1兆個のトランジスタを集積したチップの実現を目指すとしている。現時点で同社は、ガラス基板の技術開発と実用化の両面で業界のトップを走っていると言える。

|

|

また、Intelの動きに付随して、韓国SKグループの化学大手であるSKCの子会社、Abosolics(アメリカ)が8000万ドルを投資して、ジョージア州アトランタにパッケージ用ガラス基板の開発・製造を行う新工場を建設。アメリカ政府は、そこにCHIPS and Science法(CHIPS法)に基づいて、最大7500万ドルの補助金を支給することを決定した。アメリカ政府が、半導体パッケージ用のガラス基板の技術開発と生産体制の国内保有を、いかに重要視しているか垣間見ることができる。

②相次ぐ新技術の提案・開発で日本企業が世界を牽引する

現在の日本は、半導体の後工程向けの材料・製造装置、特に最先端チップ向けの領域で世界をリードする立場にある。その領域において、海外企業主導でガラス基板の採用という技術革新が起きている。うかうかしてはいられない。ただし、日本企業各社の動きは迅速かつ積極的である。材料や加工技術の開発・事業化を推し進めると共に、さらに進化した付加価値の高いガラス基板も開発し、提案している。

まず、ガラスメーカーは、この動きを新ビジネスのチャンスと捉えている。パッケージ用コア基板への適用を想定して、特性を最適化したガラス材料の開発・事業化が進められている。

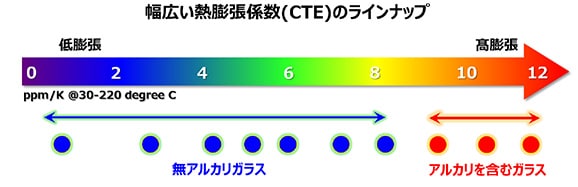

パッケージ用ガラス基板の技術仕様に関する要求は多様だ。例えば、CTEに注目すると、シリコンとCTEが完全に一致したガラスが求められているのは確かだが、それほど単純ではない。パッケージ内にはシリコン製チップレット以外に樹脂製RDLなどのCTEが異なる材料が載せられる例も多い。製造するチップごとに、構成材料の組み合わせやパターンの形状が異なるため、それらに最適なCTEを持つガラス基板が求められる。また、一般的なガラスに含まれるアルカリ成分がパッケージ内のデバイスや製造過程での装置を汚染するリスクもある。このため、応用によっては、無アルカリガラスが求められる。

ガラスの大手メーカーであるAGCは、無アルカリガラスを使った平坦・平滑な500mm角相当パネル、もしくは300mm径のウエーハ形状のパッケージ用ガラス基板を製品化している。常温から約250℃までの範囲でCTEがシリコンと完全に一致したガラスを提供すると共に、広範囲のCTEの要求に調整して提供している(図5)。さらに、アルカリを含む、より高いCTEにまで対応したガラスも用意している。同社は、そこに要求に応じたパターンでの微細ビアを形成して提供する事業も行っている。

- [図5]AGCは、熱膨張率の異なるガラスを開発し提供

- 出典:AGC

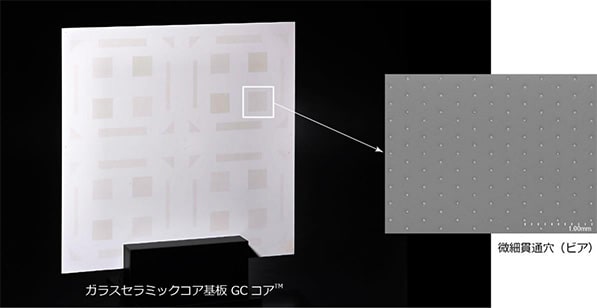

また、日本電気硝子は、既存のレーザー加工機を利用して微細ビアを加工できるガラス粉末とセラミックス粉末を混合して焼成して作る複合材の新型ガラス基板を開発した(図6)。一般に、ガラスエポキシ基板でのビア形成にはレーザー加工が適用されている。しかし、ガラス基板に適用しようとするとクラック(割れ目)が発生し、基板が破損する可能性がある。このため、レーザーによる素材改質とエッチングを組み合わせた複雑な加工工程で微細ビアを形成することになる。多様な製造装置を組み合わせた製造ラインを構築する必要があり、設備投資が増大し、加工時間も長い。日本電気硝子が開発したガラス基板は、CO2レーザー加工機を適用できる。

- [図6]日本電気硝子は、既存のレーザー加工機で加工できる新型ガラス基板を開発

- 出典:日本電気硝子

さらに、セラミックス粉末として低温焼成セラミックス(LTCC)材料を利用することで、誘電率や誘電正接が低い、信号遅延や誘電損失を低減した高速信号の伝送に向く基板を作ることが可能だ。強度も一般的なガラス基板よりも高いため、パッケージの薄型化やパッケージ生産工程でのハンドリング性向上も可能になる。こうしたコア基板の特性は、セラミックス粉末の種類の選択やガラス粉末との配合比を変えることで調整できる。

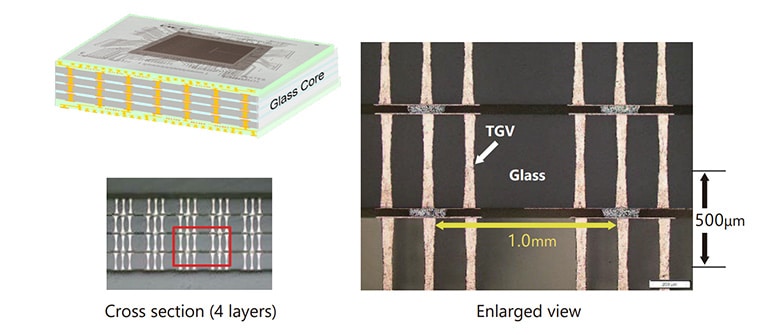

一方、FICT(旧 富士通インターコネクトテクノロジーズ)では、薄いガラス層を多層積層したコア基板「G-ALCS」を開発した(図7)。ガラス基板を支持基板としてだけ使うのではなく、ビルドアップ基板のように複雑な多層配線を形成した基板として利用できるようにした。ガラス層の間は、絶縁部分は樹脂で導電部分は導電性ペーストで積層している。樹脂で層間をつなぐことで、外部からの応力を分散させ、大きなパネルからパッケージングに用いるコア基板を切り出す際に割れてしまうことを防いでいる。

- [図7]FICTは、複雑な多層配線を形成可能な新型ガラス基板を開発

- 出典:FICT

その他にも、大日本印刷とTOPPANも、ガラス基板に貫通電極を形成したガラス基板の製造技術を開発し、事業化している。ガラス基板に関連した材料・製造装置の事業は、今後の成長が見込まれる領域だ。技術のニーズを汲み取って開発された新たな技術が続々と提案されていくことだろう。

- Writer

-

伊藤 元昭(いとう もとあき)

-

株式会社エンライト 代表

富士通の技術者として3年間の半導体開発、日経マイクロデバイスや日経エレクトロニクス、日経BP半導体リサーチなどの記者・デスク・編集長として12年間のジャーナリスト活動、日経BP社と三菱商事の合弁シンクタンクであるテクノアソシエーツのコンサルタントとして6年間のメーカー事業支援活動、日経BP社 技術情報グループの広告部門の広告プロデューサとして4年間のマーケティング支援活動を経験。

2014年に独立して株式会社エンライトを設立した。同社では、技術の価値を、狙った相手に、的確に伝えるための方法を考え、実践する技術マーケティングに特化した支援サービスを、技術系企業を中心に提供している。

- URL: http://www.enlight-inc.co.jp/