JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

- Science Report

- サイエンス リポート

AIチップの未来を切り開くウェーハスケールインテグレーション、実用化が加速

- 文/津田 建二

- 2025.04.09

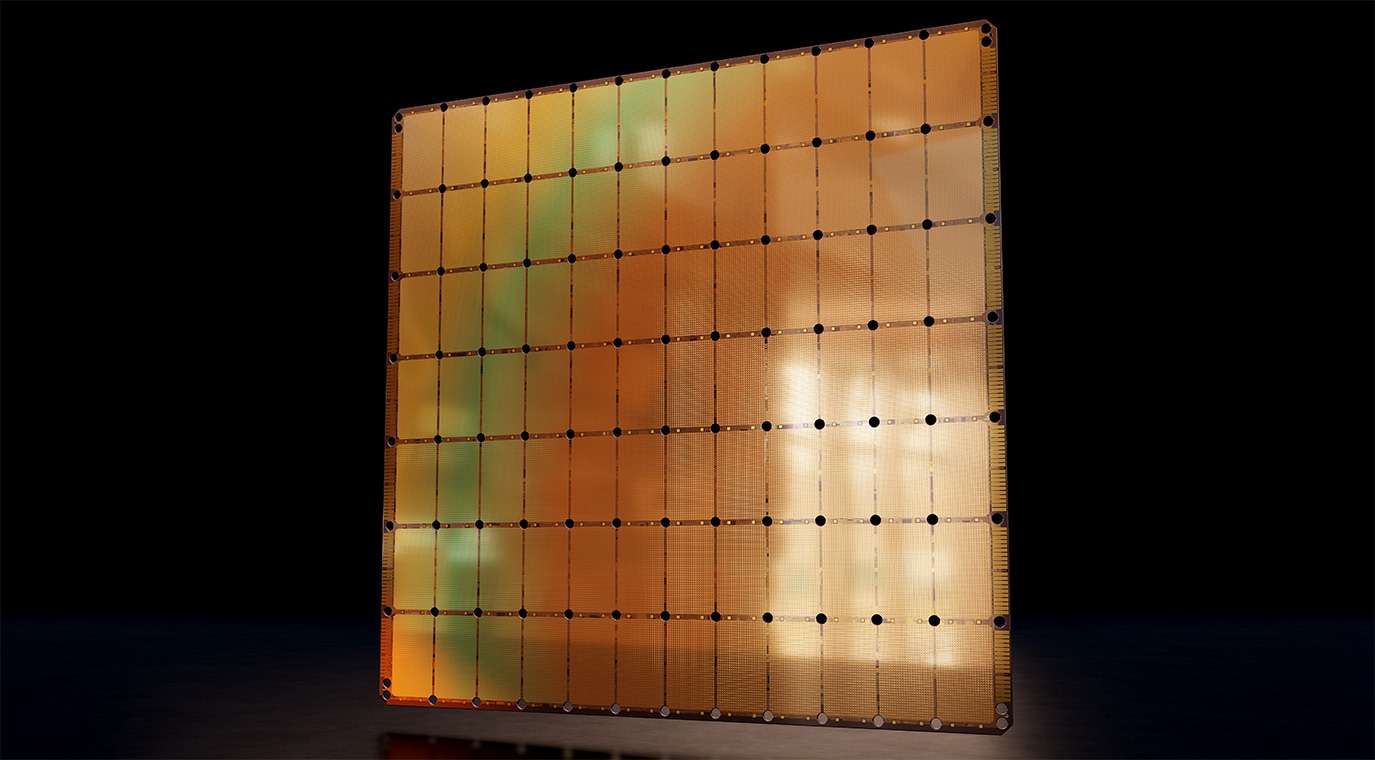

300mmウェーハ全体を一つのチップとする考え方のウェーハスケールインテグレーション(WSI)が現実的になってきた。先頭を切ったのは、スタートアップのCerebras(アメリカ)だ(図1)。ニューラルネットワークのアーキテクチャを使うAIが出てきたことと大いに関係する。AIではコンピューティングパワーを実現するための手段として極めて有効だ。Cerebrasはパートナーと組み、すでにWSI方式のチップを使ったAIコンピュータを、アメリカのデータセンター3カ所に出荷した。WSIを実現するための製造ファウンドリとして台湾のTSMCを活用しているが、TSMC側も自信を持ってWSIを提供する。さらに今年のCESでNVIDIA(アメリカ)のジェンスン・フアンCEOもWSIを示した。WSIがAIエンジンとして開花する未来が見えてきた。

ウェーハスケールインテグレーション(WSI)の実現に向けた進展

300mmウェーハから、1枚だけを四角く切り取った、ウェーハスケールインテグレーション(WSI)の巨大チップが実用的になってきた。もはやチップとは言えない大きさで、ほぼ215mm角の大きさのモノリシック半導体ICである。このようなICが実用化できるとは、誰も想像できなかったが、AI時代ではコンピュータICになりうる。

過去のWSI製造の考え方

WSIの考え方は、1980年前後にもあった。集積度を上げるために微細化が進む一方で、チップ面積を大きくするという動きがあったのだ。チップが大きければ大きいほど、たくさんのトランジスタを集積できるため、究極的にはウェーハ1枚を1個のICとしてしまえば超高集積なICができるはずだった。

ところが、空気中を漂うゴミ(空気中に浮遊する粒子なのでパーティクルとも呼ぶ)がウェーハ内に3個付着したとしよう(図2)。ゴミは、目に見えないほどの大きさで数十nm~数µm程度であり、チップサイズから見れば極めて小さい。1枚のウェーハから、32個のチップを取る場合、3個は不良品となるが、残りの29個は良品だから、歩留まりは29/32=91%となる。ところが、1枚の大規模チップの場合、ウェーハ全体が不良品となり使えず、歩留まりはゼロとなる。

チップのサイズが小さければ、1枚のウェーハから取れる数は増える。もし300個取れるサイズなら、3個が不良品で、残りの297個が良品となり99%の歩留まりとなる。その逆に1枚のウェーハから15個しか取れない大きなチップだと、不良品は3個だから、歩留まりは、12/15=80%に落ちてしまう。

整理すると、ゴミが付着した不良品ができる確率は、チップが大きくなるにつれ増えていくため、歩留まりは大きく下がってしまう。逆にチップを小さくすればするほど歩留まりは上がることになる。

WSIに関する課題

IEDM(国際電子デバイス会議)においてAMD(アメリカ)が解析した例(図3)がある。例えば、1㎠当たりのゴミが0.22個の場合、チップ面積が2.5㎠だと59%の歩留まりが得られるが、チップ面積が7.7㎠と大きくなると歩留まりは26%に低下する。もし1㎠当たりのゴミが1個の場合で、同じチップ面積の変化だと21%の歩留まりがわずか4%に落ちてしまう。

- [図3]チップ面積が大きければ大きいほど歩留まりは悪くなる

- 出典:AMD

ここで言うゴミとは、人間の体から自然に出る汗や、機械が動く摩擦で出るゴミなどのことで、クリーンルームといえども発生は避けられない。このため、チップ面積を大きくできないことは暗黙の了解だった。ゴミがウェーハ上に付着している状態でリソグラフィやエッチングをすると、その部分だけ回路パターンが細くなったり断線したりする。これでは完全な回路パターンは形成できない。チップサイズを大きくするのには限界があり、WSIは実用化できなかった。

ゴミの問題とは別に、リソグラフィ上でもレチクル(光学的なフォトマスク)のサイズを大きくすると、光学的なひずみや解像度の低下という問題が出てくるため、そのサイズに収まるチップしか製造してこなかった。

AMDは小さなチップレットでアプローチ

AMDは、チップ面積を大きくして集積度を上げると、歩留まりは確実に悪くなることを解析し、その対策として、大きなチップをいくつかに切り取り、小さなチップレットとして利用すると歩留まりが上がり、コストは下がると結論付けた。同社のGPU「MI300」などは、3次元、あるいは2.5次元のICを搭載、接続する先端パッケージに収容されている。AMDのように先端パッケージを使う技術が、この先当分は主流になるだろう。

ウェーハ歩留まりが高く、できるだけチップサイズを大きくして集積度を上げようとすると最適値が出てくるが、無理に多くのトランジスタをモノリシック(1チップのシリコン上)に集積するのではなく、いくつかに分割して、3次元にしたり、横に配置したりするなどの余裕のある実装形態が適している。これが先端パッケージの考え方だ。

新たなWSI製造の考え方

これに対し、全く逆の考え方でチップを大きくしながらも歩留まりを低下させない方法が新しいWSIである。WSIとはいえ、ゴミの問題が片付いたわけではない。やはり、チップ面積を大きくするとゴミが回路パターンを崩してしまうという問題はある。

しかし、ニューラルネットワークのモデルでコンピュータに学習させる技術では、たとえ入力配線がゴミで切れたとしても不良にはならない。図4に示す積和演算器への入力が例えば8本から7本に変わったとしても学習し直せばよいのだ。もちろん、「制御線のように絶対切れてはいけないような配線には、冗長構成でリペアする」とCerebrasの創業者兼CTO(最高技術責任者)のゲーリー・ラウターバッハ氏は語っている。だから歩留まりは100%だという。

- [図4]ニューラルネットワークのモデル

- 7~10本程度の入力の配線が1本くらい切れても学習すればよいだけなので結果に大差はない

- 作成:津田建二

CerebrasのWSI技術

Cerebrasは、2019年に初めてのWSIを開発した。この時はTSMCの16nmプロセスで巨大なチップWSE(Wafer Scale Engine)と呼ぶ21.5cm角のウェーハそのもののシリコンチップを開発、1兆2000億トランジスタを集積した参考資料1。それが2021年には2.6兆トランジスタの巨大チップWSE-2をTSMCの7nmプロセスで製造した参考資料2。そして現在はTSMCの5nmプロセスで製造された4兆トランジスタのWSE-3を2024年3月に開発参考資料3、このWSE-3の巨大チップを1枚搭載した、コンピュータCS-3をAI学習用のコンピュータとして、同社の戦略的パートナーであるG42(UAE)に64台を納入、AIデータセンターとして運用している。

現在、CerebrasのCS-3システムを導入しているAIデータセンターは、カリフォルニア州のサンタクララとストックトン、さらにテキサス州のダラスにある。今年の6月にはオクラホマ市のScale DatacenterにCS-3コンピュータを300台以上設置し、7月にはカナダのモントリオール市にある、Bit Digital(アメリカ)の一部門であるEnovumが運営する施設に設置される。Cerebrasにとって初めてのカナダへの納入となるが、性能は極めて高く、AIの推論速度は最新のGPUより10倍も速いとしている。

CerebrasのCS-3は、今年の第2四半期にはミネソタ州のミネアポリスに導入されるほか、第4四半期にはアメリカ中西部と東部にも導入が予定されている。さらにヨーロッパにも設置される予定だとしている。

技術のカギはTSMCが握る

Cerebrasは、単なる微細化だけではなく、歩留まりを向上させるための配線リペア技術や、発熱対策としての水冷導入技術などを、TSMCと共に開発してきた。しかもこのWSIをよく見ると、小さなチップのようなブロックを多数配置しており、一つのブロックはレチクルサイズに収まるような規則性のあるレイアウトである。だから、1枚のウェーハにマスクを1回で露光するのではなく、レチクルをステップ&リピート方式で露光しているように見える。つまり現実的なレチクルサイズで各ブロックを露光しているという点で、極めて現実的なWSIの解になったと言えそうだ。

このことで、TSMCはWSI技術に自信を付けてきたため、Cerebrasだけに供給するのではなく、同社以外にも要望があれば提供するという。2024年夏にTSMCが記者会見を開いた時、同社のシニアバイスプレジデント兼副共同最高業務執行責任者のケビン・ジャン氏は、これまでとは異なり、TSMCの微細化ロードマップを示さずにシリコンフォトニクスとWSIを今後の選択肢として提案した参考資料4。

TSMCは、WSI技術を先端パッケージと並ぶ、コンピューティング能力を上げるための技術として選択肢の一つに加えたのである。2024年7月、TSMCが日本でイベントを開催した時に記者会見を行い、「将来、生成AIを推進する顧客がウェーハスケール集積回路を要求する場合は、PDK(プロセス開発キット)を用意して応えていくつもりか」との質問にケビン・ジャン氏は、「Yes」と答えている参考資料4。

NVIDIAもWSIに乗り出す

NVIDIAもWSI技術に乗り出す構えを見せている。2025年のCES開催の前日、NVIDIAのジェンスン・フアンCEOが基調講演を行ったのだが、講演の最後に大きな円盤状の回路を見せ、WSI技術が次に来ることを示唆していた。

ただ、NVIDIAの考えは、Cerebrasとはやや異なる。先端パッケージ技術は、さまざまな異なるチップやチップレットなどを集積したものであり、2.5次元ではチップやチップレットをインターポーザ上に物理的に離した状態にある。これらのチップ部品を同じウェーハ上に形成したものが究極のWSI技術になるだろうとフアン氏は述べている。つまり、これから活発になってくる先端パッケージの技術は、チップとチップとの間に隙間が多いため、それらをギュッとひとまとめに密集させるという考え方だ(図5)。そして、それを実現するのがWSIだと言うのだ。

フアン氏は、大きなウェーハ状の模型を見せたものの、あまり解説をしなかった。しかし、このスライドを見ると、このWSIチップには、合計130兆トランジスタを集積していることがわかる。また、72個の「Blackwell」GPUと2592個の「Grace」CPUコア、72個の「CommectX-8」NIC(Network Interface Chip)、18個の「BlueField」DPU(Data Processing Unit)、そして576個のメモリチップ(14TBで1.2PB/sの性能)と、全GPU同士を130TB/sで接続するためのNVLinkスイッチが18個 集積されている。

実は、以前Blackwellを発表した時に、Blackwellを2つとGraceを1個搭載した基板ボードも発表しており、このボードを搭載したコンピュータを1つのラックに納め、合計72個のBlackwellを駆動させている。すなわち、まるで1台のロッカーに相当するような大きさのコンピュータラックが1枚のウェーハに収まるようなWSI技術が次世代のAIコンピュータになりうることをフアン氏は示唆した。

彼が持った1枚ウェーハのモックアップ(模型)のAI性能は、FP4(4ビットの浮動小数点演算)のAI性能が、1.4ExaFLOPSというスーパーコンピュータ並みの性能を示したのである。この「チラ見せ」こそ、将来のAIチップを示唆しているようだ。

[ 参考資料 ]

- 1. 「ディープラーニング学習にはウェーハ規模の巨大なチップが必要」、セミコンポータル、(2019/08/27)

- https://www.semiconportal.com/archive/editorial/technology/chips/190827-waferscaleic.html

- 2. 「7nmプロセスで製造したウェーハ規模の巨大なAIチップ」、同上、(2021/04/28)

- https://www.semiconportal.com/archive/editorial/technology/chips/210428-cerebras.html

- 3. 「Cerebras、4兆トランジスタの第3世代ウェーハスケールAIチップを開発」、同上、(2024/03/15)

- https://www.semiconportal.com/archive/editorial/technology/applications/240315-cerebrascs3.html

- 4. 「TSMC、Siフォトニクス、ウェーハスケール集積回路の選択肢を提案」、同上、(2024/07/02)

- https://www.semiconportal.com/archive/editorial/technology/process/240702-tsmc.html

- Writer

-

津田 建二(つだ けんじ)

-

国際技術ジャーナリスト、技術アナリスト。

現在、英文・和文のフリー技術ジャーナリスト。

30数年間、半導体産業を取材してきた経験を生かし、ブログ(newsandchips.com)や分析記事で半導体産業にさまざまな提案をしている。セミコンポータル(www.semiconportal.com)編集長を務めながら、マイナビニュースの連載「カーエレクトロニクス」のコラムニストとしても活躍。

半導体デバイスの開発等に従事後、日経マグロウヒル社(現在日経BP社)にて「日経エレクトロニクス」の記者に。その後、「日経マイクロデバイス」、英文誌「Nikkei Electronics Asia」、「Electronic Business Japan」、「Design News Japan」、「Semiconductor International日本版」を相次いで創刊。2007年6月にフリーランスの国際技術ジャーナリストとして独立。著書に「メガトレンド 半導体2014-2025」(日経BP社刊)、「知らなきゃヤバイ! 半導体、この成長産業を手放すな」、「欧州ファブレス半導体産業の真実」(共に日刊工業新聞社刊)、「グリーン半導体技術の最新動向と新ビジネス2011」(インプレス刊)などがある。

- URL: http://newsandchips.com/