- Japanese

- English

JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

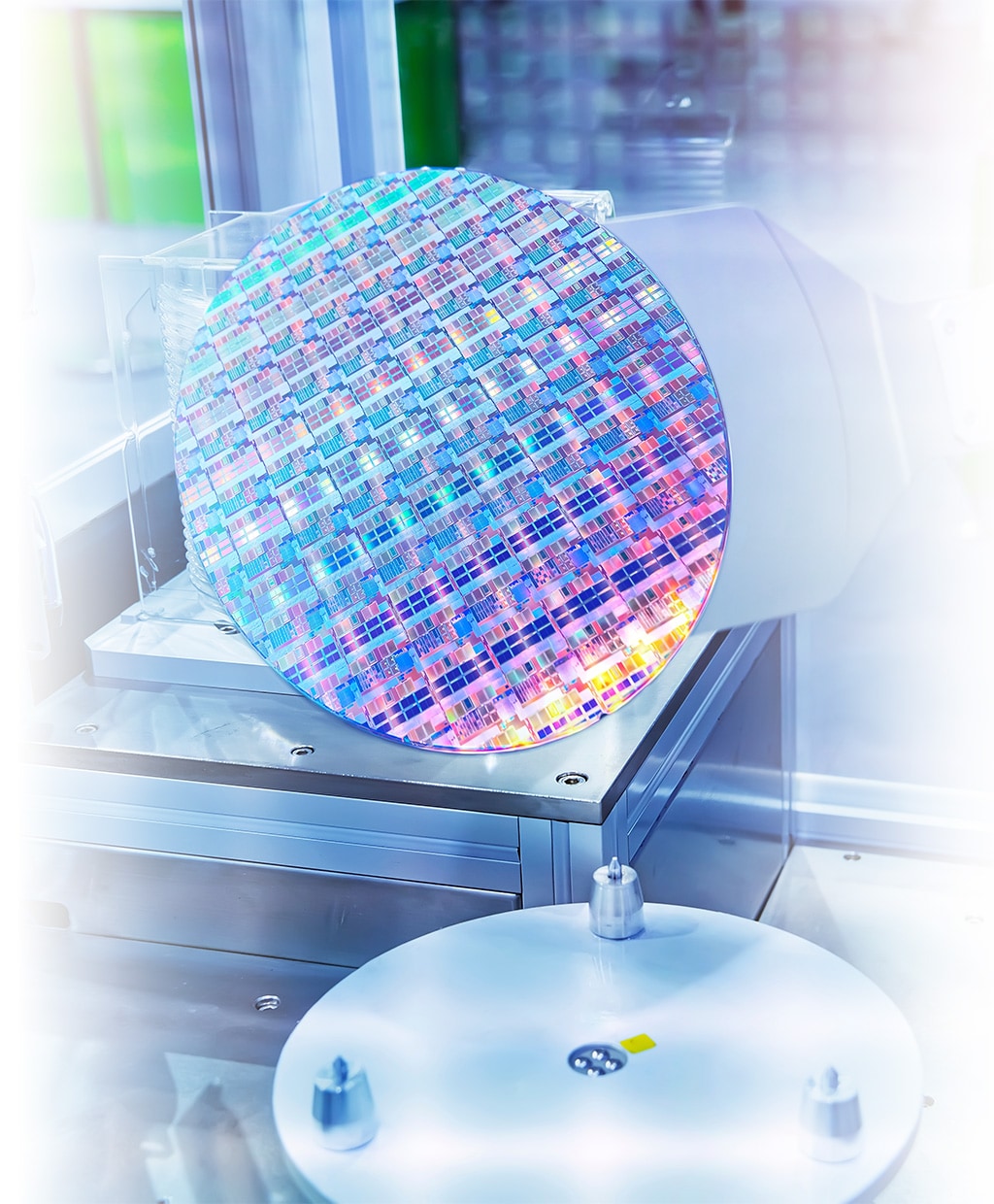

How Semiconductors Are Made

ナノの世界を追求する半導体製造工程

機械・化学・電気・電子から金属まで、

数多くの異業種技術に

よって生まれる半導体素子は、

現在イレブンナイン(99.999999999%)と

呼ばれる超高純度の世界に到達しています。

最先端のナノテクノロジーを駆使した半導体の

製造工程を、

それを支える

製造装置とともに、ご紹介します。