JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

- Science Report

- サイエンス リポート

3nm、2nm 半導体プロセスが実寸法を表していない理由

- 文/津田 建二

- 2023.11.09

「半導体は微細化が進み、今や2ナノメートル(nm)*1の開発を目指す」、「2nmの次は、18オングストローム(Å)*2」と言う声が聞こえる。一方で、「もはやムーアの法則*3は行き詰まってきた」、「ムーアの法則は、もう死んだ」、という声も聞こえる。ムーアの法則は続いているのか、それとも死んだのか、どちらが正しいのだろう。そして2nmプロセスとはどこのサイズを指すのか。これまでの取材からわかったことは、「ムーアの法則は続くが、微細化の速度は大きく落ちた」。これが正しい。では、なぜ3nmプロセスや2nmプロセスが可能なのか。ここでは、半導体プロセスノードが実寸法に対応していない理由を解説する。

10nm、7nm、3nm、2nmはチップ上の寸法のことでは無い

2019年9月、「第232回 Intelの10nmプロセスの不思議、「10nm」はどこにある?」と題した記事が掲載された参考資料1。記事には、Intelの10nmプロセスで作ったチップのどこにも10nmという寸法は存在していない。記載されていることはIntel(アメリカ)の製造プロセスと各ピッチ(配線の幅や間隔=寸法)のサイズを示す表のみである。TSMC(台湾)の7nmプロセスもプロセスのチップのどこにも7nmという寸法はない。また、Intelの10nmプロセスとTSMCの7nmプロセスは、ほぼ同じ寸法という話もある。〇nmプロセスという名称とチップ上の寸法とは完全に乖離している。

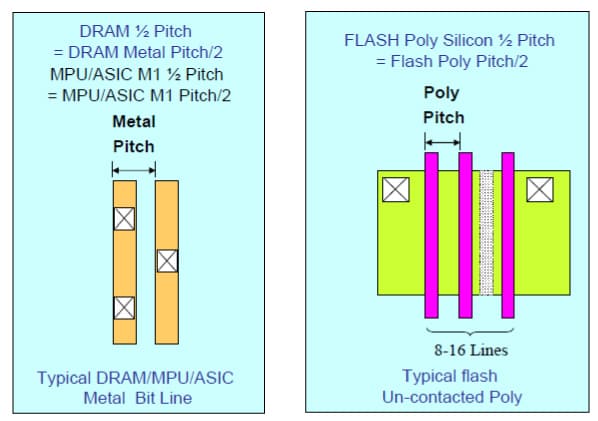

半導体プロセスノードの寸法はメタルピッチ(配線幅+間隔)で表していた

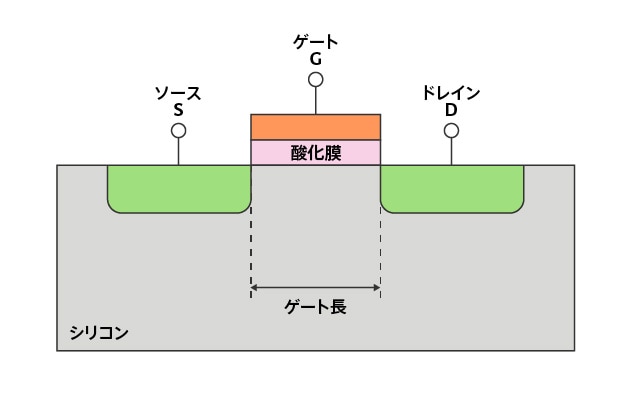

かつて、半導体プロセスノードの「〇〇nm」はMOSトランジスタのゲート長(図1)を指していた。ゲート長は、nチャンネルMOSトランジスタの場合、電子がソースからドレインへ走行する長さを表し、短くなればなるほど、短時間で移動できるため、微細化で性能が向上する。そこで、この長さを最少寸法とした。ただし、余りにも短くしすぎると、短チャンネル効果と呼ばれる現象でリーク電流が増えてしまう。その結果、消費電力も増えてトランジスタを高集積化できなくなる。そこでゲート長の微細化ではなく、配線の幅や間隔を狭くするようになり、最小寸法はメタルピッチ(配線幅+間隔、図2)で表現されるようになった。

- [図1] 2次元構造プレーナ型のMOSFET

- 最小寸法はゲート長だった。

- [図2] メタル配線の例

- ここで示すメタルピッチとは、一つの配線幅と配線間隔の合計の寸法のこと。

出典:ITRS

トランジスタ構造が2次元から3次元に変わり実寸法から乖離し始めた

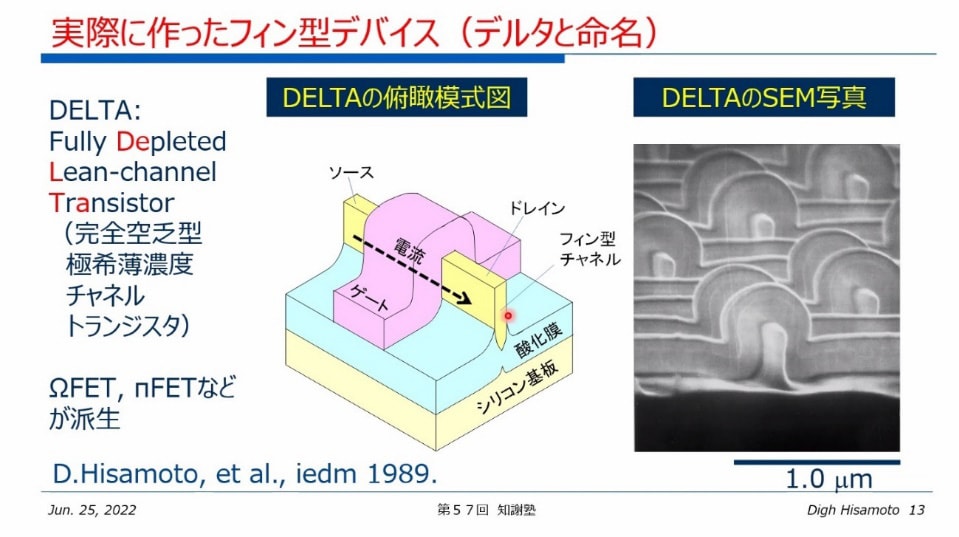

半導体の微細化が進みMOSトランジスタの構造が22nmプロセスノードになると、2次元構造のプレーナ型からFinFET(図3)と呼ばれる3次元構造に変わり始めた。最初に導入したのはIntelだ。従来のプレーナ型はチップ表面に沿って電流が流れたが、FinFETでは平面に垂直な壁に沿って電流が流れるようになる。このため、FinFETトランジスタ平面の面積は、プレーナ型よりも小さくなった。

- [図3] FinFETの構造

- 出典:日立製作所久本大氏より

実は、〇〇nmというプロセスノードと実寸法が乖離し始めたのは、FinFETの導入時期からである。FinFETの導入は3次元的に電流が流れることで面積を削減できる。FinFET構造を導入したのはIntel、TSMC、Samsung(韓国)の3社だけだったため、当時はプロセスノードと実際の寸法との乖離は、一般に明らかにされなかった。

しかし、台湾のメモリ設計会社Etron TechnologyのNicky・Lu CEOが、2022年9月に京都工芸繊維大学で開催されたKIT/Symetrix International Symposiumで「TSMCはこれまでの微細化からエリアスケーリングに変えた」と明らかにしたのだ。

〇〇nmは実寸法ではなくなった

半導体の微細化は、チップ内の配線幅/配線間隔を縮小するリニアスケーリングで微細化が進んできたが、近年はレイアウトパターンを3次元的に重ねることで面積を削減する方法(後述)であるエリアスケーリングが行われている。これによって、単位面積当たりのトランジスタ数を増やすことができる。つまり、シリコンチップ上に集積されるトランジスタ数は、2年ごとに2倍に増加するという本来のムーアの法則に沿っているのである。

〇〇nmプロセスの実際の最小寸法を示せば従来通りに見えるが、実際のところトランジスタ密度が増えて〇〇nmプロセス相当の性能があることから、〇〇nmプロセスノードという言い方をファウンドリ企業がしているのだ。

メモリも同様に実寸法を示せば従来通りに見えるため、20nm以下は、19nmとは言わずに1x nm、18〜17nmプロセスは1y nm、16〜15nmは1z nmプロセス、それ以下は同様に1αnm、1βnm、1γnm などと表現してきた。現在、実際の最少寸法は12nmまで、細かく刻みながら進化してきた。

半導体の微細化はリニアスケーリングからエリアスケーリングへ

では、エリアスケーリングは具体的にどう面積を削減しているのか。その実例を図4で紹介する。

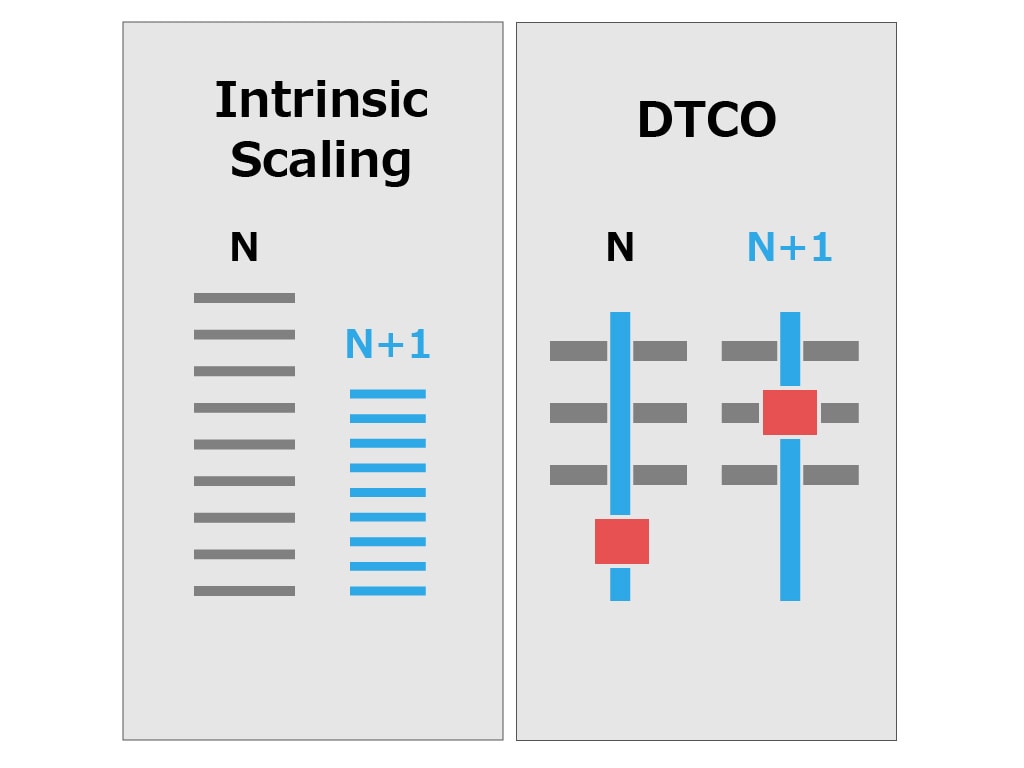

- [図4] 従来のリニアスケーリング(Intrinsic Scaling)とエリアスケーリング(DTCO)の違い

- 出典:TSMCのISSCCでの発表での図表を基に作成

https://www.youtube.com/watch?v=J5QVKCjyNG0

図4のIntrinsic Scalingとは従来のリニアスケーリングのことであり、配線幅と配線間隔を比例縮小側に沿って微細化したものである。一方、DTCOと書かれたパターンがエリアスケーリングの実例である。プロセスノードNでは、スルーホール(基板上に開けた穴/赤い四角で表現)を横方向の配線層とは別の領域に設けていたが、プロセスノードN+1では、配線層の上に重ねるようにして面積を削減した。

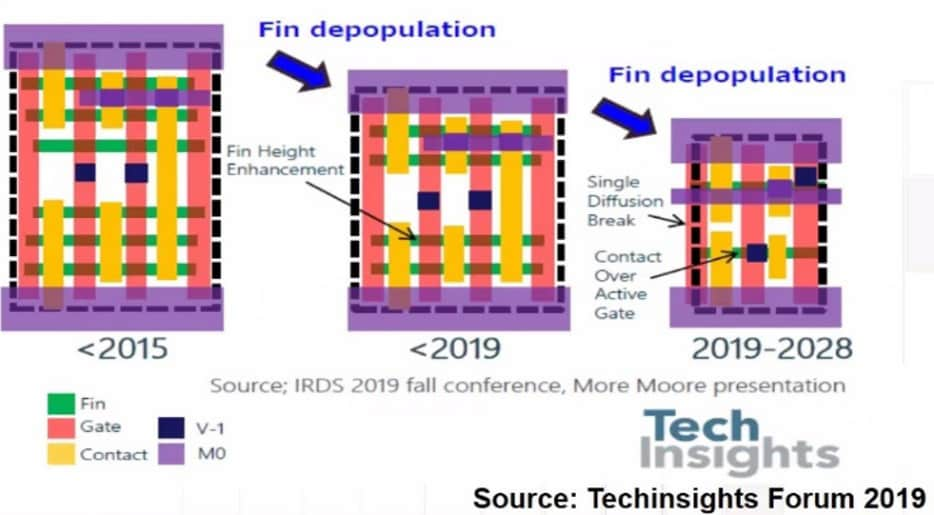

もう一つはFinFET部分の例である(図5)。

- [図5] FinFETのトランジスタ面積縮小の流れ

- 出典:TechInsights

FinFETのFinの数を3本から、2本、1本と減らすことによって、トランジスタの面積を削減している。ただし1本になれば、それ以上は削減できない。この図からAMD(アメリカ)のMark・Fuselier Technology & Product Engineering担当シニアバイスプレジデントは、SEMICON Japan 2022において「2028年ころにはエリアスケーリングは飽和する」と述べていた。

これからの微細化とは

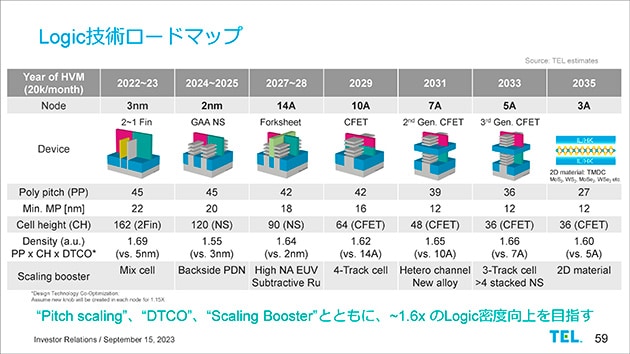

2nmより先の微細化は、どうなるのだろうか。東京エレクトロンは、2021年10月の中期計画発表の中で、2030年までのロードマップを示している(図6)。GAAの先は基本トランジスタであるCMOS回路のnチャンネルとpチャンネルのトランジスタを重ねて面積をさらに削減する方向へ向かうと予測している。

- [図6] MOSトランジスタ構造のロードマップ

- 出典:東京エレクトロンの2022年中期経営計画

リソグラフィでは、波長13.5nmのEUV装置に代わり、波長を自由に調整できる自由電子レーザーによる波長6nmの露光装置が提案されている。この新型レーザーだとEUVの約半分の寸法が期待される。

各企業の〇〇nmプロセスノードとトランジスタ密度

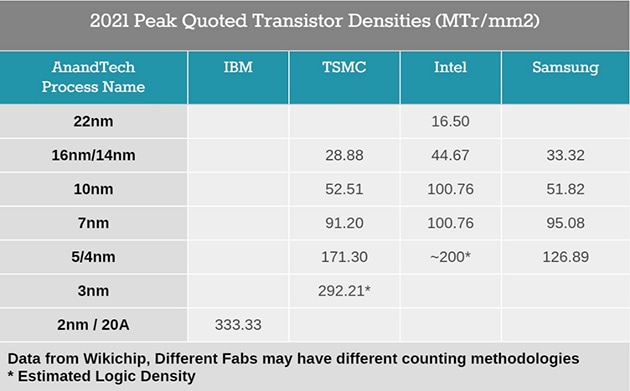

市場調査会社のAnandTech(イギリス)が、TSMCとIntel、Samsungの各社のプロセスノードと単位面積当たりのトランジスタ数を調べた(図7)。

- [図7] 先端プロセスノードと各社のトランジスタ密度

- 出典:AnandTech

これによると、Intelの10nmプロセスにおける単位面積当たりのトランジスタ数は1億個/mm²。TSMCの7nmプロセスでのトランジスタ数が9120万個/mm²だから、ほぼ等しい集積度であることがわかる。また、Intel 4プロセスでのトランジスタ数が2億個/mm²なのに対し、TSMCの5/4nmプロセスのトランジスタ数が1.71億個/mm²と、こちらもほぼ等しいことを示している。このようにしてエリアスケーリングの実態を総合的に捉えると、単位面積当たりのトランジスタ数がプロセスノードを表現していることがわかる。

2023年9月末に明らかになったが、中国のHUAWEIの最新スマートフォンのアプリケーションプロセッサチップ「Kirin 9000S」に搭載されていた、トランジスタ数は8900万個/mm²だった。これはTSMCの7nmプロセスノードのトランジスタ数に相当する(図7)。つまりHUAWEIの半導体チップは、7nmプロセスで製造されていると表現できる。

図7ではIBM(アメリカ)の単位面積当たりのトランジスタ数が、3.33億個/mm²もあることから2nmプロセスと表現しているが、これも実寸法を表しているわけではない。IBMはFinFETよりも、さらに小さな面積で製造できるGAA(Gate All Around)構造のトランジスタを設計し、500億個のGAAトランジスタを集積したテストチップを作製した。この時に1mm²当たりのトランジスタ数を見積もると3.33億個となったのだ。IBMの2nmプロセスノードのテストチップは、7nmプロセスのチップと比べ、性能が45%高く、消費電力は75%低いと見積もっている。

ラピダスがIBMから2nmプロセス技術を導入するため、半導体エンジニア数十名をIBM研究所に派遣しているが、IBMが開発したのは、あくまでも試作チップであり、ラピダスが量産チップを製造するためには、高い壁を突破する必要がある。

先端パッケージで集積度を飛躍的に向上

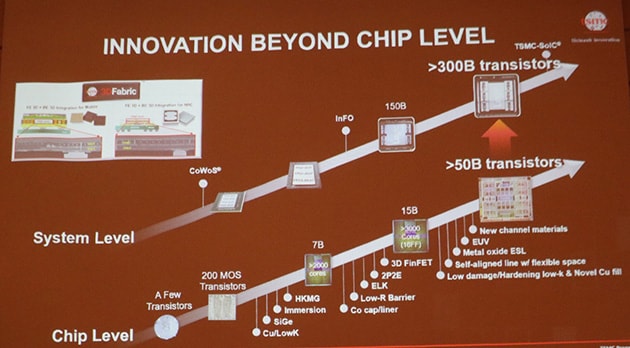

さらに先端パッケージング技術の登場で高集積化は進む。TSMCは2022年SEMICON Japanの記者説明会の席上で先端的なプロセスノードのチップやチップレット*4を使い、2.5D/3D-IC技術を活用することで、集積度が10倍に向上するという図を示した(図8)。

- [図8] 先端パッケージの採用による集積度の向上

- 出典:TSMC

プロセスによる微細化のスピードは緩やかになってはいるが、終わるわけではない。また、先端パッケージによる高集積化の歩みも始まっている。高集積化を目指す動きは、昔から全く変わっていない。性能向上と消費電力削減を同時に達成できるからだ。プロセスとパッケージの進化は、これから同時に進み、留まるところを知らない。

[ 脚注 ]

- *1

- 1nmは10億分の1mを指す。

- *2

- 1Åは、100億分の1mを指す。

- *3 ムーアの法則

- TELESCOPE magazine 半導体産業発展を支える「ムーアの法則」の過去・現在・未来 参照

- *4 チップレット

- TELESCOPE magazine 半導体業界構造を一変させる技術!?「チップレット」とは? 参照

[ 参考資料 ]

- 1. 「第232回 Intelの10nmプロセスの不思議、「10nm」はどこにある?」、@IT、(2019/9/20)

- https://atmarkit.itmedia.co.jp/ait/articles/1909/20/news016.html

- Writer

-

津田 建二(つだ けんじ)

-

国際技術ジャーナリスト、技術アナリスト。

現在、英文・和文のフリー技術ジャーナリスト。

30数年間、半導体産業を取材してきた経験を生かし、ブログ(newsandchips.com)や分析記事で半導体産業にさまざまな提案をしている。セミコンポータル(www.semiconportal.com)編集長を務めながら、マイナビニュースの連載「カーエレクトロニクス」のコラムニストとしても活躍。

半導体デバイスの開発等に従事後、日経マグロウヒル社(現在日経BP社)にて「日経エレクトロニクス」の記者に。その後、「日経マイクロデバイス」、英文誌「Nikkei Electronics Asia」、「Electronic Business Japan」、「Design News Japan」、「Semiconductor International日本版」を相次いで創刊。2007年6月にフリーランスの国際技術ジャーナリストとして独立。著書に「メガトレンド 半導体2014-2025」(日経BP社刊)、「知らなきゃヤバイ! 半導体、この成長産業を手放すな」、「欧州ファブレス半導体産業の真実」(共に日刊工業新聞社刊)、「グリーン半導体技術の最新動向と新ビジネス2011」(インプレス刊)などがある。

- URL: http://newsandchips.com/