JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

- Science Report

- サイエンス リポート

半導体サプライチェーンの設計工程から製造工程の基礎を学ぼう

- 文/津田 建二

- 2024.04.10

半導体IC(集積回路)の設計から製造までの間に、実に多くの業界や企業が携わってきたことを、「複雑な半導体サプライチェーンを解き明かそう」で紹介したが、各工程に関しては、ほとんど説明していなかった。そもそもIC回路とは何か、そしてICはどうやって作るのか、設計工程から電子回路の製造方法までの流れを、ここでは紹介し、「複雑な半導体サプライチェーンを解き明かそう」と共に、実に多くの業界や企業が関係することを改めて認識していきたい。

ICチップの微細加工サイズ

IC(集積回路)チップは、光の加減によって、まるで模様のように見えることがある。その模様は1つ1つに微細な加工がされており、加工サイズは1mmの1000分の1、つまり1µm(マイクロメートル)よりもさらに微細な100nm(ナノメートル)から10nmまでの寸法で微細加工が行われている。これほど微細な寸法のトランジスタを、どうやって設計し、製造するのか、これから解説していきたい。

市場で販売されている半導体IC上に集積されるトランジスタ数は、18~24カ月ごとに倍増するという経済原則がある。有名なムーアの法則である。この法則は、元Intel会長の故ゴードン・ムーア氏がフェアチャイルド(アメリカ)に所属していた1965年ごろに予言したもので、その頃のICはトランジスタ数が数個か十数個しかなかった。それが今では最も大きなICともなると1000億個のトランジスタが集積されるまでになった。しかも、トランジスタ1個の寸法は、配線幅を20nmとすると、50nm×50nm程度と実に小さい。

設計工程を学ぶ

設計工程はプログラミングから始まる

モノづくりは設計から始まると言われるが、半導体ICも同様に設計から始まる。ICの設計工程は、論理設計、論理合成、回路設計、レイアウト設計、配置・配線、機能動作シミュレーション、マスクデータ変換出力、という流れに乗って、フォトマスク作成に至る(図1)。

論理設計は論理式を活用しプログラムする

論理設計では、ICチップ上を大きな機能ブロック(CPUやメモリ、I/Oなど)に分け、そのブロックを、さらに小さな機能に分けて設計していく。なお、IC上の各機能ブロックのことをIP(知的財産:Intellectual Property)と呼ぶ。これらのブロックを一から設計するとなると、人海戦術では数十年もかかり現実的ではない。そこでコンピュータによる自動設計ツールを使い、さらに大きなIPブロックを外部からの購入などで入手し設計する。

まずは、機能ブロックを論理式(ANDやOR、NOTなどの論理記号やIf文など)で表現していく。これはもはやプログラミングに近い作業となり、HDL(Hardware Description Language)あるいはVerilogという名前の言語でプログラムしていくのだが、バグが発生しがちになるため、プログラム検証作業が欠かせない。

この設計作業では、まだ回路にはなっていない。RTL(Register Transfer Level)というフォーマットで機能記述プログラムを出力できたら、コンピュータによる自動的な論理合成作業で論理回路に変換する。これらの自動化作業に必要な設計ソフトウエアをEDA(Electronic Design Automation)ツールと呼んでいる。

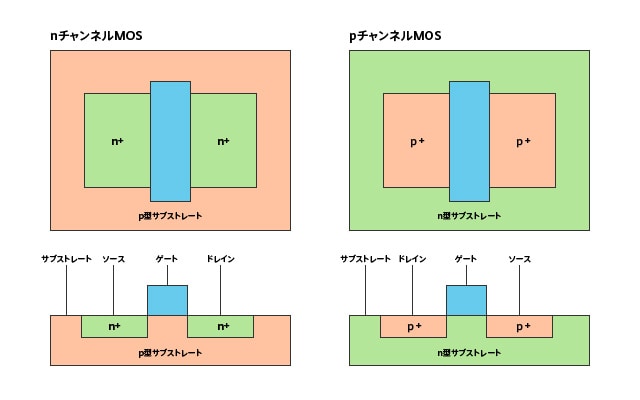

論理回路はCMOS回路を基本として設計する

論理回路はnチャンネルMOSトランジスタとpチャンネルMOSトランジスタで構成されるCMOS回路を基本トランジスタとして回路作成が行われている(図2)。1970~80年代には抵抗負荷のnチャンネルMOSトランジスタや、バイポーラトランジスタを差動回路で動かすECL(Emitter-Coupled Logic)回路などが基本論理回路として使われていたが、時代と共にCMOSに代わった。それはnMOSトランジスタにせよ、ECLにせよ、1または0を表現するときに電流が必ず流れていたからだ。

CMOS回路は基本的に、1の状態でも0の状態でも電流は流れない。欠陥などによるリーク電流が流れることはあるが、完ぺきな結晶で作られたトランジスタはリーク電流がゼロに近づくため消費電力はゼロに近い。ただ、論理状態を1から0へ、また0から1へ切り替えるときだけ電流が流れる。このため素早く切り替える、すなわち切り替え周波数を上げると電流は次第に増えていく。クロック周波数を上げれば上げるほど消費電力が増えるため、クロック周波数を上げずに性能を上げる手法として、マルチコアという概念が生まれてきた。

レイアウト配置・配線設計はコンピュータ化が進む

回路に変換できたら、今度は機能ブロックをチップ上に割り当てる、レイアウト作業となる。そして機能ブロック間とブロック内を配線で接続する。これも基本的にはコンピュータによる自動化作業となる。そのためのツールもEDA企業が提供している。

膨大なトランジスタを配線でつなぎ合わせるため、ミスは許されない。このため、最初の論理設計、論理合成、レイアウト、配置・配線など全ての工程で検証作業やシミュレーションを行い、ミスのない設計に仕上げる。それだけではない。最初の思い通りの性能や機能がきちんと得られているのかに関しても各段階でチェックする。シリコンに回路を焼き付けてしまった後にミスがあると、IC全てが不良品となり作り直さなければならないからだ。

これらの設計作業が終了したら、フォトマスクに変換する。フォトマスクのデータも自動化されており、そのフォーマットはGDS-IIという形式で出力する。マスク上にゴミやチリがないかどうかも検査する。マスクができると設計作業は終了となる。この一連の設計作業には2~3年かかることが多い。

製造工程を学ぶ

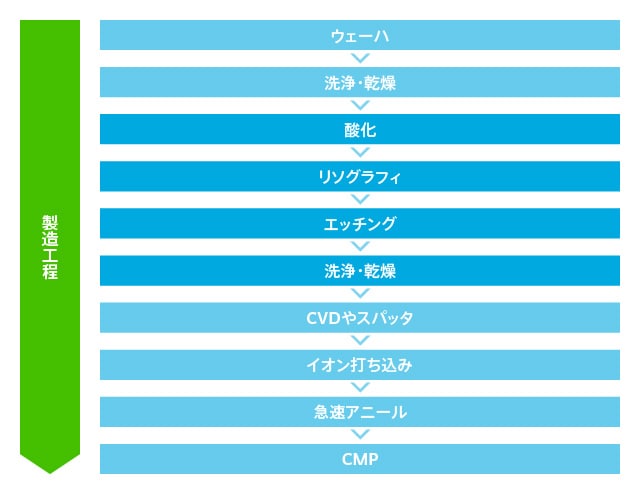

- [図3] 製造工程

- リソグラフィから洗浄・乾燥の工程をマスクごとに繰り返す。図4では酸化→CVDによる多結晶シリコン形成→リソグラフィ→エッチング→洗浄・乾燥の工程を表している

製造工程では、設計工程で作製したフォトマスクを利用して露光・現像・エッチングなどのパターン加工を繰り返し行う。例えば、図4のようにMOSトランジスタのゲートに使われてきた多結晶シリコンを加工する例を紹介しよう。

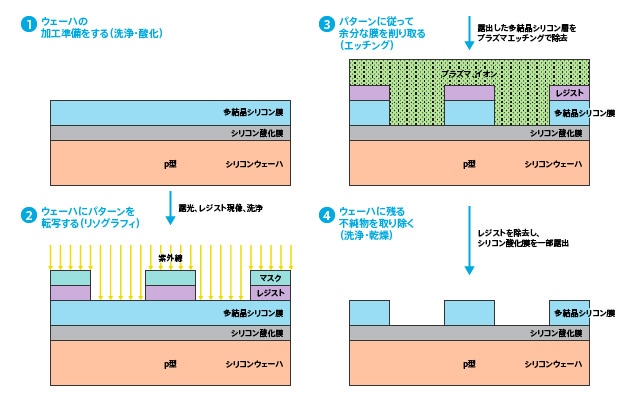

ウェーハの加工準備をする(洗浄・酸化)

まず、1000℃程度の高温でシリコン表面を酸化し、P型シリコン基板上にシリコン酸化膜を形成する。その後、ウェーハを洗浄し、表面上のパーティクル(ゴミや塵芥など)を取り除いた後に、CVD(化学的気相成長)装置の中に入れて多結晶シリコン膜を形成する。この状態が図4①のウェーハ断面となる。

ウェーハにパターンを転写する(リソグラフィ)

次にリソグラフィ工程で多結晶膜を加工する訳だが、まず粘着性のある液体のフォトレジストをウェーハ全体に塗布する。このままだとレジストでウェーハ表面がドロドロの状態なので、100℃程度のプリベーク(熱処理)を数十分間行い、有機溶剤を飛ばして焼き固める。その後、設計図となるフォトマスクをウェーハ上に設置し光を当てたくない領域を隠す。ポジ型レジストは光が当たると感光し現像液で溶けてしまうため、図4②の状態となる。ネガ型レジストはこの逆で、光が当たらない領域のレジストが現像液で溶けてしまう。

パターンに従って余分な膜を削り取る(エッチング)

フォトマスクを外すと、多結晶シリコン膜上にレジストが残っている領域と、除去された領域ができる。ここで、露出している多結晶シリコン膜をプラズマエッチングで取り除くために、F(フッ素)系のガスを使う。ガスに含まれるプラズマやイオンに反応し、多結晶シリコン膜が除去されるが、レジストに覆われた部分の多結晶シリコン膜は残り、図4③の状態になる。

ウェーハに残る不純物を取り除く(洗浄・乾燥)

さらに、多結晶シリコン膜上のレジストをプラズマなどで除去、洗浄すると、図4④の状態になる。すなわち多結晶シリコン膜がある所と、ない所ができる。これが回路パターンになる。また、図4は多結晶シリコンだけの加工のプロセスである。この後に、例えば、p型表面の一部をn型に変えるため、As(ヒ素)やB(ボロン)をイオン注入などで打ち込んだり、ゲート多結晶シリコンと接続する金属配線層を形成したりする場合も、図4と同様のリソグラフィ・エッチング工程を使う。

ICを製造するのには、以上のような製造工程を繰り返し通り、ほぼ3カ月程度かかる。このため、工程一つでの作業時間の短縮が求められる。加えて、エッチングやレジスト除去などの工程でプラズマ炉を使うのだが、最初のロットと数十回目のロットでは炉の状態が変化するため歩留まりが悪くなる。このため、製造装置内を常にモニターしながら、炉内が同一状態になるように調整する。

設計工程と製造工程に企業が分かれた背景

これらの大変な設計作業工程をしている間、製造ラインは動かせないままだから、1社で設計と製造工場を持つことは経済的に見合わない。しかし、1社の製造ラインが専業で複数社のICを受け持つならラインは常に稼働できる。これがファウンドリビジネスである。また、1社でも製品の種類が豊富にあれば製造ラインは埋まるだろうが、1社でたくさんの製品を設計することも経済的に難しい。だから設計を専門に行うファブレスと製造を専門に行うファウンドリに分離してきたのである。

ただし、メモリのように設計が単純なら、設計期間は短く、しかも大量生産の製品だから、1社で設計と製造ラインを持っていても経済的に見合う。このためメモリメーカーはIDM(設計と製造を受け持つ垂直統合型の半導体企業)が成り立つのである。

設計工程では作業時間を短くすることが求められている。さらに、論理設計においてミスやバグを見つけ除去することが設計の精度を上げ設計期間の短縮に役立つ。できる限りコンピュータによる自動設計化を進めることがミスを除くことにつながる。ICの製造現場では、決められた状態を常に保ちながらICの電気的・論理的特性を随時チェックし歩留まりを上げるようにエンジニアたちが活動している。ICの集積度はこれからもますます増加し複雑になっていく。このため、設計と製造の自動化は、これからも進んでいくだろう。

- Writer

-

津田 建二(つだ けんじ)

-

国際技術ジャーナリスト、技術アナリスト。

現在、英文・和文のフリー技術ジャーナリスト。

30数年間、半導体産業を取材してきた経験を生かし、ブログ(newsandchips.com)や分析記事で半導体産業にさまざまな提案をしている。セミコンポータル(www.semiconportal.com)編集長を務めながら、マイナビニュースの連載「カーエレクトロニクス」のコラムニストとしても活躍。

半導体デバイスの開発等に従事後、日経マグロウヒル社(現在日経BP社)にて「日経エレクトロニクス」の記者に。その後、「日経マイクロデバイス」、英文誌「Nikkei Electronics Asia」、「Electronic Business Japan」、「Design News Japan」、「Semiconductor International日本版」を相次いで創刊。2007年6月にフリーランスの国際技術ジャーナリストとして独立。著書に「メガトレンド 半導体2014-2025」(日経BP社刊)、「知らなきゃヤバイ! 半導体、この成長産業を手放すな」、「欧州ファブレス半導体産業の真実」(共に日刊工業新聞社刊)、「グリーン半導体技術の最新動向と新ビジネス2011」(インプレス刊)などがある。

- URL: http://newsandchips.com/