JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

- Science Report

- サイエンス リポート

今年は14nm半導体決戦の年〜

ところで14nmとはどこの長さ?

- 文/服部 毅

- 2015.02.27

半導体技術はムーアの法則に従って、ひたすら集積度を上げる方向でこれまで進化を遂げてきた。集積度を上げるために10µm(ミクロン=1/100mm)時代から始まった集積回路(IC)はひたすら微細化を実現し、今最先端の製品技術は14nm(ナノメーター)の技術までやってきている。しかしトランジスタ構造は3次元になり、どの寸法が14nmなのか不明になってきた。本連載では、第1回目は最小寸法の定義について、第2回は3次元化への道、第3回はさらなる大口径化(450mm)への展望についてお届けする。

最近、新聞やウェブサイトを見ていると、「米国インテル、14nmからファウンドリービジネスに本格参入」、「韓国サムスン、14nmプロセス技術を米国企業に供与」、「台湾TSMC 16nmデバイスのリスク生産開始」、というような見出しをしばしば目にするようになってきた。見出しにある14nm、あるいは16nmというのは一体何のことだろうか。ICチップの微細化を特徴付ける最小線幅あるいは最小加工寸法のことだと思いこんでいる人が多いのではなかろうか。以前はそれが正解だったが、微細化競争が激化するにつれてだんだん事情が複雑化してきており、もはや最小線幅や最小加工寸法を意味しない。それではいったい何を意味するのか?

半導体ICは、回路線幅を細く、回路を小さくして、たくさんのトランジスタを集積することによって、消費電力を下げ、高速動作(性能)を向上させてきた。このため、トランジスタやIC(集積回路)が生まれてから、ずっと回路の微細化が進められてきた。トランジスタ数の増加を表すムーアの法則に従って、トランジスタ数は増加の一途をたどってきた。新聞でも時々書かれているこのムーアの法則とは、1チップに集積されるトランジスタの数は18〜24カ月ごとに倍増する、という技術の進化を表したもの。トランジスタをたくさん詰め込むためには回路の線幅を細く、回路を小さくしてきた。集積回路が誕生した頃は回路の最小線幅は10µm(ミクロン=1/100mm)だった。これが7µm、5µm、3µm、2µm、1.3µm、1µm、0.7µm、0.5µm、0.3µm、0.2µm、0.13µm、と細くなってきたころから、nmという単位を使うようになってきた。その後は、90nm、65nm、45nm、28nm、20nm、16/14nmと、ほぼ0.7倍のペースで微細化し、現在は16/14nmノードまでやってきた。ノードとは、これまで最小線幅を実現するプロセスの総称として使われていたが、14nmノードではもはや実際の最小寸法は14nmよりも小さくなっている。「ノード」にはもはや意味がなくなりつつあるのだ。

世界規模の協業で定めた半導体微細化の指標

米国半導体工業会(Semiconductor Industry Association: SIA) は、日本の電子情報技術産業協会(JEITA)半導体部会はじめ各国の半導体業界団体と世界規模で協業して、15年先までの半導体微細化のトレンドを予測している。そして、毎年、「国際半導体技術ロード マップ(International Technology Roadmap for Semiconductors, ITRS) を更新し続けている。その最新版(2014年4月に公表された2013年版)の総括表の抜粋を表1に示す。

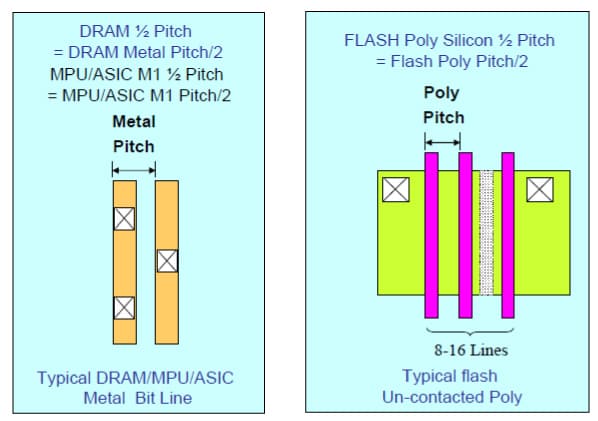

ITRSは、集積回路の集積度を決める要素は、伝統的に最小の配線ピッチであることを考慮し、最小配線ピッチの1/2(ハーフピッチ)を微細化の指標としている(図1)。ピッチとは、周期的に並んだ、一つの配線幅と配線間隔を合計したもの。DRAM(Dynamic Random Access Memory;コンピュータのメモリとして使われている)の場合は、配線の最下層に相当する金属配線層(Metalの1層目という意味でM1層と略称される)の配線ピッチの1/2を"技術ノード"(技術の節目と言う意味)と称して微細化の度合いを表す指標としている(図1左)。MPU(Micro Processing Unit;マイクロプロセッサ)やASIC(Application Specific Integrated Circuit)などのロジック(論理)半導体デバイスでも、同様にM1層のハーフピッチで微細化の度合いを示すと定めている。フラッシュメモリの場合は、メモリセル内のワード線(碁盤の目のようなマトリクス状に並んだメモリの一つを選択するために使う配線)のハーフピッチを微細化の指標としている(図1右)。図示されているように、DRAMやMPU/ASICの配線にはコンタクトホール(基板や上層の配線と導通させるための孔)が配置されているが、フラッシュメモリのワード線はコンタクトホールを含まないので、そのハーフピッチは他のデバイスの値より小さい。このため、フラッシュメモリの配線の微細(細さ)はDRAMよりも先行している。

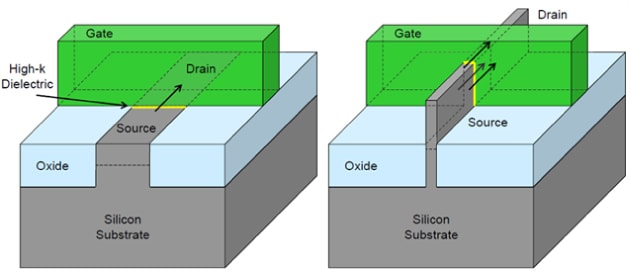

メモリ業界では、伝統的にこの定義を採用しているが、IntelのMPUに代表されるロジックデバイス業界は、ITRSの方針には従わず、MOSトランジスタのゲート長(図2左に示すプレーナ型MOSFETの最上部のゲートの長さ(図中の緑色の長方形の幅))を技術ノードとして扱い、ビジネスを進めてきた。最近では、フォトマスク(電子部品の回路パターンを転写する際の原版のガラス乾板)上のゲート長よりもはるかに細くでききるプロセス技術が導入されたため、このゲート長が最小加工寸法として躍り出た。MPUの演算性能を表す指標としては、配線ピッチよりもむしろこちらの方が新しい世代の技術を表している上に、配線のハーフピッチよりはるかに小さい値となるので、微細化を誇示したいロジックICメーカーやファウンドリーでは、微細化を象徴する数値としてゲート長を採用した方がビジネスに有利とみている。このため、これを商用ノードと呼ぶ人もいる。

|

物理長と無関係に独り歩きし始めた微細化の指標

しかし、近年、ゲート長の微細化に陰りが見えてきた。 ゲート長を短くすると短チャネル効果と呼ばれる現象が顕在化してくるからだ。この現象はデバイスの電気特性を劣化させるもので、わずかな寸法のバラつきがあっても誤動作してしまう。その結果、ゲート長を縮小する毎年のペースが落ちてしまったため、微細化の指標に使うのは都合が悪くなってきた。そこで、最近は、2〜3年ごとに新材料や新構造を導入し、ある程度加工寸法が縮小されるたびに、前の世代の技術ノードの0.7 倍の値を便宜的に新技術ノードとして採用するようになった。

DRAMがテクノロジーをけん引する製品だった1980年〜90年代には、長年に渡り、世代ごとに最小線幅を0.7 倍(面積は、0.7×0.7 ≒ 0.5倍、つまり面積半減)に縮小させてきたのが、その名残であるが、最近のロジックデバイスでは、もはや物理的な長さとは無関係に、数字だけ独り歩きしてしまっている。表1の最上段に「ロジック業界で使われているノード名を示すラベル」と記されているのはそのためである。もはや物理的な意味がないので表1では、"16/14"のように無名数(単位のない数値)で表示されているが、これに習うケースは少なく、これまでの延長線上で"nm"という長さの単位をつけて使っているのが実情である。しかし、表1からもわかるように、そのような長さの個所は存在しない。最先端の量産立ち上げ中のデバイスの技術ノードをTSMCは16nmと呼び、インテルやサムスンは14nmと呼んでいるが、実際の微細化の程度やデバイス性能は、今後発売される製品を調べなければわからない。

|

新しい3次元トランジスタ構造の登場

トランジスタのバラつきを増やす短チャネル効果を抑制するため、新しい構造が登場した。これは、チャネルを多方向からゲートで囲うことで、わずかなキャリア(電子や正孔)も漏れなくする制御技術である。構造を3次元化することでトランジスタのサイズも小さくできる。インテルは、世界に先駆けて22nm世代から MOSトランジスタのチャネル(電流の流れ道)の3方向をゲートで囲う3次元立体構造(インテル自身はTri-gate(図2右)と呼んでいるが、一般には魚のひれ(Fin)になぞらえてFinFETと呼ばれる)に切り替えた。ライバル企業は、数年遅れで16/14nmから採用する。表1から明らかなように、ここで最小加工寸法は7nm台のFinFETのフィン幅(図2右で緑色のゲートと直角に交わる灰色の細いフィンの幅で)であり、16/14nmではない点が注目される。

|

今年は16/14nm半導体ファウンドリー決戦の年

ITRS2013(表1)にも示されているように2013年中に14/16nm ロジックデバイスの量産が始まる予定だった。しかし、Intelの14nm MPUの製造歩留まり(良品の取れる割合)が立ち上げ時点から長期に渡り低迷しており、2014年後半になってようやく、わずかの量のタブレットPC用14nm MPUが米国オレゴン州にある試作ラインから出荷された。パソコン用 14nm MPU量産は2015年にずれ込んでしまっている。2年ごとのロジック技術ノードの更新が14nmでは3年以上かかってしまっている。インテルは2013年秋に、「14nmからは本格的にファウンドリーサービス(集積回路の製造だけを請け負うサービス)を開始する」と発表しているが、歩留まりトラブルが完全には解決しないため、ファウンドリーとしての製造開始は、パソコン用MPU量産が軌道に乗る2015 年後半以降にずれこむのではないかと見られている。

|

最先端の半導体は激烈な競争を展開

いま、最先端の半導体ビジネスは14nm技術でしのぎを削っている。ここに登場するのは、インテル、サムスン、TSMCなど半導体製造でトップ争いを演じている企業ばかりだ。彼らが展開している激烈な競争の一部を紹介しよう。

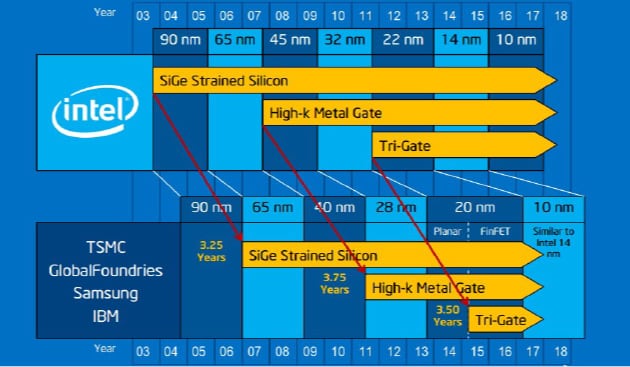

インテルは、ファウンドリービジネス参入にあたり、長年にわたって他のライバルに先駆けて新技術を導入し続けてきており、常に3年以上先行していると主張している(図4)。ライバルメーカーを名指しで露骨に比較するほど、モバイルビジネス不振のインテルの厳しい現状が垣間見える。

一方、韓国サムスン は、20nmをスキップして14nm Fin FETプロセスの開発を急いだおかげで、2014年前半に完成させ、インテルのファウンドリーサービスに先駆けて昨秋からの生産開始を発表していた。複数の顧客から大量注文を取り付けたか、あるいはその感触を得ていると言われている。同社s2ファブ(米国テキサス州オースチンにある工場の名前)ではすでにアップル社向けA9プロセッサ(今年秋にアップルから発売が予想されるiPhoneやiPadの次機種に使用される予定)の試作を開始していると噂されている。さらに、サムスンは米国グローバルファウンドリーズ(GF)に14nmプロセスを供与し、両社一体となって、世界に向けて14nmデバイスの受託生産を開始すると、昨年4月に発表している(図4)。GFは現在生産準備中である。

|

台湾TSMCは、新興ファウンドリーであるインテルと対抗するため、20nmプロセス開発と並行して16nmプロセス開発を行うという離れ業をやってのけ、2014年にはアップルはじめ世界有数の大口顧客の20nmデバイス注文を独占すると同時に昨年秋から16nmリスク生産(試験的な生産)を始めている。

本格的なファウンドリービジネスへの参入宣言をしたインテルと、TSMC、サムスン(+技術供与先のグローバルファウンドリーズ)との三つ巴の激しい戦いがいよいよ始まろうとしている。14nmの次は、10nmの戦いとなるが、微細化の困難性はさらに増しており、ITRSロードマップ通りにはいかないことは確実だ。この意味で、ITRSは未来予測としてとらえると裏切られることが多くなっており、関係者の努力目標ととらえるのが適当だろう。

これまで半導体集積回路は、シリコンのほんの表面だけを使って形成してきた。今後は、シリコンを立体的に重ねて3次元構造を作って集積度を高めようとする技術もある。次回の連載では、これらの技術が向かう方向について考察していく。それによって、今後どこまで微細化が進むのか? 合わせて、読み解いていくことにしよう。

[第2回へ続く]- Writer

-

服部 毅(はっとり たけし)

-

ソニー(株)に30年余り勤務し、中央研究所で半導体基礎研究、半導体事業本部でデバイス・プロセス開発から量産ラインの歩留まり向上まで広範な業務を担当。この間、本社経営/研究企画業務、米国スタンフォード大学大学院留学、同集積回路研究所客員研究員等も経験。2007年に技術・経営コンサルタント、国際技術ジャーナリストとして独立し現在に至る。工学博士。The Electrochemical Society (ECS)フェロー・理事。韓国漢陽大学工学部客員教授。主な著書に「シリコンウェーハ表面のクリーン化技術(リアライズ社)」、同英語版(Springer社)、「半導体MEMSのための超臨界流体(コロナ社)」「メガトレンド半導体2014ー2023(日経BP社)」がある(共に共著)。