JavaScriptが無効になっています。

このWebサイトの全ての機能を利用するためにはJavaScriptを有効にする必要があります。

- Science Report

- サイエンス リポート

シリコンウェーハは直径20mmから出発、450mmをめざす道程

- 文/服部 毅

- 2015.04.30

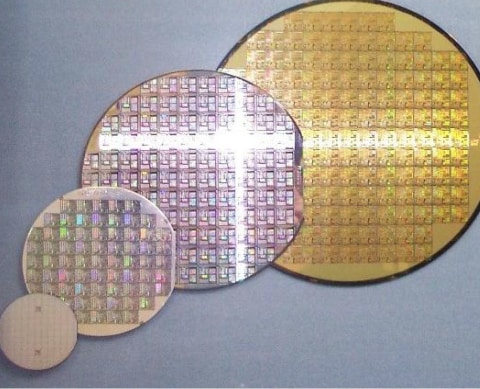

前回は、ムーアの法則に従って、半導体デバイスの微細化により高集積化を図り、トランジスタ当たりのコストを過去50年以上にわたり低減してきたと述べた。ただし、コストダウンは、このような微細化・高集積化だけではなく、製造歩留まり(良品率)の改善や、製造効率化によるスル―プット(単位時間当たりの製品処理数)の向上など、製造現場の努力に加え、半導体デバイスの土台となるシリコンウェーハ(半導体基板)の大口径化によるところが大きい(図1)。

ウェーハの面積が拡大すれば、1枚のウェーハからとれる半導体チップ(ダイとも呼ばれる)の数を増やせるので、チップ当たりの製造コストを下げられるからである。今回は、半導体コストダウンの有力手段であるウェーハ大口径化を採りあげて過去の歴史を振り返る。そして、次世代450mm時代はいつやって来るのか探ってみよう。

|

半導体の歴史はウェーハ大口径化の歴史

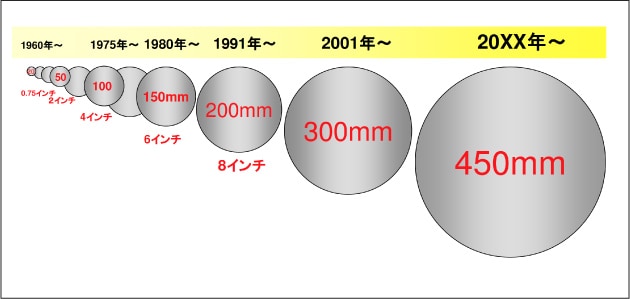

半導体の歴史は微細化の歴史であると共にシリコンウェーハ大口径化の歴史でもあった(図2)。1960年過ぎに、まず直径0.75インチ(約20mm)前後のシリコン単結晶ウェーハが入手できるようになった。ゴードン・ムーア氏がいわゆる「ムーアの法則」(前回記事参照)を提唱した1965年ごろ、それまでは主にディスクリート(単一機能)トランジスタ中心に細々と使われていた直径1.25インチ(約30mm)の小さなウェーハにかわって黎明期の集積回路用に1.5インチ(約40mm)ウェーハ需要が急増した。

|

その後、2インチ(約50mm)、3インチ(約75mm)を経て、1975年頃に4インチウェーハ(約100mm) が登場し、世界的に広く普及する。その後は、図2に示すように、5インチ(125cm)、6インチ(150mm)、8インチ(200mm)をへて、今世紀に入り、300mmの時代を迎えている。

現在、先端の半導体製造ラインでは、ロジック(論理)集積回路もメモリーもアナログも300mmウェーハを使用しているが、1980~90年代に建設された製造ラインでは6~8インチウェーハが使われており、ごく一部の古いラインでは、未だに4インチを使っているところもある。

ところで、ウェーハ口径の呼び方だが、トランジスタ発明とともに半導体結晶の成長も米国が起源であるため、その単結晶ウェーハの直径表示は(いまや世界中で米国でしか通用しない)ヤードポンド法に基づき、伝統的にインチ表示されてきた。しかし、8インチのころから米国でもウェーハ口径表示にメートル法を適用する機運がでてきて、米国人は意識して200mmと言う一方で、日本人が今までの延長で8インチを好んで使うという不思議な光景がしばしば見られた。300mmからはメートル法表記が世界的に定着している。

シリコンウェーハ製造は日本のお家芸

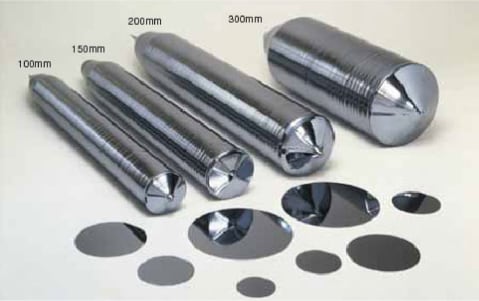

シリコンウェーハはどのように製造されるのだろうか。まずは、高純度の多結晶珪素(シリコン)を砕いて、お椀のような形状をした石英製のるつぼに入れ、加熱して溶解させる。次にワイヤでつるした小さな種結晶の棒をシリコン融液の液面につけ、回転させながらゆっくりと引き上げると、種結晶と同じ原子配列をした単結晶シリコン・インゴット(塊の意味)が作られる(図3上部)。円柱状のハムの塊を包丁で切ってスライス(薄膜状のハム)にするのと同じ要領で、シリコン・インゴットも薄切りにして円板状のウェーハにしてから、何度も研磨やエッチングや洗浄を繰り返し、表面を鏡面のようにピカピカにし出来上がる(図3下)。

|

単結晶シリコン・インゴットを結晶欠陥なしに引き上げるのは、温度制御やインゴット引き上げスピード制御など難しく微妙な技術を要し、半世紀かけて試行錯誤を続け、インゴット直径を0.75インチ(20mm)から300mm(12インチ相当)まで徐々に拡大してきた。この間、直径は16倍、面積では250倍に拡大したことになる。ちなみに2014年の世界シリコンウェーハ出荷実績は、前年比11.4%増の93億7千万平方インチ(604万5千平方メートル)で、過去最高を達成した。金額ベースでは、76億ドル規模である。

ところで、シリコンウェーハの世界トップ・サプライヤ―は信越半導体(信越化学の100%子会社)であり、海外ではSEH(Shin-Etsu Handoutaiの頭字語で、エスイーエイチと発音)として知られている。2位はSUMCO(サムコと発音)で、一般の方にはなじみが薄いが、れっきとした日本企業である。 三菱マテリアルズシリコンと住友金属工業シリコン事業部門が2002年に合併して住友三菱シリコン(英語名はSumitomo Mitsubishi Silicon)となり、2005年にSUMCOに改名した。後に同業のコマツ電子金属を買収し子会社化したので、いわば信越半導体のライバル3社の連合軍だ。信越とSUMCOだけで世界シリコンウェーハ市場で6割以上のシェアを握っている。無欠陥の結晶品質が要求されるシリコンウェーハ製造は、いわば日本のお家芸である。

コスト3割減を狙う450mm大口径化

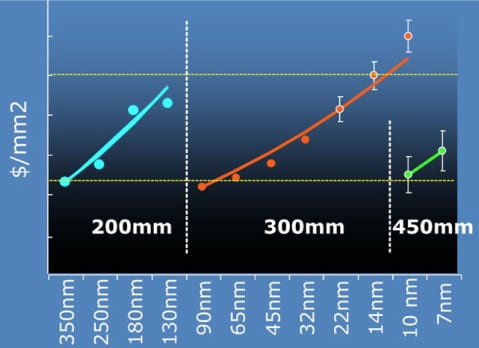

半導体デバイスを微細化するたびに、解像度の高いリソグラフィ技術を始め、新たな技術や材料を導入する必要があり、デバイスの製造コストはますます高騰する傾向にある。このようなコスト上昇を、ウェーハを大口径化することにより吸収しようという試みが、過去50年以上に渡り行われてきた(図4)。

|

この経験則に乗って、現在ウェーハ口径を現在最先端の300mmから450mmへと1.5倍大きくして、(面積は1.5 x 1.5=2.25倍に大きくして)、微細化によるコストアップを大口径化で吸収しようとしている。

米国の半導体製造技術開発コンソーシアムであるセマテックの試算によると、450mmウェーハの価格は、当初は300mmウェーハよりも5.5倍高くなったとしても、450mm製造装置購入費や水道光熱費や消耗材料費やメンテナンス費用を、300mmの場合の3割増しに抑えられれば、結果として、450mmウェーハを用いた場合のチップ当たりの製造コストは300mmから3割減となる(表1)。このような製造コスト削減をめざして、450mm大口径化を推進する世界的な動きが出てきている。

|

米国で先進5社が450mm化推進組織結成

米インテルは、微細化によるチップコスト上昇を回避するために、過去のシリコン(Si)ウェーハ大口径化の経験則に従い、450mm化を一刻も早く実現しなければならないことを早くから主張していたが、2008年 5月に韓国サムスン電子、台湾TSMCに働きかけ、450mm製造技術を3社で共同開発すると発表した。しかし、半導体製造装置メーカーはどこも未だに300mm装置の開発費を回収できていない段階にあったため、協力が得られず、「2012年に450mm試作開始」という初期の計画は頓挫してしまった。

450mm化がにわかに現実味を帯びるようになったのは, 米国ニューヨーク州のクオモ知事が「米台韓の先端半導体メーカー5社(インテル、TSMC、サムスン、グローバルファウンドリーズ、IBM)が、次世代コンピュータチップ開発と450mm大口径化推進の2大プロジェクトを州都Albanyで開始する」という声明を2011年9月26日に突如発表して以来である。

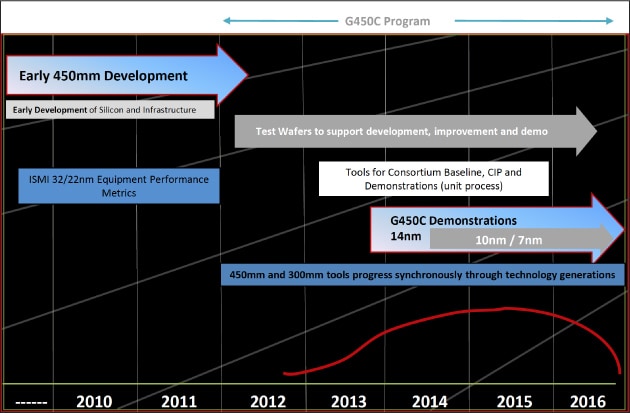

この5社が参画し、ニューヨーク州政府/ニューヨーク州立大学ナノスケール理工学カレッジ(CNSE)が主導する450mm コンソーシアム (Global 450mm Consortium :G450C )が翌年活動を開始し、その目標は、「会員企業が2015-2016年に450mmパイロットラインを構築できるように、450mm装置を評価し、14nm世代のプロセス技術の検証を進め、製造可能な環境を整備する」というものであった。後に、「2016年末までに10/7nm装置評価・プロセス検証」と目標を変更して今日に至っている(図5)。

|

G450Cは、初期の450mm装置評価結果は極めて良好であり、未設置の露光装置(後述)を除き、300mmから450mmへ移行するに際しての大きな技術的障壁はないと判断している。

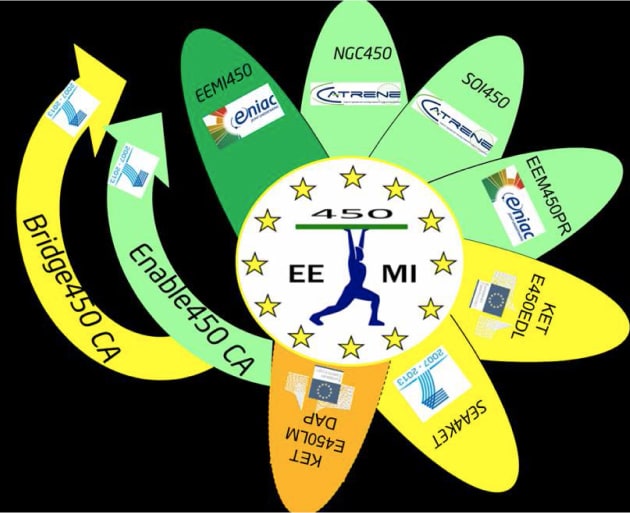

欧州では装置業界が450mm化推進活動

欧州では、同地域の半導体装置・材料メーカーが450mm大口径化開発活動を推進し、European 450mm Equipment and Materials Initiative (EEMI450)という母体が2009年に結成された。EC (欧州委員会)からの資金援助で2010-12年に同名の450mm装置材料開発プロジェクトが実施され、プロジェクト終了後もこの推進母体は「欧州における450mmプラットフォーム」として存続。会員数は10カ国58社に増加している。そして、その周辺には公的支援を受けた様々な450mm化推進プロジェクトが次々と誕生し、同時進行している(図6)。これらの活動をネットワーク化し外部に広報するプロジェクトENABLE450、およびアジアにおける450mm装置の潜在需要を掘り起こすと共に450mmファブを欧州に誘致するプロジェクトBridge450が全体を推進している。

|

ベルギーにある独立系の先端半導体研究機関imecは、地元フランダース地方政府の資金で450mm研究開発用クリーンルームを建設中である。

これらとは別に、イスラエルでは、政府支援でMetro450という450mm計測の産官学プロジェクトが発足させている。Metro450は、450mm装置評価に関して、米G450Cおよび欧EEMIとグローバルな協業体制を敷いている。

450mm量産実現のカギにぎる露光装置

450mm量産にとって一番のボトルネックはリソグラフィだが、本命のオランダ(蘭)ASMLの量産用EUV(波長13.5nmの極端紫外)露光装置開発は、光源出力を向上させ、スループットを従来の露光装置並みに上げるメドが立っていない。一方、ニコンはASMLに対抗して、従来技術を用いた450mm ArF液浸露光装置(試作機)を2015年4月に出荷、次いで量産機の2017年(以降で顧客の希望時期に)出荷を表明している。同社は、少なくとも今後数年間は世界の450mm化計画のペースメーカー役を務めるだろう。ただし、この方式の露光は解像度が悪いため、マルチパターニングという複雑な工程を経ないと超微細加工ができず製造コストが上がる。これに対してEUV露光は、解像度が高いため一回露光で済むので、EUV露光の実用化を待ちたいという市場の向きもある。

450mm化は一体いつはじまるのか?

世界の最先端微細化を主導するインテルの当初(2012年)の予定では、2015-2016年に450mm試作開始、2018年に量産開始となる予定であった。しかし、本連載第1回で述べたように、同社は14nm MPU用の300mm製造ラインの歩留まりトラブルが長期間解決しないという、想定外の事態に見舞われた。まずは300mmラインを埋めるメドが立たなければ450mmへの移行はできない。さらには、インテルが主力のPC向けMPUビジネスの長期凋落を見越して本格的にファウンドリ参入を宣言し、14nmファウンドリ競争が激化したことにより, 一時的にせよ、450mm化どころではない状況になっている。しかも、上述のように450mm EUV露光のめどもたっていない。

インテルは、当初の計画がすでに何度か先延ばしされている(実際には棚上げされている)ことは認めつつも、公式的には「断固たる決意で2010年代後半に450mm量産を開始する(クルザニッチ社長, 2013年 10月)」」方針に大きな変更はない(つまり遅くとも2019年末までには450mm量産を開始したい)としている。しかし、インテル・TSMC・サムスン間のファウンドリ競争が10nmで更に激化し、しかも歩留まり向上のための技術開発に時間がかかるようだと、450mm化はさらに先延ばしされる可能性がある。

加えて450㎜製造工場の建設には300㎜工場以上の膨大な設備投資が必要とされることから、この投資に耐えられるのは世界的に見てほんの数社という現実もある。半導体業界全体として成長を続けるために、市場的・経済的な観点からも考える必要があろう。

- Writer

-

服部 毅(はっとり たけし)

-

ソニー(株)に30年余り勤務し、中央研究所で半導体基礎研究、半導体事業本部でデバイス・プロセス開発から量産ラインの歩留まり向上まで広範な業務を担当。この間、本社経営/研究企画業務、米国スタンフォード大学大学院留学、同集積回路研究所客員研究員等も経験。2007年に技術・経営コンサルタント、国際技術ジャーナリストとして独立し現在に至る。工学博士。The Electrochemical Society (ECS)フェロー・理事。韓国漢陽大学工学部客員教授。主な著書に「シリコンウェーハ表面のクリーン化技術(リアライズ社)」、同英語版(Springer社)、「半導体MEMSのための超臨界流体(コロナ社)」「メガトレンド半導体2014ー2023(日経BP社)」がある(共に共著)。