TELが切り拓く先端パッケージング時代のR&D最前線

Technology

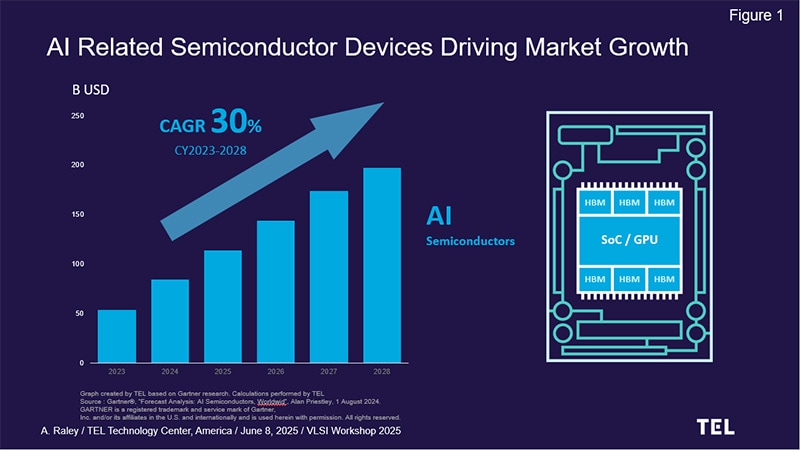

近年、人工知能(AI)や高性能コンピューティング(HPC)の急速な進展により、これらの技術を支える半導体市場は大きく成長している。AI半導体の売上高は、2028年までに年平均成長率(CAGR)30%で成長すると予測されており、その需要拡大は目覚ましい。

AI半導体は、「3Dインテグレーション(3DI)」技術を用いて製造されており、複数の半導体や機能を一つのユニットにパッケージ化することで、半導体のさらなる性能向上を可能にしている。この技術は現在、半導体の能力強化を実現する重要な手段として大きな注目を集めている。

東京エレクトロン(以下:TEL)は、豊富な装置ポートフォリオを生かし、デジタルツイン技術を用いて「3Dインテグレーション(3DI)」装置の研究開発を加速している。

本記事では、半導体研究における最高峰の国際学会Symposium on VLSI Technology & Circuits 2025(以下:VLSIシンポジウム)でのTELエンジニア Angélique Raleyが開催したセッションの発表をもとに、3DIにおけるさらなる技術イノベーションに向けたTELの取り組みを紹介する。

略歴

-

Angélique Raley

Angélique Raleyは現在、TEL Technology Center, Americaにて、インテグレーションおよび3DIのシニアテクノロジーディレクターを務める。彼女は、先端ロジック、パッケージング、フォトニクス分野におけるTELの装置ポートフォリオソリューションの統合に関する研究開発を統括。 フランスのPolytech’ Grenoble(グルノーブル工科大学)で材料科学工学の修士号を取得後、サムスン社のインテグレーション部門でキャリアをスタートし、2010年にTELに入社。Angélique は半導体研究コミュニティのメンバーであり、複数の国際会議の運営委員会にも参加。彼女はこれまでに、多数の国際会議で論文発表や招待講演をおこない、半導体技術の着実な進展に貢献する50件以上の特許を取得。

半導体進化の鍵を握る、3Dインテグレーション(3DI) 技術とはなにか

3Dインテグレーション(3D Integration、以下3DI)技術は、複数の半導体デバイスや異なる材料を3次元構造で組み合わせ、一つのパッケージにまとめることで、性能や機能を向上させる技術だ。

これまで半導体は主に、「微細化(スケーリング)」によって性能を高めてきた。これは、回路をより小さな面積に細かく書き込む(小さな2次元領域内に書き込む)方法だ。その「微細化」に加えて今、新しい半導体開発のアプローチとして登場したのが3DI技術であり、2次元のスケーリングを補完する新たな開発手法として注目を集めている。

AIや高性能コンピューティング(HPC)、自動運転、5G/6Gといったアプリケーションに向けた、高速かつ低遅延のデータ処理ニーズが高まる中、半導体技術の向上が求められている。高密度で高機能な半導体パッケージを実現する3DI技術は、半導体の性能と機能向上に欠かせない技術として大きな注目を集めている。

VLSIシンポジウム2025において、Angélique Raleyは、3DI技術の進化における課題の共有に焦点を当てたセッションの主催者を務め、デジタルツインの活用によるポストボンドオーバーレイ制御の可能性に関する概要を紹介した。

セッションメンバーであるキオクシア社のTagami Masayoshi氏は、3D NANDメモリのスケーリングの進化を加速する上で3DI技術の重要性を強調した。一方、スタンフォード大学の博士課程学生 Dennis Rich氏は、超高密度3D異種統合のコンセプト「N3XT」を発表した。NVIDIAのLiron Gantz博士は、ボトルネックを回避するためのインターコネクト帯域幅の重要性が高まっていることをセッションで説明した。彼は、複数の半導体を高密度で接続し、性能と効率を向上させるチップレット設計におけるパッケージング技術であるNVIDIA社のCo-Packaged Optics(CPO)技術について述べ、さらなるスケーリングと効率化を可能にする先進的な2.5Dおよび3Dインテグレーションアーキテクチャの探求の必要性を強調した。

前工程での活用にも広がりを見せる3DI技術

半導体の製造は、「前工程 (フロントエンド)」と「後工程 (バックエンド)」に分かれる。前工程は、ウェーハと呼ばれる基板上に半導体デバイスを形成する工程であり、後工程は、ウェーハに形成された半導体デバイスを個々の半導体チップにダイシングし、それらを組み立てて完成させる工程だ。

それぞれの工程で求められる技術は異なるが、近年、伝統的に後工程で使用されてきた貼り合わせ技術が前工程に応用されるなど、技術の融合が進んでいる。どちらの工程でも、高清浄度と高精度化をもつ製造装置が求められている。

このような技術的融合が起こっている理由は、半導体のさらなる性能、機能向上を実現するための、高密度な半導体パッケージングへのニーズの高まりに起因している。具体的には、従来CMOS イメージセンサーの製造で用いられてきた「ウェーハボンディング技術*」が、3D NANDやロジックデバイスの前工程にも適用され始めている。さらに、DRAM向けのボンディング技術の開発も加速している。今後、次世代の主要な半導体デバイスすべてに、このボンディング技術が導入されることが見込まれており、不可欠な技術になっている。半導体デバイスのロードマップに応じた、加速的な開発を推進するために異なるボンディング技術が必要とされている。

*ウェーハボンディング技術 : 複数のウェーハ(半導体基板)を貼り合わせる技術。3D集積において異なる層を接合する際に使われる。

TELの強み:前工程と後工程、両方の技術を融合した製品

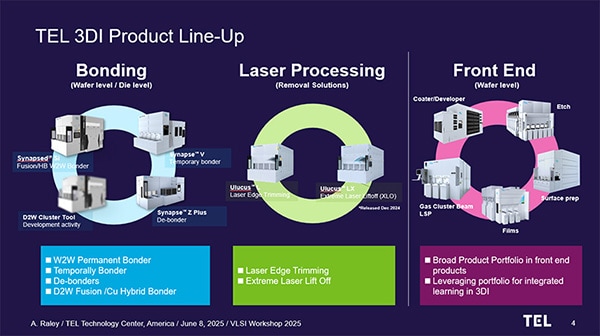

ボンディング技術を搭載する製造装置の開発には、多くの技術の統合が求められる。TELは前工程と後工程の両方をカバーする幅広い製品ラインアップを有し、前工程で求められる高精度かつ高清浄度の技術力を備え 、高い世界シェアを誇る。世界的に見ても、このような幅広い装置ポートフォリオを一つの企業で提供できるメーカーは少数だ。この強みを生かし、TELは前工程と後工程の両工程の技術を融合した装置を開発している。プラズマ活性化や、洗浄プロセスによるボンディング界面の最適化、CMPの制御、そして熱伝導率など適切な膜特性の確保は、最終的なボンディングと半導体デバイス性能において極めて重要だ。エッチング、成膜、洗浄、表面処理など従来の前工程装置の知見を生かした半導体プロセス技術およびハードウェアの開発が加速している。

◆3DI製造装置ラインアップ

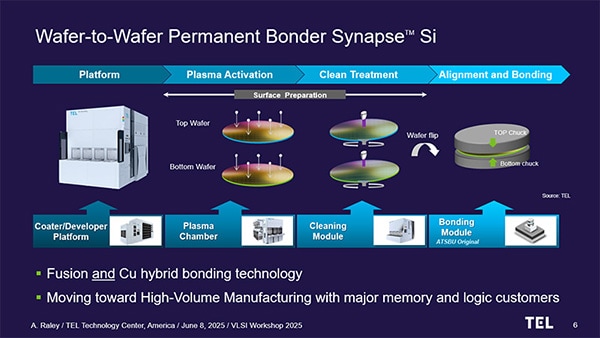

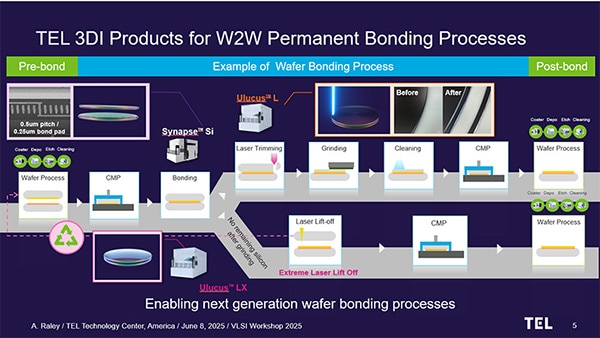

Wafer Bonding Equipment “Synapse™ Si”

プラズマ制御技術*、洗浄技術、高精度アライメント(位置合わせ)技術といった前工程の技術を応用し、3DI特有の厳しい要求に対応するよう設計された装置。Cu hybrid(カッパーハイブリッド)もしくはFusion(フュージョン)として知られる「ボンディング」プロセス技術を統合した装置。

*プラズマ制御技術:半導体表面の加工や洗浄のために、ガスや高エネルギーガス(プラズマ)を精密に操作する技術。

Temporary Bonder/Debonder “Synapse™ V and Synapse™ Z Plus”

TELが保有する前工程のスピンコーティング技術*、洗浄・乾燥技術や、独自開発の位置制御技術が一つの装置に統合された装置。薄いシリコンデバイス層上のスルーシリコンビア(TSV)の加工を可能にする。この技術は、AI半導体向けの需要が急拡大している高帯域幅メモリ(HBM)の製造において使用されている。

*スピンコーティング技術:回転するウェーハの表面に液体を広げて均一な薄膜コーティングを形成する技術。

Edge Trimming System “Ulucus™ L”

特殊なレーザー加工を活用し、ウェーハのエッジを正確にトリミングして、高いプロセスクリーン度と信頼性を兼ね備える装置。多数の量産実績がある前工程のリソグラフィ装置*「LITHIUS Pro™ Z」のプラットフォームを基に開発された装置。

*リソグラフィ装置 :ウェーハ上に半導体回路のパターンを形成する装置。

Extreme Laser Lift-Off (XLO) System: Ulucus™ LX

特殊なレーザーを用いてシリコンキャリアウェーハを剥離する技術を搭載する装置。シリコンキャリアウェーハは何度も再利用が可能であり、シリコンキャリアウェーハの使用を節約し、使用水量を削減することで、ウェーハ加工の環境負荷を大幅に低減する装置。

デジタルツインの活用による開発加速

高性能な装置を開発するためには、検証済みのシミュレーションモデルを通じて重要な要素を理解し特定することが不可欠だ。TELは、物理理論を取り入れた機械学習によるモデル化(Physics AI)*手法を用いたデジタルツイン*技術を活用している。これにより、限られた学習データでも必要な予測精度を保ち、開発スピードを加速させている。モデルや最適化は実際の製品での性能に結びついてこそ意味がある。異なる補正モデルをテストによって比較し、簡略化したショートループ試験を実施し、隠れた要因を特定することが重要だ。

*Physics AI(物理理論を取り入れた機械学習):物理理論を組み込んだ人工知能技術で、限られたデータでも高精度な予測モデルをつくる技術。

*デジタルツイン : 実際の装置やシステムの動作をコンピュータ上で正確に再現し、設計や最適化に活用する技術。

3DI装置の開発における克服すべき課題は以下の通り。

- ウェーハ反りの管理 反ったウェーハを正確にボンディング するには、反りの度合いや形状に応じた補正技術が求められる。

- ポストボンド歪みの最小化 ボンディングプロセスは、機械的および化学的現象が複合的に作用し、接合されたウェーハに局所的な歪みを生じさせる可能性がある。ハードウェア設計とプロセス条件の最適化により、ボンディングプロセスを制御し、ポストボンド歪みを抑制することが求められる。

- 高精度アライメントとオーバーレイ測定 赤外線カメラを用いてウェーハの位置ずれ測定し、平行移動、回転、スケール変化、残渣誤差を分析する。ボンディング精度の評価と改善が求められる。

これらの課題に対し、TELはデジタルツイン技術を活用した仮想環境での最適化を推進している。上下ウェーハの弾性変形、中央部にかかる圧力、ボンディング面の気圧や摩擦、ウェーハの剥離動作などを詳細に再現し、試作回数の削減と開発期間の短縮に大きく貢献している。

すべては半導体の技術革新に貢献するために

3DI技術は、AIをはじめとする高度な応用を実現するために不可欠な要素だ。その普及には、高度な技術開発と、装置メーカーと半導体メーカーとの緊密な連携が求められる。TELは広い装置ポートフォリオと独自の統合学習プラットフォームを活用し、物理モデルに基づくデジタルツインで開発効率を飛躍的に向上させるとともに、半導体業界の新たなニーズに応える装置開発を加速している。今後もTELは、未来の半導体産業を支える3DI技術のさらなる拡大を支援するキープレイヤーとして、挑戦を続けていく。

セッションでの発表者の様子