深さ10 µm, 400層を超える3D NAND Flash向けに超高速かつ地球温暖化係数84%減を実現したメモリチャネルホールエッチング技術を開発

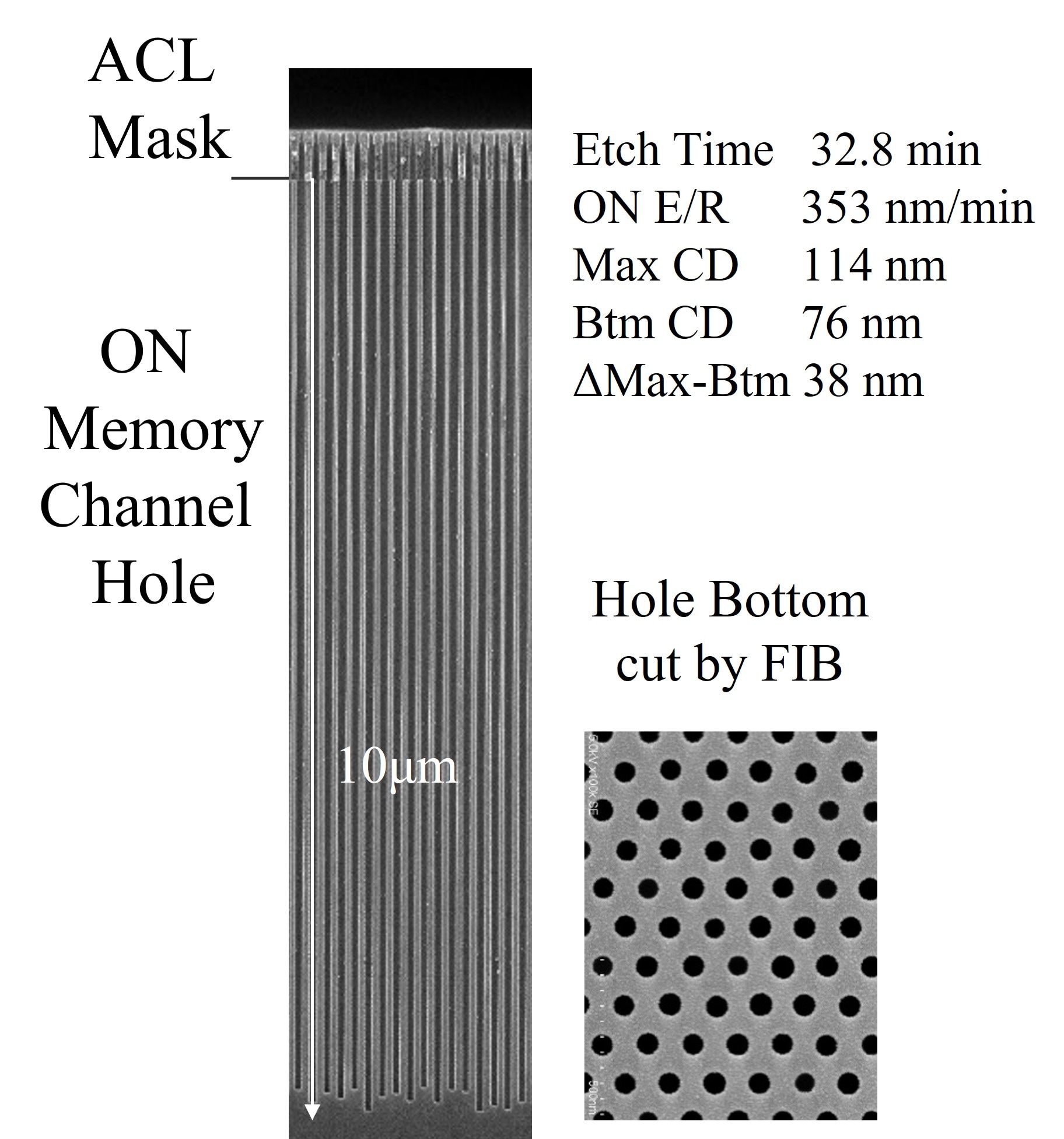

東京エレクトロン (TEL、東京都港区、社長:河合利樹)のプラズマエッチング装置の開発・製造拠点である東京エレクトロン宮城の開発チームは、積層化が進む3D NANDにおいて、400層を超える積層構造にメモリチャネルホールを形成する、新しいエッチング技術を開発しました。これまで絶縁膜エッチングでは実用化されていなかった極低温領域において、絶縁膜のエッチング速度を格段に上げる新たなプロセスを開発し、対応装置を実現しました。この新技術は、高アスペクト比*の10 µmのエッチング深さを、33分という短時間で加工することが可能となるだけでなく、地球温暖化係数を従来比で84%削減できる画期的な技術です。図1に示す通り、非常に優れた形状を実現しています。本技術は、さらなる大容量3D NAND Flashの技術革新に貢献します。

図1. ホールパターンの断面SEM写真と、ホール底部のFIBカット写真

図2. 3D NAND Flash

当社の開発チームは、本技術の研究成果を、2023年6月11日から16日に京都で開催される半導体研究における最高峰の国際会議のひとつ、2023 Symposium on VLSI Technology and Circuitsにて報告します。半導体の技術革新と地球環境保全に貢献する当社の技術発表にぜひご期待ください。

当社はこれからもBest Products、Best Technical Serviceを常に追求し、半導体の技術革新に貢献し続けます。そして、今年、創立60周年を迎えるいま、この節目を「新たな変革点」と位置づけ、さらなる挑戦と進化を続け、夢のある社会の発展に貢献してまいります。

*アスペクト比:ウェーハ上に形成されたパターンの深さと幅の比

論文情報

深さ10 µm, 400層を超える3D NAND Flash向けに超高速かつ地球温暖化係数84%減を実現したメモリチャネルホールエッチング技術

Y. Kihara, M. Tomura, W. Sakamoto, M. Honda and M. Kojima,

Tokyo Electron Miyagi Ltd.

セッション、発表日時:

Technology Session 3, NAND Flash [Shunju II]

6月13日(火)14:00-15:40

詳しいイベント情報はこちら: 2023 Symposium on VLSI Technology and Circuits

図1の写真を含む発表論文の著作権は、日本応用物理学会に帰属します。利用を希望される場合は、2023 Symposium on VLSI Technology and Circuits事務局までお問い合わせください。

VLSI Secretariat

Japan and Asia

vlsisymp@jtbcom.co.jp