分業化はさらに進む

この先、半導体産業の水平分業化はますます進む。例えば、設計だけでも、企画設計会社、デザインハウス、IPベンダーというように分かれてきている。いわゆるファブレスといわれる企業はICチップの機能やテクノロジーなどを定義し、自社ブランドの製品として企画設計のみをおこなう。デザインハウスは企画設計会社やシステム会社から定義されたICチップの機能や性能を実現するために、後述するRTL出力までプログラムしたりする。IPベンダーはICチップ上の特徴的な回路ブロックだけを設計し、ライセンス供与する。今では、プログラミングや回路が期待通り動くかどうか検証するためのサービスを行う企業や、テストだけを受け持つ企業などが出てきている。分業化はこの先もますます進むと考えられる。

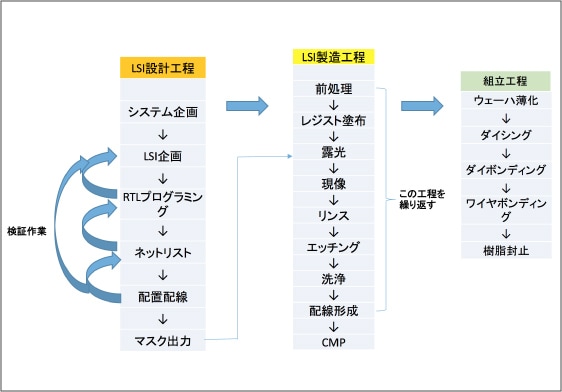

その根拠は、半導体ICの設計・製造工程が、この先もますます複雑になるからだ。製造工程は常に行ったり来たりするため、ベルトコンベア方式には乗らない。工程は、設計、前工程製造、後工程製造、と三つに大別できるが(図2)、いずれもその複雑さが増している。

|

設計工程では、まずシステムがどのような機能から出来ているのか企画立案し、それをハードウエアあるいはソフトウエアで実現する要件を決める。ICとなるハードウエアを設計するには、まずソフトウエアのプログラミングと同じようにICの機能を特殊な言語(VHLと呼ばれる)で記述していく。プログラムの入力ミスはつきものであるから、プログラム終了後にはバグのチェックを行い、デバグ作業でミスを取り除かなくてはならない。プログラムが正しく書けたら、次は機能を記述したプログラムの出力RTL(register transfer level:IC回路専用のプログラム出力形式)から、機能を実現するための回路間の結びつきを示すネットリスト(回路図)へ書き直す。ここでも回路が正しく接続されているかどうかのチェックをする。

回路図が正しく描かれていればと、それをレイアウトし、トランジスタのパターンを描く配置・配線を行う。配置・配線工程はトランジスタが正確に描かれているだけではなく、要求性能を満たしているかどうかもチェックする。配線の長さができるだけ等しくなるようにレイアウトや配線の回し方を工夫する。配線の長さがバラバラだと、信号が決まった時間内に届く回路と届かない回路が存在し、ICとして正しく動作しなくなる。最終的に出来上がった回路パターンの電子ファイルからフォトマスク(回路を上に転写する際に用いられる回路原版)を作製し、それを前工程に渡す。