Expert Interviewエキスパートインタビュー

── チップ化の次は何を進化させますか。

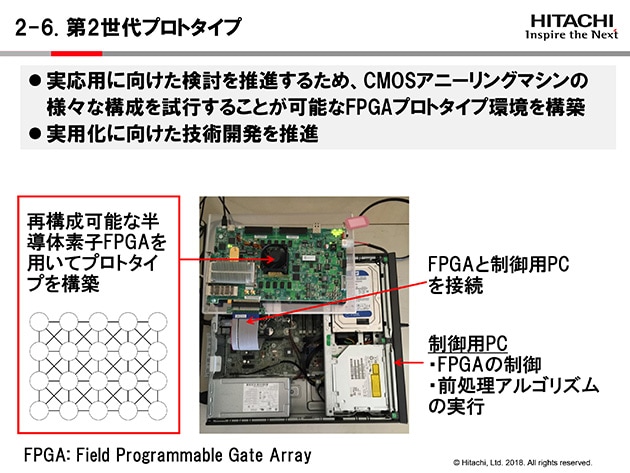

このチップは第1世代のLSI(大規模集積回路)ですが、実応用に向けて第2世代(図5)、第3世代の試作チップを作るため、それぞれFPGA*6で組み込みました。FPGAを使ったのは、これからもっと効率の高いアルゴリズムが生まれてきたときに簡単にソフトウエアで取り込めるようにするためです。

|

最初のCMOSアニーリングマシンはASIC*7なので、イジングモデルの構成が固定されています。イジングモデルはスピン間の結合がどうつながっているか、結合の強さはどうか、などまだ工夫の余地はあります。ASICにしてしまうと、固定してしまうので、第2世代ではFPGAでいつでも変えられるようにしておくことも必要です。ですから最初のチップを試作したことによって、どの程度の効果があることがわかったので、次はチップを固定せずFPGAボードを新しいアルゴリズムやパラメータを変えられるようにしておきます。

── 第3世代のFPGAモデルはどのようになりますか。

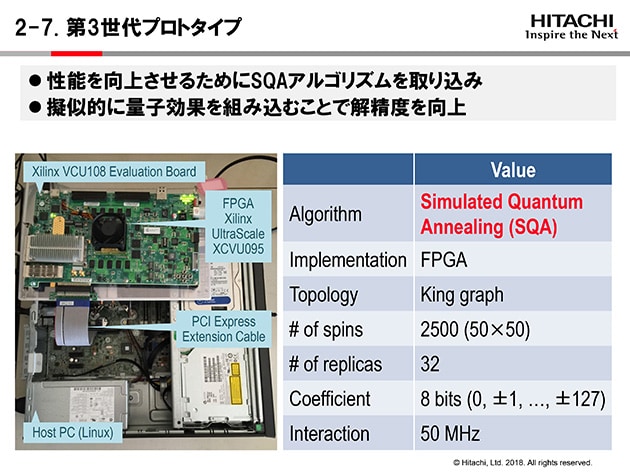

さらに第3世代(図6)では、アニーリングそのものを、SQA(Simulated Quantum Annealing)法*8に変えています。このアニーリング法のコンセプトは10年ほど前に登場したもので、2016年にGoogle社がソフト的に量子効果を取り込めることを学会で発表しました。そこで、当社はこれをハードウエアに取り込んで精度を上げようと考えました。ここではFPGAで試しています。

|

簡単に言えば、イジングモデルのレプリカ(コピー)を複数個作り、それぞれで計算させるのですが、最終的には一つに収束していくような動作をさせるという考えです。これによって量子効果の重ね合わせ原理を再現します。本当の量子効果では無限に重ね合わせることができるのですが、我々は今のところ32層あるいは64層程度の重ね合わせを実現しています。この重ね合わせを利用することで精度を上げることが可能です。

実際に32層の重ね合わせ効果を再現すると、従来のシミュレーテッドアニーリング法と比べて、15倍あるいは40倍も高速に最適化問題を実行できることがわかりました。

── 各層をCMOS技術ではどのように表現されるのでしょうか。

各層はCMOSのSRAMメモリとして表現しているので、もう少し大規模なSRAMを作り、層1をSRAM内のメモリブロック1に、層2を同メモリブロック2へと対応させることで実現できます。このとき、接続状態は各層とも同じです。ただし、スピンの値だけが違うので、SRAMをそのまま大規模にしなくても済むようになります。

── 実用化に向けての課題は何ですか。

ハードウエアの基本構成はできたのですが、これを実用化する場合にはソフトウエアを組み込むことが重要で、今それを開発しているところです。そのソフトウエアの例を挙げましょう。もともとのイジングモデルのスピンは複雑なつながりを持っているのですが、アニーリングマシンは規則的な構造を持っています。そこで、複雑なつながりを規則的な形の上に再現するという変換ソフトウエアを開発しています。そうすると、ハードウエアがシンプルになるため、高速で解きやすくなるんです。こうしたソフトウエアの開発により、この技術の実用化を進めています。

── このCMOS方式の問題点、あるいは量子効果の問題点は何でしょうか。

量子を含めた問題として、この技術は新しいのでそれに合わせたソフトウエアの開発や、どこに使うのかといった応用上の問題があります。これはCMOS型でも量子型でも同様で、ソフト開発は非常に重要な問題だととらえています。これは我々だけではなく、国内外の研究者も同様にソフトウエアの開発が重要だとして取り組んでいます。

CMOSの課題は、量子コンピュータに比べると精度が劣るところです。同じ時間で計算するなら、CMOSの方が精度は劣りますし、同じ精度を求めようとしたら、CMOSの方が時間はかかります。ただし、この問題を解決するには、疑似量子効果のようにアルゴリズムを改良して精度を上げる方法があります。

もう一つの課題として、実際に使う場合にどこまでの精度が必要なのか、ということを見極める技術が求められます。これは、実際のアプリケーションとして必要な精度を、工学的見地から見極めるということです。必要以上に精度を上げても意味がありませんから。

例えば、組合せ最適化問題において、素因数分解は暗号を解くのに使われますから、精度が優先されるため量子コンピュータが必要でしょう。素因数分解がすべての数字でできれば暗号を解くことができると言われています。

一方、応用によっては、最適化に近ければよいという場合もあるでしょう。例えば、ポートフォリオの最適化の場合は、世の中の動きによって求める条件が変わります。その時点で最適な条件が求められるので、解は最適に近ければよいということになるでしょう。こういった場合はCMOSの方が有利です。

── AIスピーカーに使われている音声認識や文字認識も、精度よりはむしろ最適に近い方が重要ですね。

そう思います。これらはある程度の認識をした後に、探している分野に近い言葉に補正して答えに近づけます。そのため、認識精度の厳密性は求められません。

精度の他にもう一つ、規模も必要になります。同じ規模を同じ時間で計算する場合に、どちらが有利かを見極める必要があります。

その効率を高めるために、量子コンピュータも頑張っていると思います。つまり、どちらかだけが必要という訳ではなく、CMOSも量子型もどちらにも長所があり、用途によって両者を使い分けることが応用を広げていくことにつながるでしょう。

[ 脚注 ]

- *6

- FPGA:Field Programmable Gate Arrayの略で、ユーザーの手元で異なる論理回路に変えることのできるプログラム可能なデジタル論理回路

- *7

- ASIC:Application Specific Integrated Circuitの略で、専用の集積回路のこと。独自の回路なので作ったら最後、設計を変更することはできないし、その特定用途以外に使えない。

- *8

- SQA(Simulated Quantum Annealing)法:解の候補の量子力学的な重ね合わせの時間変化を表すシュレーディンガー方程式を解いていく、量子アニーリングをシミュレーションすること。